Zastosowanie technologii - boundary scan - w testerach Seica

| Prezentacje firmowe ArtykułyPostęp technologiczny w elektronice stawia nowe wymagania przed technikami kontroli układów elektronicznych. Dziedziną, której najczęściej to dotyczy, jest montaż elektroniczny, co wynika z procesów miniaturyzacji płytek drukowanych, powszechnego montażu dwustronnego, zastosowaniu obudów BGA no i oczywiście obecności procesorów sterujących. Coraz częściej ze względu na dużą gęstość ułożenia elementów, kontrola połączeń za pomocą igieł dotykowych nie jest możliwa. Z pomocą przychodzi skanowanie typu boundary scan, które pozwala na dostęp do ukrytych miejsc i przeprowadzenie testów nawet najbardziej złożonych płytek drukowanych, jak również na usuwanie problemów, programowanie wewnątrz systemu i diagnozowanie problemów sprzętowych.

Wszystko to dlatego, że boundary scan umożliwia szczegółowy dostęp do nawet najbardziej „zatłoczonych” układów - zupełnie niezależnie do metod technologii układania elementów.

Wszystko to dlatego, że boundary scan umożliwia szczegółowy dostęp do nawet najbardziej „zatłoczonych” układów - zupełnie niezależnie do metod technologii układania elementów.

Pośród wielu metod testowania, kontrola montażu za pomocą sond testowych flying probe jest bardzo efektywnym rozwiązaniem do testów prototypów, podczas wdrażania nowych produktów i produkcji nieseryjnej, z dużym naciskiem na kontrolę montażu obwodów cyfrowych i analogowych. Ponadto tester flying probe nie wymaga dodatkowych inwestycji w kompleksowe budowanie drogich fixtur testowych i zapewnia sporą elastyczność, która przydaje się podczas częstych zmian w projekcie. Natomiast w przypadku produkcji seryjnej, do testowania dopracowanych produktów, proponuje się rozwiązania oparte o sondy igłowe, znane jako bed of nails, które gwarantują wysoką wydajność testów.

Korzyści płynące z korzystania z metody boundary scan i systemów testowych (zarówno flying probe jak i bed of nails) wzrastają z powodu niskich kosztów związanych z ich wykorzystaniem oraz olbrzymiej efektywności w przypadku analogowych części obwodów. To dlatego, że system boundary scan rozwinął się, jako idealna metoda kontroli układów, zwłaszcza tych zawierających komponenty BGA. Połączenie go razem z testerami automatycznymi daje komplementarne rozwiązanie, którym możemy się posłużyć w przypadku testów projektów o złożonej budowie.

Boundary scan zmniejsza także margines błędu na przykład poprzez umożliwienie testowanie połączeń układu BGA z niedostępnymi z zewnątrz połączeniami wewnątrz płytki.

Co to jest boundary scan?

Boundary scan (skanowanie ze ścieżką krawędziową) jest najprawdopodobniej jedną z najlepszych istniejących technik testowania układów elektronicznych. Zasada działania jest podobna do techniki testującej In-Circuit Board Tester (ICT) z tą różnicą, że w przypadku boundary scan nie ma fizycznego kontaktu z wyprowadzeniami na PCB. Różnica ta stanowi o jej wyższości względem innych metod testujących.

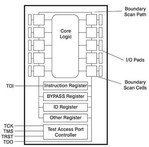

Za pomocą boundary scan można wykryć i zlokalizować błędy w połączeniach i wykonać tysiące testów punktowych niezależnie od typu użytych obudów i liczby warstw na płytce. Główna jednostka boundary scan zawarta w układach scalonych obsługujących omawiane metody testowania zbudowana jest z rdzenia logicznego (Core Logic) oraz z komórek (Boundary Scan Cell).

Komórki są zintegrowane pomiędzy głównym rdzeniem układu a zewnętrznymi pinami. Wszystkie komórki połączone są w szeregowy rejestr przesuwny z równoległymi wejściami i wyjściami. W każdym układzie zaimplementowana jest także jednostka kontrolna (Test Access Port), która ma za zadanie pobudzać stany na wyprowadzeniach, a następnie odczytywać odpowiedzi.

|

| Rys. 1. Schemat struktury łańcucha Boundary Scan |

Cały układ sterowany jest przez cztery linie sygnałowe. Za synchronizację pracy odpowiedzialna jest linia sygnałowa Test Clock (TCK). Wyjście Test Mode Select (TMS) służy do wyboru trybu pracy, gdzie jeden stan oznacza pracę w trybie testowania, a drugi w trybie normalnej pracy. Linie sygnałowe Test Data In (TDI) oraz Test Data Out (TDO) reprezentują odpowiednio dane wejściowe i wyjściowe w rejestrze przesuwnym.

Rezultatem zastosowania opisanej techniki jest ogromna redukcja punktów testowych na płytce, a to się przekłada na duże oszczędności: prostsze rozplanowanie układu płytki, mniej kosztowne instalacje testowe, oszczędność czasu przy testach in-circuit, zwiększone wykorzystanie standardowych interfejsów oraz poprzez przyspieszenie czasu testu.

Od strony oprogramowania, boundary scan daje możliwości konfigurowania prawie wszystkich typów CPLD oraz pamięci Flash, już po montażu PCB, niezależnie od złożoności płytki drukowanej. W efekcie otrzymujemy zmniejszenie nakładu pracy, liczby niezbędnych narzędzi do przeprogramowywania i zintegrowanie czynności niezbędnych do programowania płytek na linii produkcyjnej.

Rozwiązanie proponowane na przykładzie testerów Seica

Firma Seica korzysta z boundary scan we wszystkich systemach testujacych flying probe i bed of nails. System kontrolny osprzętu boundary-scan jest zamocowany w gnieździe PCI komputera, który jest podłączony do generatora za pomocą łącza SCSI. Cyfrowy skaner I/O łączy je z wejściami testera Seica, aby sygnały zostały zaaplikowane do badanego urządzenia.

Ze skanerem cyfrowym I/O jest możliwe stosowanie łańcucha boundary scan w sieci (po jednym na każdy punkt sygnałowy) w pojedynczym obwodzie testowym. Od strony oprogramowania tester bazuje na dynamicznych bibliotekach, pozwalających na automatyczne generowanie programów testowych za pomocą autorskiego języka programowania Seica. Programy testowe są tworzone na bazie funkcjonalnego środowiska testowego.

Daniel Trzciński, PB Technik