FPGA od początku do końca - część pierwsza

| TechnikaSzybki rozwój rynku FPGA, którego wartość oceniania jest obecnie ponad 2 mld dol., a także coraz częstsze stosowanie układów programowalnych w aplikacjach dotąd zdominowanych przez ASIC są dobrymi argumentami do podejmowania tego tematu w kolejnych artykułach. Jednakże nie wszyscy zainteresowani FPGA są dobrze zorientowani w podstawowych kwestiach, jakie wiążą się z mnogością typów dostępnych układów. Niniejszy tekst ma na celu zebranie i krótki opis budowy, cech i podstawowych możliwości układów programowalnych. Różnorodność aplikacji, w jakich stosowane są układy programowalne jest zdumiewająca. Stale rośnie także liczba produkowanych systemów, których elementem jest układ FPGA. Bezpośrednim odzwierciedleniem tych trendów na rynku są dane statystyczne dotyczące wartości sprzedawanych w kolejnych latach układów FPGA. Jak podaje firma In-Stat, do 2010 roku kwota ta powinna przekroczyć 2,75 mld dol. rocznie i nadal rosnąć w tym samym tempie. Głównymi zastosowaniami FPGA są systemy komunikacji, zarówno tej na duże odległości, jak i wewnątrz systemowej, odbywającej się w ramach kilku współpracujących ze sobą urządzeń. Oczywiście, układy FPGA są obecne także w wielu innych dziedzinach elektroniki, gdzie z powodzeniem zastępują mało skomplikowane sieci układów logicznych, albo też wykonują proste obliczenia na bardzo dużych ilościach danych.

Ta różnorodność zastosowań sprawia, że tak jak wśród mikrokontrolerów, na rynku dostępnych jest bardzo wiele różnych układów programowalnych, dostosowanych możliwościami i ceną do wymagań stawianych przez poszczególne segmenty rynku.

Jak wybierać?

Dobór układu FPGA do zastosowania powinien być starannie przeprowadzony, aby cały system miał szanse na optymalne funkcjonowanie. Wybór ten jest nieco trudniejszy niż w przypadku selekcji mikrokontrolera do sterownika, gdyż liczba parametrów wybieranego układu jest większa. Co więcej, problematyczne może być określenie wymaganej pojemności układu, od której zależy liczba operacji, jakie mogą być wykonywane naraz przez system. Wielkość ta podawana jest przez producentów w postaci wielu różnych parametrów, pomiędzy którymi nie istnieje stały i zawsze obiektywny przelicznik. Niekiedy rozwiązaniem może być zastosowanie narzędzi dostępnych w zintegrowanych pakietach dla projektantów, które oferowane są przez producentów FPGA. Dzięki tym programom możliwe jest nie tylko dokładne określenie liczby podstawowych komórek układu, jakie będą konieczne do implementacji danej funkcjonalności w konkretnym układzie, ale także i pobór mocy, którym charakteryzować się będzie gotowe urządzenie. Niestety, dane te będą tym bardziej precyzyjne im więcej informacji na temat projektowanego systemu zostanie wprowadzonych do środowiska projektowego. Niekiedy oznacza to, że aby wyliczyć wszystkie wymagania, którymi kierować się będziemy podczas finalnego wyboru układu, konieczne jest wcześniejsze napisanie praktycznie całego kodu, w odpowiednim języku opisu sprzętu. Ponieważ, ze względu na szerokie oferty prawie wszystkich producentów FPGA, warto pozostawić sobie wybór wytwórcy układu na koniec i móc rozważać wszystkie z podzespołów oferowanych na rynku. Aby to w ogóle było możliwe, stosowany podczas programowania język opisu sprzętu powinien być na tyle uniwersalny, by zapisany kod mógł być wykorzystany do zaprogramowania układów dowolnego producenta. Przykładem takiego języka będzie chyba najbardziej popularny VHDL - Very High Speed Integrated Circuits Hardware Description Language. Równie interesującym może okazać się Verilog, uznawany przez wielu specjalistów jako znacznie bardziej czytelny i klarowny sposób opisu pracy układów.

Dobór układu FPGA do zastosowania powinien być starannie przeprowadzony, aby cały system miał szanse na optymalne funkcjonowanie. Wybór ten jest nieco trudniejszy niż w przypadku selekcji mikrokontrolera do sterownika, gdyż liczba parametrów wybieranego układu jest większa. Co więcej, problematyczne może być określenie wymaganej pojemności układu, od której zależy liczba operacji, jakie mogą być wykonywane naraz przez system. Wielkość ta podawana jest przez producentów w postaci wielu różnych parametrów, pomiędzy którymi nie istnieje stały i zawsze obiektywny przelicznik. Niekiedy rozwiązaniem może być zastosowanie narzędzi dostępnych w zintegrowanych pakietach dla projektantów, które oferowane są przez producentów FPGA. Dzięki tym programom możliwe jest nie tylko dokładne określenie liczby podstawowych komórek układu, jakie będą konieczne do implementacji danej funkcjonalności w konkretnym układzie, ale także i pobór mocy, którym charakteryzować się będzie gotowe urządzenie. Niestety, dane te będą tym bardziej precyzyjne im więcej informacji na temat projektowanego systemu zostanie wprowadzonych do środowiska projektowego. Niekiedy oznacza to, że aby wyliczyć wszystkie wymagania, którymi kierować się będziemy podczas finalnego wyboru układu, konieczne jest wcześniejsze napisanie praktycznie całego kodu, w odpowiednim języku opisu sprzętu. Ponieważ, ze względu na szerokie oferty prawie wszystkich producentów FPGA, warto pozostawić sobie wybór wytwórcy układu na koniec i móc rozważać wszystkie z podzespołów oferowanych na rynku. Aby to w ogóle było możliwe, stosowany podczas programowania język opisu sprzętu powinien być na tyle uniwersalny, by zapisany kod mógł być wykorzystany do zaprogramowania układów dowolnego producenta. Przykładem takiego języka będzie chyba najbardziej popularny VHDL - Very High Speed Integrated Circuits Hardware Description Language. Równie interesującym może okazać się Verilog, uznawany przez wielu specjalistów jako znacznie bardziej czytelny i klarowny sposób opisu pracy układów.

Tymczasem pierwszym krokiem dotyczącym wyboru sprzętu powinno być określenie docelowego typu układu programowalnego, czyli wybór pomiędzy układami typu antifuse, Flash, SRAM i FLASH-SRAM.

Układy typu antifuse

Pierwsza konstrukcja pozwala na jednorazowe programowanie techniką, określana mianem antifuse, której znaczenie sprowadza się do implementacji we wnętrzu układu milionów scalonych bezpieczników. Bezpieczniki te działają odwrotnie niż normalne bezpieczniki elektroniczne, tj. przewodzą dopiero po ich przepaleniu. To właśnie w wyniku nieodwracalnego procesu termicznego, zapisane w tych FPGA dane nie podlegają zmianie, toteż niemożliwa jest ponowna rekonfiguracja raz zaprogramowanego układu.

Ponadto ze względu na swoją konstrukcję są to najbezpieczniejsze systemy, gdyż wszelkie próby reverse engineering, mające na celu odczytanie konfiguracji takiego układu kończą się niepowodzeniem. Wynika to z faktu, że dane na temat wewnętrznej konfiguracji nie są przenoszone poza sam układ, a stosowane czasami metody polegające na usuwaniu kolejnych warstw półprzewodnika i fotografowaniu jego przekroju tworzą obraz milionów identycznych bezpieczników, wśród których rozróżnienie tych przepalonych, od nieprzewodzących jest praktycznie niemożliwe.

Ponadto ze względu na swoją konstrukcję są to najbezpieczniejsze systemy, gdyż wszelkie próby reverse engineering, mające na celu odczytanie konfiguracji takiego układu kończą się niepowodzeniem. Wynika to z faktu, że dane na temat wewnętrznej konfiguracji nie są przenoszone poza sam układ, a stosowane czasami metody polegające na usuwaniu kolejnych warstw półprzewodnika i fotografowaniu jego przekroju tworzą obraz milionów identycznych bezpieczników, wśród których rozróżnienie tych przepalonych, od nieprzewodzących jest praktycznie niemożliwe.

Należy jednak zaznaczyć, że układy typu antifuse domyślnie pozwalają na odczyt zapisanej konfiguracji, aby umożliwić testowanie poprawności przebiegu procesu programowania. Dopiero po ustawieniu specjalnego bitu zabezpieczającego, dostęp do wewnętrznej konfiguracji jest nieodwracalnie blokowany.

Urządzenia oparte o technikę przepalania charakteryzują się szeregiem zalet, jakich nie mają inne typy FPGA. Brak wewnętrznych tranzystorów odpowiadających za konfigurację sprawia, że układy te są znacznie mniej podatne na uszkodzenia spowodowane promieniowaniem. Predestynuje je to do roli układów przetwarzania sygnałów w zastosowaniach w lotnictwie i aeronautyce, gdzie FPGA oparte o pamięci SRAM lub Flash byłyby zbyt zawodne. Ponieważ jednak w układach tych występują także różnego rodzaju przerzutniki, których stan może zostać zmieniony pod wpływem promieniowania, stosuje się takie techniki jak dodatkowe, silne kody korekcyjne i potrójne redundantne układy głosujące. Zwiększają one prawdopodobieństwo poprawnego działania systemu w czasie zaplanowanej misji.

Nie można też pominąć faktu, że układy antifuse, ze względu na brak tranzystorów konfigurujących zużywają znacznie mniej mocy statycznej w stosunku do wyprodukowanych w tej samej technologii układów SRAM lub Flash. Wartość ta wynosi około 20% mocy, którą pobiera układ reprogramowalny. Co więcej, brak tranzystorów to także brak wprowadzanych przez nie opóźnień, dzięki czemu cały system jest w stanie działać wyraźnie szybciej. Ostatecznie, jako że połączenia wykonane w postaci stopionych ze sobą metalizacji zajmują znacznie mniej powierzchni półprzewodnika, niż tranzystory wraz z ich otoczeniem, układy wykonane w technologii antifuse zajmują znacznie mniej miejsca niż odpowiadające im układy SRAM i Flash.

Wszystkie powyższe argumenty byłyby świetnym powodem do wyboru układów trwale programowalnych, zawsze gdy tylko jest to możliwe, gdyby nie jeden mały, ale bardzo istotny problem. Mianowicie wykonanie układu w technologii antifuse wymaga przeprowadzenia trzech dodatkowych procesów technologicznych, co znacząco wpływa na ograniczenia precyzji, z jaką projektowane mogą być te układy. Efektem jest konieczność posługiwania się przynajmniej o generację starszą, a niejednokrotnie i o kilka stopni mniej zaawansowany proces technologiczny, w wyniku czego wszystkie opisane dotąd przewagi antifuse FPGA nad SRAM i Flash FPGA tracą na znaczeniu.

Ostatecznie, układy jednokrotnie programowalne niezbyt nadają się do produkcji prototypów i nie pozwalają na wprowadzanie usprawnień do gotowych urządzeń, poprzez funkcję aktualizacji firmware.

FPGA na pamięciach statycznych

Drugim z podstawowych typów technologii, w jakim wykonywane są układy FPGA jest wykorzystanie pamięci statycznych SRAM. Podstawową różnicą w stosunku do wcześniej opisanych antifuse jest możliwość ich wielokrotnego programowania, co pozwala na przykład na stosowanie aktualizacji firmware. Ponadto układy te bazują na pomysłach opracowanych przy produkcji nowoczesnych pamięci wykonanych w technologii CMOS, dzięki czemu mogą wykorzystywać najnowsze osiągnięcia technologiczne w tej dziedzinie. Nie wymagają one żadnych dodatkowych procesów technologicznych, a więc układy te najczęściej projektowane są w oparciu o najbardziej zaawansowane technologie z najmniejszym wymiarem charakterystycznym. Dzięki temu dorównują mniej zaawansowanym pod tym względem układom antifuse i omówionym w dalszej części Flash FPGA.

Niestety, ponieważ pamięci SRAM są z natury rzeczy ulotne, konieczne jest ładowanie kodu konfiguracyjnego do wnętrza układu podczas każdego uruchamiania systemu. Odbywa się to zazwyczaj poprzez wprowadzenie tych danych ze zlokalizowanego w pobliżu układu pamięci trwałej, takiej jak EPROM lub Flash. To dodatkowe wymaganie sprawia, że konieczne jest zarezerwowanie większej ilości miejsca na powierzchni płytki drukowanej, którego przeznaczeniem będzie lokalizacja dodatkowej pamięci i połączeń pomiędzy nią a układem programowalnym.

Sam proces wgrywania programu także nie jest pozbawiony wad. Każdorazowo wymaga on trochę czasu, przez co start urządzenia jest zawsze opóźniony. Dane te mogą być bez problemu przechwycone, co sprawia, że zapisany za ich pomocą projekt jest łatwy do zdekodowania i powielenia na innych urządzeniach. Aby to uniemożliwić, producenci SRAM FPGA wprowadzili dodatkową możliwość szyfrowania przesyłanych danych. Producent szyfruje zawartość kodu programującego zapisanego w zewnętrznej pamięci i wgrywa odpowiedni klucz deszyfrujący do wnętrza układu. Oczywiście nie jest to takie proste, gdyż jak to zostało wcześniej napisane, SRAM FPGA nie jest w stanie przechowywać żadnej konfiguracji bez podtrzymywania zasilania. Dlatego też tak zabezpieczone układy muszą być wyposażone w dodatkowe źródło zasilania, najczęściej realizowane w postaci niewielkiej baterii. Jest to dobre rozwiązanie, gdyż ilość pamięci potrzebnej do przechowania klucza, która to musi być zasilana jest stosunkowo niewielka. Jednak konieczność umieszczenia dodatkowej baterii na płytce PCB, jeszcze bardziej powiększa jej rozmiary. Co więcej, w przypadku uszkodzenia baterii, przechowywany klucz deszyfrujący zostaje utracony i urządzenie staje się niesprawne. Mimo to stosowanie takich zabezpieczeń jest uznawane za rozsądne, gdyż nie tylko blokuje możliwość odczytu zapisanej konfiguracji, ale i nie pozwala na przekonfigurowanie systemu w taki sposób, by działał na szkodę użytkownika. Taka metoda ataku nazywana jest potocznie wprogramowywaniem trojańskich projektów i choć nie jest popularna, należy mieć na uwadze potencjalne szkody, jakie może wyrządzić.

W sytuacji, gdy producent nie może sobie pozwolić na umieszczenie dodatkowej baterii na płytce PCB, a wymaga zastosowania układu SRAM możliwe jest wykorzystanie jednego z niewielu dostępnych na rynku układów hybrydowych, w których klucz przechowywany jest w nieulotnych pamięciach Flash wewnątrz układu.

Flash FPGA

Trzecim typem układów programowalnych, także nieulotnych, ale pozwalających na wielokrotne programowanie są systemy oparte o technikę Flash. Łączą one niejako zalety poprzednio wymienionych typów układu, ale z racji zwiększonej trudności wykonania, mają także i swoje ograniczenia. Po pierwsze czas ich programowania jest kilkakrotnie dłuższy niż w przypadku układów SRAM. Nie występują natomiast opóźnienia podczas uruchomienia. Ich wewnętrzna konstrukcja jest nieco mniej skomplikowana niż w przypadku pamięci statycznych, toteż mogą być gęściej upakowane. Niestety, tak jak to było w przypadku antifuse FPGA, także i tu wymagana jest większa liczba zabiegów technologicznych – z tym, że zazwyczaj jest to 5 dodatkowych procesów. Sprawia to oczywiście, że układy te są najczęściej o kilka generacji starsze niż ich odpowiedniki produkowane w tym samym czasie, które wymagają jedynie użycia metod typowych dla CMOS. Kolejną wadą jest zwiększony pobór mocy statycznej, za co odpowiadają gęsto występujące we Flash FPGA rezystory podciągające.

Na koniec warto dodać, że także i układy oparte o pamięci Flash są zabezpieczone przed wprogramowaniem nieautoryzowanych projektów. Aby odczytać zawartość takiego FPGA lub wpisać nowe dane konieczne jest podanie przez interfejs JTAG poprawnego klucza. Ponieważ obecnie implementacje standardu JTAG pracują zazwyczaj z częstotliwością około 20MHz, czas potrzebny na przetestowanie wszystkich możliwych kluczy sięga miliardów lat.

Struktura logiczna

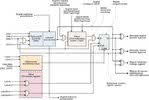

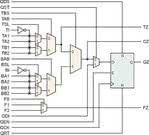

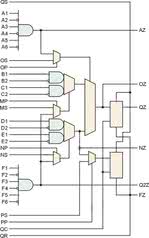

Niezależnie od fizycznej realizacji układu FPGA, tak czy inaczej jest on podzielony na bloki logiczne, których nazwy, rozmiary i forma zależne są od producenta i konkretnego układu. W uproszczeniu, każdy układ FPGA składa się z bloków logicznych, które to umieszczone są pomiędzy szynami danych, czy też ogólnie mówiąc - ścieżkami umożliwiającymi dokonanie odpowiednich połączeń pomiędzy poszczególnymi komórkami. Każda komórka ma kilka wejść i nieco mniej wyjść. Nie są to jednak linie sobie równoważne, gdyż większość z nich pełni specjalne funkcje a jedynie część z tych sygnałów może być argumentami funkcji logicznych lub przybierać wartości przez nie zwracane. Przykład implementacji elementu logicznego – gdyż tak została nazwana najmniejsza komórka układu Cyclone II, zilustrowany został na rysunku 3. W ramach tego schematu wyróżnić można typowy, czterowejściowy blok LUT z jednym wyjściem. Bloki takie jak ten pozwalają na realizację dowolnej funkcji logicznej wprowadzanych do nich sygnałów i mogą być zrealizowane na dwa różne sposoby.

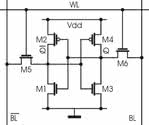

Najczęściej wykorzystywaną strukturą są matryce LUT (Look-Up Table). W rozwiązaniu tym sygnały wejściowe służą jako dane adresowe używane do odnalezienia odpowiedniej wartości wyjściowej zapisanej w 16-pozycyjnej macierzy. Wybieranie odpowiedniej komórki macierzy uzyskiwane jest często poprzez zastosowanie szeregu bramek transmisyjnych, tak jak to zostało przedstawione w uproszczeniu na rysunku 4. Drugą stosowaną metodą jest konstrukcja oparta o multipleksery. Stosowana jest w znacznie mniejszej liczbie układów, ze względu na trudności w uzyskaniu antycypacji przeniesienia, która przyspiesza pracę w sytuacji, gdy kilka elementów logicznych współpracuje ze sobą równocześnie. Niemniej są firmy, takie jak QuickLogic, które specjalizują się w produkcji układów opartych o struktury MUX, czy też mieszane MUX-LUT. Zaprojektowane w ten sposób fragmenty układów są odpowiednikami np. pojedynczej 4-wejściowej matrycy LUT, lub dwóch 3-wejściowych matryc LUT. Przykłady struktur opartych o multipleksery zostały zobrazowane na rysunkach 5 i 6.

Oprócz omówionych powyżej bloków, które realizują funkcje logiczne sygnałów danych, do komórek doprowadzane są linie sygnałów zegarowych i innych sygnałów sterujących takich jak output enable, clock enable lub reset. We wnętrzu takiej komórki znajduje się zazwyczaj także przerzutnik, który jest umieszczony tak, aby jego funkcja mogła zależeć od sposobu zaprogramowania układu.

Elementy łączą się w bloki

Opisane dotąd elementy logiczne łączone są w większe grupy nazywane w przypadku produktów Altery blokami logicznymi. Każdy taki blok składa się z szesnastu elementów logicznych, pomiędzy którymi przekazywane są sygnały przeniesienia, jak również wspólne zegary i niektóre sygnały sterujące. Bloki te mogą także służyć jako dodatkowa pamięć RAM, której komórki stanowią zintegrowane w elementach logicznych przerzutniki. Ponieważ typowa matryca LUT może zostać przekształcona w 16 bitów pamięci RAM, także i ona może być widziana jako dodatkowa pamięć układu – o ile tylko nie pełni żadnej innej funkcji logicznej. Ze względu na sposób realizacji tejże pamięci nazywa się ją często pamięcią rozproszoną w celu odróżnienia od skupionych bloków pamięci, jakie także mieszczą się wewnątrz układów FPGA. Ostatecznie ze względu na sygnały przeniesienia przekazywane pomiędzy sąsiadującymi komórkami, pamięci te mogą być traktowane jako rejestry przesuwne.

W tym momencie warto wspomnieć, że podobnie, aczkolwiek trochę inaczej zorganizowane są układy produkowane przez firmę Xilinx. To, co w przypadku układów Altery określane jest jako element logiczny, w produktach firmy Xilinx wygląda bardzo podobnie i nazywa się komórką logiczną. Tymczasem duża różnica występuje pomiędzy blokami logicznymi Altery, a ich odpowiednikami – kawałkami („plasterkami” - slice) logicznymi, które składają się jedynie z dwóch komórek logicznych. Jeszcze inaczej jest w najnowszych układach Virtex 5, firmy Xilinx, w których to 4 sześciowejściowe komórki logiczne stanowią jeden kawałek. Dalsza hierarchia w przypadku Altery sprowadza się do grupowania kilkunastu bloków logicznych, które następnie umieszczane są razem pomiędzy matrycami połączeń. Tymczasem firma Xilinx wprowadza jeszcze jeden poziom struktury, nazywany CLB, czyli konfigurowalne bloki logiczne, które składają się z dwóch lub czterech kawałków logicznych. Dopiero one umieszczane są pomiędzy siecią globalnych połączeń. Duża hierarchizacja została zastosowana w celu maksymalnej optymalizacji przesyłu danych na kolejnych poziomach struktury.

Warto dodać, że kolejne generacje układów wprowadzają coraz to bardziej skomplikowane struktury. Prawdopodobnie najbardziej skomplikowanym układem mogą poszczycić się obecnie projektanci z Altery, którzy byli twórcami układu Stratix III. Nie dość, że większość podstawowych elementów logicznych tego układu jest sześciowejściowa, to sąsiadują one z adaptacyjnymi modułami logicznymi, które to mogą być konfigurowane do pięciu różnych trybów pracy. Dla porównania, elementy logiczne układu Cyclone II mogą pracować tylko w dwóch trybach – normalnym i arytmetycznym.

Dodatkowe moduły

Układy FPGA zawierają także inne moduły, takie jak bloki pamięci, rdzenie specjalizowanych procesorów DSP lub jednostek arytmetycznych x86 czy też ARM, układy mnożące, sumatory, układy sterowania zegarem, pętle fazowe i zaawansowane układy wejścia oraz wyjścia. Opis tych i innych podsystemów zostanie opublikowany w następnym numerze Elektronika.

Marcin Karbowniczek