Ethernet w układach elektronicznych, część 2. Mikrokontrolery i układy programowalne

| TechnikaOferta rynkowa producentów układów scalonych, modułów i innych rozwiązań komunikacyjnych zapewniających komunikację za pomocą Ethernetu jest bardzo szeroka i dołączenie urządzenia do sieci i Internetu nie stanowi już większego problemu. Dostępne są specjalizowane kontrolery, układy realizujące warstwę fizyczną, gotowe biblioteki, stosy TCP/IP oraz mikrokontrolery mające wbudowane kontrolery MAC czy nawet pełną obsługę warstwy sprzętowej.

Niniejszy artykuł przedstawia najpopularniejsze metody dołączania do Ethernetu własnych urządzeń. W części pierwszej prezentowane były podstawowe informacje o standardzie i rozwiązania układowe gotowych konwerterów protokołów i modułów komunikacyjnych, w części drugiej omawiamy Ethernet w mikrokontrolerach i układach programowalnych oraz możliwości dostępnych bibliotek oprogramowania.

Ethernet w mikrokontrolerach

Znalezienie na rynku mikrokontrolerów zawierających zintegrowany kontroler Ethernetu obecnie nie nastręcza większych trudności. Najczęściej dostępna jest jedynie warstwa MAC, więc konieczne jest zastosowanie dodatkowego układu scalonego spełniającego funkcję warstwę fizycznej (PHY). Przykładem układów wyposażonych w warstwę MAC są STM32F107Vx z rodziny STM32 produkowanej przez STMicroelectronics.

Mają one 32-bitowy rdzeń ARM, do 256KB pamięci Flash oraz do 64KB wewnętrznej pamięci SRAM. Zasoby te pozwalają zmieścić w programie obsługę stosu TCP/IP oraz najważniejszych protokołów. Wykorzystanie kontrolera MAC nie odbiega zbytnio od korzystania ze zintegrowanych kontrolerów omówionych wcześniej. Pierwszym krokiem jest wyposażenie urządzenia w warstwę fizyczną (PHY) przez dodanie do projektu stosownego układu scalonego.

Komunikacja między mikrokontrolerem a układem realizującym warstwę fizyczną może się odbywać przez interfejsy MII (Media Independent Interface) lub RMII (Reduced Media Independent Interface). Wysyłanie danych sprowadza się do przygotowania ramki ethernetowej i umieszczenia jej w wewnętrznej pamięci SRAM. Do transmisji przeznaczony został specjalny bufor FIFO o rozmiarze 2KB, do którego dane trafiają z pamięci SRAM za pośrednictwem układu DMA. Stamtąd są przekazywane do modułu PHY i wprowadzane do sieci.

Kontroler warstwy MAC obecny w rodzinie STM32 cechuje się m.in.:

- obsługą transmisji z prędkością 10/100 Mb/s,

- pracą w trybie full-duplex (kontrola przepływu zgodna z IEEE 802.3x) oraz half-duplex (wsparcie dla protokołu CSMA/CD),

- automatycznym wstawianiem i usuwaniem preambuły oraz pola SFD,

- automatycznym obliczaniem sumy kontrolnej CRC.

Nadejście nowej ramki powoduje, że kontroler MAC usuwa z niej preambułę, pole SFD, oblicza sumę kontrolną i przesyła do bufora FIFO dane począwszy od adresu MAC. Możliwość sprzętowego filtrowania odbieranych pakietów pozwala z góry odrzucić niechciane ramki i ograniczyć generowany ruch. Podobne rozwiązania zostały zastosowane w układach rodziny AVR32. Atmel udostępnił sprzętową warstwę MAC umożliwiającą wysyłanie danych z prędkością 10 lub 100Mb/s.

Również w tym przypadku wymagane jest dołączenie zewnętrznego układu PHY. Wymiana danych pomiędzy warstwami MAC oraz PHY jest realizowana z użyciem interfejsu MII lub RMII zależnie od wyboru konstruktora. "Wygodni" konstruktorzy mogą wybrać mikrokontrolery zawierające zintegrowane obie warstwy: MAC oraz PHY. Pozwoli to zrezygnować ze stosowania dodatkowego elementu w projekcie. Wciąż potrzebne będzie gniazdo RJ45, które może mieć wbudowany transformator separujący, co jeszcze bardziej uprości konstrukcję całego urządzenia.

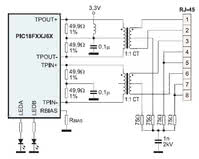

Przykładem mikrokontrolera mającego obie warstwy jest PIC18F97J60 produkowany przez Microchip. Jest on wyposażony w 128KB pamięci programu oraz 3,8kB pamięci RAM, a jego podstawowa, sieciowa aplikacji pokazana została na rysunku 1. Dodatkowe udogodnienie stanowi bufor o pojemności 8KB przeznaczony dla odbieranych i wysyłanych ramek.

Wśród możliwości oferowanych przez zintegrowany kontroler ethernetowy warto wymienić:

- programowalną retransmisję danych po stwierdzeniu kolizji,

- dodawanie bajtów wypełniających (gdy ramka ma za mały rozmiar) oraz generowanie sumy kontrolnej CRC,

- możliwość automatycznego odrzucania uszkodzonych pakietów,

- programowalne filtry pozwalające wyeliminować odbiór niepożądanych pakietów.

Konfigurowanie kontrolera, filtrów oraz dostęp do bufora zostało oparte o zespół rejestrów. Zintegrowany moduł DMA może zostać wykorzystany do kopiowania danych z jednego miejsca do drugiego w obrębie bufora danych oraz do wyznaczania sumy kontrolnej CRC wykorzystywanej przez różne protokoły komunikacyjne (np. TCP, UDP, IP).

Przesyłanie pakietów w mikrokontrolerach PIC18 jest zorganizowane podobnie jak w omówionym wcześniej układzie ENC28J60 i sprowadza się do umieszczenia w buforze pakietu, który ma zostać wysłany, ustawienia wskaźników początku oraz końca ramki i ustawienia odpowiedniego bitu w rejestrze, co wymusi rozpoczęcie transmisji. Dostępne są również mikrokontrolery z rdzeniem ARM zawierające zintegrowane warstwy MAC oraz PHY, czego przykładem mogą być układy z rodziny Stellaris produkowane przez Texas Instruments (np. LM3S9B81).

Producent udostępnił projektantom dwa bufory FIFO (nadawczy oraz odbiorczy) o rozmiarze 2KB pozwalające przechować po jednej pełnej ramce. W sytuacji, gdy ma ona mały rozmiar, do bufora można zapisać większą ich liczbę (do 31). Warto wspomnieć, że suma kontrolna może być wyliczana automatycznie lub zapisywana przez program.

W tym drugim przypadku świadome wysyłanie "uszkodzonych" pakietów pozwoli zbadać zachowanie pozostałych urządzeń pracujących w sieci na okoliczność błędów. Ramki o rozmiarze mniejszym, niż dopuszcza to standard, zostaną automatycznie uzupełnione o brakujące bajty. Zarządzanie pracą warstwy MAC oraz PHY odbywa się za pomocą zespołu rejestrów, natomiast wymiana danych między pamięcią RAM a buforem FIFO może być prowadzona z wykorzystaniem kontrolera μDMA.