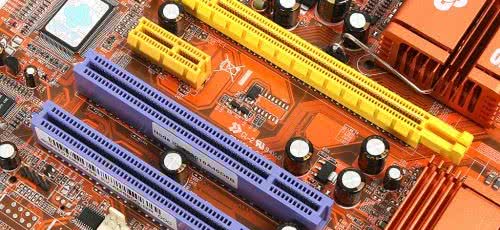

W kierunku PCI Express 3.0

| Gospodarka ArtykułyMagistrala PCI Express powoli, ale stale rozwija się, i powstają nowe urządzenia ją wykorzystujące. Na niedawnej konferencji PCI Special Interest Group (PCI SIG) zaprezentowano niektóre z nich. Podczas konferencji kilka firm zademonstrowało prototypowe rozwiązania oparte o interfejs PCI Express 2.0, który charakteryzuje się dwukrotnie większą przepustowością niż starsza wersja standardu. Firma Intel zapowiedziała, że pierwsze jej układy wykorzystujące PCI Express 2.0 trafią do sklepów przed końcem roku.

Ponadto członkowie PCI SIG zaprezentowali więcej szczegółów dotyczących pierwszych prac nad architekturą produktów najnowszej generacji, które mogą pojawić się pod koniec 2009 roku. Konsorcjum PCI SIG ogłosiło także, że osiągnięto postęp w pracach nad specyfikacjami dla wysoko wydajnych kart graficznych oraz wirtualizacji serwerów.

Do wymagających zastosowań

Obecnie ocenia się, że karty graficzne będą głównym kołem napędowym dla rozwoju magistrali PCI Express nowej generacji. Niedawno Intel zaprezentował chipset Stoakley, który współpracował z nowymi, jeszcze niedostępnymi na rynku układami graficznymi AMD i Nvidii. Stoakley przeznaczony jest do stacji roboczych i zawiera dwa 16-liniowe interfejsy PCI Express 2.0. Jednakże, według LSI Logic, także najnowsze 10-gigabitowe karty sieciowe będą również wykorzystywały interfejs PCI Express 2.0.

Zespół PCI SIG przeprowadza obecnie testy zgodności ze standardem 2.0 i zapowiada ich zakończenie przed warsztatami Plugfest, które odbędą się na początku grudnia w okolicach San José. Firmy mają nadzieję, że rozwiązania oparte o PCI Express 2.0 trafią na rynek już po tej konferencji.

Szczegóły techniczne

Istotnym elementem poprzedniej konferencji było omówienie kwestii standardu PCI Express w wersji 2.0. Firmy ARM, LSI Logic, NEC oraz Synopsys zademonstrowały interfejsy komunikacyjne umożliwiające wykonywanie do 5 mld przesłań na sekundę, a także Serdes (serializer/deserializer), którego maksymalna przepustowość wynosi 6,25Gb/s.

W celu osiągnięcia większej prędkości przesyłu danych, w PCI Express 2.0 zmniejszono o połowę dozwolone wahania długości cyklu zegara taktującego magistralę oraz obniżono impedancję ze 100 do 85. Długość pojedynczego złącza zmniejszona została z 12 do 6, a w niektórych przypadkach do 8 cali, natomiast implementacje dwuzłączowe będą wymagały linii paskowych zamiast ścieżek mikropaskowych.

Ponadto PCI SIG rozwija standard wspierający wysoko wydajne karty graficzne zużywające nawet do 300W mocy, podczas gdy obecne maksymalne zużycie wynosi 150W. Końcowa specyfikacja ma być gotowa pod koniec tego roku. Organizacja próbuje także stworzyć standard dla wirtualizacji poprzez magistralę PCI Express. Wraz z pojawieniem się procesorów wielordzeniowych perspektywa tworzenia w systemie wirtualnych partycji stała się jedną z głównych możliwości do wykorzystania w technice komputerowej. W marcu zespół ekspertów PCI SIG zakończył prace nad standardem dla tablicy adresowej będącej podstawową cechą specyfikacji. Standard dla wirtualizacji stosowanej w komputerach jednoprocesorowych powinien zostać ustanowiony na jesieni. Specyfikacja dla systemów wieloprocesorowych ma być gotowa przed końcem roku.

PCI Express 3.0

Konsorcjum PCI SIG pracuje nad kilkoma projektami, które w przyszłości pozwolą zdefiniować wersję 3.0 magistrali PCI Express - może to nastąpić już pod koniec 2009 roku. Inżynierowie wciąż rozważają możliwe warianty przepustowości magistrali - obecnie rozpatrywane są prędkości 8 lub 10 GT/s (miliardów przesłań). W tym samym czasie inny zespół roboczy pracuje nad zmianami w warstwie transakcyjnej dla magistrali PCI Express 3.0, które obniżą czasy opóźnienia o co najmniej 10%, przy jednoczesnym wzroście przepustowości złącza.

Także dwa inne zespoły inżynierów rozważają wprowadzenie poprawek do wersji 3.0. Jeden pracuje nad sposobami zmniejszenia przepustowości lub szerokości szyny urządzeń wykorzystujących magistralę PCI Express, co w dalszym ciągu pozwoli na ich wydajne funkcjonowanie. Natomiast druga grupa analizuje metody współpracy magistrali z systemami operacyjnymi i sterownikami urządzeń, aby polecenia złącza PCI Express były wykonywane bardziej efektywnie.

Grzegorz Michałowski