Ethernet w układach elektronicznych, część 2. Mikrokontrolery i układy programowalne

| TechnikaOferta rynkowa producentów układów scalonych, modułów i innych rozwiązań komunikacyjnych zapewniających komunikację za pomocą Ethernetu jest bardzo szeroka i dołączenie urządzenia do sieci i Internetu nie stanowi już większego problemu. Dostępne są specjalizowane kontrolery, układy realizujące warstwę fizyczną, gotowe biblioteki, stosy TCP/IP oraz mikrokontrolery mające wbudowane kontrolery MAC czy nawet pełną obsługę warstwy sprzętowej.

Ethernet w układach programowalnych

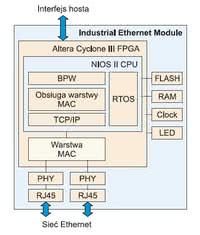

Rys. 2. Schemat blokowy przykładowej realizacji komunikacji sieciowej z wykorzystaniem układu Cyclone III oraz procesora NIOS II

Komunikacja sieciowa jest możliwa również z wykorzystaniem układów programowalnych (FPGA). Oprócz najbardziej intuicyjnego rozwiązania, jakim jest wykorzystanie zewnętrznego kontrolera Ethernet, można zastosować układy FPGA z wbudowanym kontrolerem warstwy MAC lub syntezowalny moduł opisany w języku HDL. W tym drugim przypadku można posiłkować się gotowymi rozwiązaniami lub kreatorami udostępnianymi przez producentów układów FPGA.

Synteza kontrolera MAC może nie być trywialna, jednakże takie podejście pozwala na prostą modyfikację kontrolera MAC i dostosowanie go do nowych standardów bez wprowadzania zmian sprzętowych. Wystarczy przygotować nowy opis, przeprowadzić jego syntezę i na nowo skonfigurować układ FPGA. Niezależnie od wybranego rozwiązania (synteza kontrolera MAC lub wykorzystanie zintegrowanego) niezbędne będzie użycie zewnętrznej warstwy PHY.

Obsługa stosu TCP/IP jest znacznie łatwiejsza za pomocą procesora i oprogramowania niż poprzez przygotowanie odpowiedniego opisu sprzętowego, więc powszechnym podejściem jest synteza rdzenia procesora i uruchamianie na nim oprogramowania. Jego zadaniem jest interpretowanie ramek otrzymanych z warstwy MAC oraz przygotowywanie pakietów, które następnie zostaną przesłane do sieci.

Procesor obsługuje także wyższe warstwy, takie jak TCP/IP, umożliwiając wygodną komunikację z innymi urządzeniami pracującymi w sieci. Na rysunku 2 przedstawiono schemat blokowy tak pracującego systemu. Rdzeń procesora przeznaczony do syntezy w FPGA najłatwiej pozyskać z oficjalnego źródła, jakim jest producent danego układu programowalnego. Na korzyść takiego rozwiązania przemawia duża optymalizacja rdzenia, co przekłada się na wyższą jego wydajność oraz wsparcie w postaci narzędzi do pisania oprogramowania dla danego procesora.

W Internecie dostępne są moduły IP (Intellectual Property) opracowywane przez niezależne jednostki i często udostępniane na zasadach licencji GPL/LGPL. Rozwiązania tego typu można znaleźć np. na stronie www.opencores.org, udostępnione są tam także kontrolery MAC.

Moc obliczeniowa wybranego procesora może być na tyle duża, że pozwoli to uruchomić system operacyjny pokroju Linux czy uC Linux, co jeszcze bardziej uprości komunikację przez sieć Ethernet. Warto zauważyć, że oficjalna dystrybucja jądra Linux zawiera wsparcie dla procesora Microblaze opracowanego przez firmę Xilinx. Tym samym stosunkowo niewielkim kosztem można uruchomić system operacyjny na układzie FPGA.

Listing 1. Szablon programu wykorzystującego stos TCP/IP firmy Microchip// Declare this file as main application file |

Komunikacja Wi-Fi (moduły, routery)

Realizacja bezprzewodowej komunikacji sieciowej z wykorzystaniem sieci WiFi nie musi być trudna, jeżeli wykorzystane zostaną zintegrowane moduły komunikacyjne. Przykładem takiego modułu jest MatchPort b/g produkowany przez firmę Lantronix (rys. 3). Jest to zintegrowane rozwiązanie zawierające 32-bitowy procesor ARM9, pamięć (do 64MB SDRAM i 256MB NAND Flash), nadajnik/odbiornik standardu 802.11b/g, Ethernet 10/100 Mbps, dwa porty szeregowe oraz port USB.

Wśród funkcji modułu warto wymienić wbudowany serwer web, pełną obsługę stosu TCP/IP, wysyłanie przez e-mail informacji o zdarzeniach oraz obsługę protokołów: ARP, UDP, TCP, ICMP, Telnet, AutoIP, DHCP, http czy SNMP. Komunikacja sieciowa może być zabezpieczona protokołami WEP, WPA lub 802.11i/WPA2-Personal. Moduł udostępnia interfejs szeregowy, przez który możliwa jest komunikacja projektowanego urządzenia z siecią Wi-Fi.

Innym przykładem układu do komunikacji przez sieć Wi-Fi jest moduł MRF24WB0MA produkowany przez firmę Microchip. Jest on zgodny ze standardem 802.11b/g/n i zapewnia komunikację z prędkością 1 oraz 2 Mbps w odległości do 400m. Zintegrowana antena oraz małe wymiary (21×31mm) umożliwiają łatwiejsze wbudowanie układu do własnego projektu.

Moduł podczas pracy musi być zasilany napięciem z zakresu od 2,7 do 3,6V, a typowy pobór prądu wynosi: 85mA (odbiór) oraz 154mA (nadawanie). Producent wyposażył produkt w sprzętową kontrolę dostępu do medium transmisyjnego (CSMA/CA), automatyczne wysyłanie potwierdzeń oraz sprawdzanie i dodawanie sumy kontrolnej. Warstwa MAC może ponadto samodzielnie retransmitować ramki, jeżeli zajdzie taka potrzeba.

Bezpieczeństwo transmisji zapewnia obsługa protokołów WEP, WPAPSK oraz WPA-2-PSK oraz zintegrowane, sprzętowe moduły szyfrujące zapewniające wsparcie dla algorytmów AES oraz RC4. Interfejs od strony mikrokontrolera stanowi port SPI, linia CS oraz dodatkowe linie sterujące (przerwanie, reset, stan hibernacji). Dla łatwiejszego debugowania dodane zostały porty JTAG i UART.

Z oczywistych względów moduł jest szczególnie polecany do współpracy z mikrokontrolerami PIC (PIC18, PIC24, dsPIC33 oraz PIC32). Współpraca z innymi rodzinami układów nie będzie łatwa do zrealizowania, gdyż znajdująca się na stronie produktu dokumentacja nie dostarcza opisu wewnętrznych rejestrów oraz sposobu konfiguracji modułu.

Zadanie to zostało powierzone bibliotekom opracowanym przez Microchip (Microchip Application Libraries, w skład której wchodzi także stos TCP/IP) dla mikrokontrolerów z rodziny PIC. Jest to rozwiązanie z jednej strony wygodne, gdyż moduł jest od początku tworzony z myślą o obsługiwaniu przez gotowe biblioteki, co pozwoli znacząco zaoszczędzić czas projektantów, jednakże z drugiej strony wymusza stosowanie mikrokontrolerów tylko jednej firmy, co nie zawsze jest rozwiązaniem korzystnym.

Dokumenty RFCDokumenty RFC (Request for Comments) są publikowane przez nieformalne, międzynarodowe stowarzyszenie IETF (Internet Engineering Task Force). Zawierają one definicje znaczącej części standardów oraz protokołów internetowych (np. TCP, IP, DHCP). Dokumenty te nie stanowią same w sobie standardu, ale z czasem część z nich jest przekształcana w oficjalne standardy sieciowe. Idea dokumentów RFC została zapoczątkowana w roku 1969 i od samego początku obowiązuje zasada, że raz opublikowany dokument nie jest później zmieniany. Wszelkie pomyłki koryguje się poprzez wydawanie poprawek, natomiast błędne rozwiązania są anulowane i w ich miejsce wydawany jest nowy dokument RFC. Takie podejście sprawiło, że powstała interesująca historia Internetu, którą można prześledzić, analizując kolejne zapisy na stronie IETF. Analiza taka pokaże, w jaki sposób następowała ewolucja sieci na przestrzeni kilkudziesięciu lat. Stowarzyszenie IETF ma charakter otwarty i nie ma osobowości prawnej. W strukturze organizacyjnej można wyróżnić m.in. grupy robocze mające własne grupy mailowe, do których mogą zapisywać się nowi członkowie. W ramach takiej grupy wypracowywane jest wspólne stanowisko w danej sprawie lub kilka różnych z zaznaczonym procentowym poparciem dla każdego z nich. Następnie stanowisko takie jest przekazywane do ciała decyzyjno- koordynującego IESG (Internet Engineering Steering Group), które może zatwierdzać lub odrzucać w drodze głosowania propozycję dokumentu RFC. |