Ładowanie systemu operacyjnego w urządzeniach wbudowanych

| TechnikaProcesor umieszczony w systemie wbudowanym musi wykonać wiele czynności po włączeniu zasilania, aby użytkownik miał możliwość uruchomienia aplikacji. Cała procedura, choć może się wydawać prosta z teoretycznego punktu widzenia, staje się złożona, gdy trzeba spojrzeć na nią okiem projektantów odpowiedzialnych za kwestie sprzętowe oraz programowe. Poziom komplikacji wzrasta jeszcze bardziej, gdy pod uwagę brane są różnorodne konfiguracje sprzętowe, na jakich system operacyjny będzie uruchamiany z możliwością wyboru kilku opcji, jakie pozostawia się zazwyczaj użytkownikowi.

Przykład stanowi system Windows, który jest uruchamiany na bardzo różnorodnym sprzęcie, pochodzącym od różnych producentów i wyprodukowanym na przestrzeni wielu lat. Użytkownik może ponadto wpływać na sposób ładowania systemu operacyjnego, wskazując choćby lokalizację właściwych plików: dysk twardy, napęd optyczny, pamięć masowa czy niekiedy interfejs taki jak Ethernet.

Załadowanie systemu operacyjnego sprowadza się do umieszczenia programu w pamięci RAM, z której będzie on następnie wykonywany. Typowy scenariusz zakłada przekopiowanie obrazu z pamięci nieulotnej (dysk twardy, pamięć Flash) do pamięci operacyjnej, gdyż z reguły jest ona znacząco szybsza.

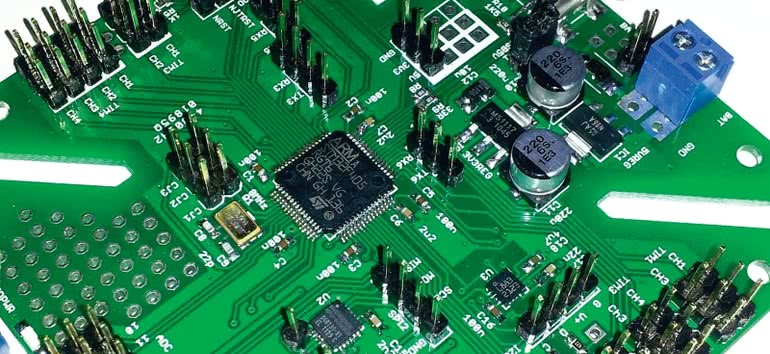

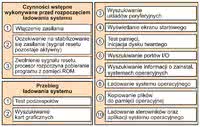

Pierwszy etap rozpoczyna się po włączeniu zasilania bądź resecie i sprowadza się do przygotowania części sprzętowej, na co składa się inicjacja układów peryferyjnych. Przykład może stanowić rodzina procesorów i.MX, która po resecie sprawdza stany logiczne na określonych wejściach, aby wybrać tryb uruchomienia. Inicjowane układy peryferyjne są niezbędne na etapie ładowania systemu.

Na przestrzeni ostatnich lat dokonał się znaczący postęp, wzrosły możliwości współczesnych procesorów i systemów wbudowanych, a co za tym idzie proces uruchamiania systemu operacyjnego też stał się znacząco bardziej skomplikowany. Oczywistą zaletą takiej sytuacji jest możliwość uruchomienia systemu operacyjnego już nie tylko z dysku twardego, ale można go załadować z szerokiej gamy nośników (chipów pamięci Flash, kart SD, przenośnych pamięci masowych USB).

Ponadto współczesne bootloadery umożliwiają ładowanie systemu operacyjnego za pośrednictwem popularnych interfejsów: UART, SATA, PCIe, Ethernet. Możliwość ładowania systemu (lub jego instalowania) za pośrednictwem pamięci masowych zapewnia oprócz wygody także szereg korzyści.

Przykład może stanowić instalowanie oprogramowania w netbookach, dzięki czemu nie muszą one mieć napędu optycznego, który nie należy do szczególnie praktycznych i niepotrzebnie zwiększałby rozmiary urządzenia. Innym zastosowaniem jest serwisowanie urządzeń z uszkodzonym firmware'em.

Serwis ma możliwość uruchomienia narzędzi diagnostycznych i zapisania nowego oprogramowania bezpośrednio z pamięci masowej. Unika się tym samym odsyłania uszkodzonego sprzętu do producenta posiadającego stosowny programator, co przyczynia się do zmniejszenia kosztów naprawy i transportu.

Procesory bardziej zaawansowane potrafią załadować system operacyjny pobrany z innych, mniej typowych źródeł, czego przykład stanowi złącze PCIe, karty SDHC, konwencjonalne (równoległe) pamięci nieulotne Flash czy USB. Urządzenie musi być jednak wyposażone w bootloader zdolny pobrać kod z wybranego źródła i umieścić go w pamięci. Przykład może stanowić U-boot dostępny wraz z otwartym kodem źródłowym znajdujący zastosowanie w systemach wbudowanych.

Ładowanie systemu Windows XP

Typowy scenariusz ładowania systemu operacyjnego pokazano na rysunku 1. Wykorzystuje go m.in. Windows XP. Po włączeniu zasilania (bądź resecie) procesor pozostaje nieaktywny do momentu ustabilizowania się napięcia zasilającego - w tym czasie wewnętrzny reset jest utrzymywany w stanie aktywnym. Po zapewnieniu właściwego zasilania rozpoczyna się wykonywanie programu pobranego z pamięci ROM.

W przypadku komputerów PC będzie to BIOS, który w pierwszej kolejności przeprowadza test POST (power-on self-test). Ocenie podlega poprawność funkcjonowania podstawowych modułów sprzętowych. Wykryte na tym etapie błędy są sygnalizowane akustycznie, gdyż karta graficzna jest inicjowana dopiero w następnym kroku.

BIOS wyszukuje układ graficzny poprzez skanowanie przestrzeni adresowej w zakresie od C000:0000 do C780:0000. W efekcie nastąpi zainicjowanie i przetestowanie każdej odnalezionej karty graficznej, potencjalnie od razu z pamięcią wideo i odczyt informacji o dostępnych monitorach. Warto zauważyć, że "zimny" reset wymusza przeprowadzenie pełnego testu od początku, podczas gdy "ciepły" pozwala pominąć część czynności sprawdzających poprawność pracy podzespołów.

W dalszej części procesu ładowania systemu operacyjnego odczytywane są dane konfiguracyjne umieszczone w pamięci, której zawartość jest podtrzymywana przez niewielką baterię litową. Pamięć ta przechowuje m.in. aktualną godzinę, datę oraz ustaloną kolejność przeszukiwania dysków i interfejsów pod kątem obecności systemu operacyjnego.

BIOS, mając do czynienia z dyskiem twardym, analizuje pierwszy sektor w poszukiwaniu MBR (Master Boot Record) zawierającego informacje o strukturze logicznej dysku (tablica partycji), umiejscowieniu aktywnej partycji oraz zawierającego program niezbędny do kontynuowania pracy. Po odnalezieniu aktywnej partycji następuje sprawdzenie sygnatury w jej pierwszym sektorze, gdy będzie ona właściwa, nastąpi wykonanie kodu znajdującego się w sektorze rozruchowym.

Z systemem Windows XP związany jest program rozruchowy NT OS Loader (NTLDR, New Technology Loader) wczytywany do pamięci przez program umieszczony w sektorze rozruchowym. NTLDR znajduje się w głównym katalogu partycji systemowej i do jego zadań należy m.in. przełączenie procesora w tryb chroniony, aktywacja 32-bitowego dostępu do pamięci, włączenie stronicowania pamięci.

Ładowany jest ponadto sterownik dający dostęp do plików zapisanych na partycjach FAT16, FAT32 oraz NTFS. Wyszukiwany jest plik hiberfil.sys tworzony podczas hibernacji systemu, jeżeli jest on obecny, następuje odtworzenie zawartości pamięci z załadowanym uprzednio systemem Windows. W przypadku braku tego pliku załadowany zostanie "czysty" system operacyjny.

NTLDR może wykryć obecność więcej niż jednego systemu operacyjnego, w takiej sytuacji wstrzyma swoją pracę i wyświetli menu umożliwiające wybór systemu, jaki ma zostać uruchomiony. Kolejnym krokiem jest uruchomienie kodu odpowiedzialnego za gromadzenie podstawowych informacji o podzespołach komputera.

Po uzyskaniu informacji o konfiguracji sprzętu następuje dalszy etap uruchamiania - ładowane są pliki jądra systemu oraz sterowniki systemowe. Na tym etapie wyświetlane jest logo systemu oraz pasek postępu informujący użytkownika o trwającym procesie. Ładowane są także sterowniki pominięte przez NTLDR.

Ostatnim krokiem będzie uruchomienie menedżera sesji odpowiedzialnego za utworzenie przestrzeni użytkownika i załadowanie sterowników urządzeń wykorzystujących podsystem graficzny. Proces uruchamiania systemu Windows XP kończy się, gdy zaloguje się użytkownik.

Procesory z rodziny i.MXPrzykładem obrazującym stopień złożoności współczesnych procesorów w zakresie ładowania systemu operacyjnego jest rodzina procesorów i.MX51 Freescale. Ma ona wbudowaną pamięć ROM, z której pobierany jest bootloader odpowiedzialny za inicjację poszczególnych modułów procesora (m.in. centralnej jednostki bezpieczeństwa CSU, interfejsu pamięci zewnętrznych EMI, kontrolera eSDHC, I²C, pętli PLL, portu szeregowego czy watchdoga). Ponadto odczytuje on bity (eFUSE) lub wejścia konfiguracyjne, w zależności od wybranego trybu, aby na tej podstawie określić sposób, w jaki ma przebiegać ładowanie systemu. Warto zauważyć, że układy i.MX51 wspierają mechanizmy bezpieczeństwa oparte na kluczu publicznym i prywatnym. Oznacza to, że projektanci mogą wykluczyć uruchamianie nieautoryzowanego (niepodpisanego prywatnym kluczem) kodu. Procesor może zostać ustawiony tak, aby nie ładował z pamięci ROM bootloadera i od razu przystąpił do pobierania systemu z pamięci zewnętrznej. Warto wspomnieć o obecności trybu serial downloader, który umożliwia załadowanie i wykonanie programu przez port szeregowy bądź USB. Przesłany w ten sposób program jest umieszczany w pamięci RAM, skąd następuje jego wykonanie i może on posłużyć do programowania zewnętrznej pamięci Flash. System ładowany przez bootloader może znajdować się na nośnikach takich jak karty pamięci MMC/SD, standardowe pamięci Flash czy pamięci szeregowe z dostępem przez interfejs szeregowy I²C (EEPROM) lub SPI (Flash). |