Transceiver sygnałów wektorowych - architektura sprzętowa

| TechnikaWprowadzenie przez firmę National Instruments na rynek wektorowego transceivera sygnałów (Vector Signal Transceiver - VST) PXIe-5644R z wbudowanym układem FPGA programowalnym przez użytkownika, zrewolucjonizowało rynek aparatury pomiarowej w.cz. i ustanowiło kamień milowy w zakresie elastyczności konfiguracji przyrządów pomiarowych. VST łączy w ramach jednego przyrządu pomiarowego wektorowy analizator sygnałów (Vector Signal Analyzer - VSA) i wektorowy generator sygnałów (Vector Signal Generator - VSG). Sterowanie tymi podsystemami (generacja, analiza sygnałów radiowych) oraz przetwarzanie sygnału mają miejsce z poziomu układu FPGA.

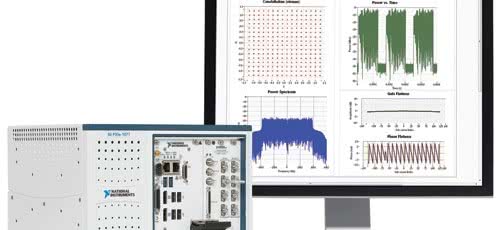

Przyrząd VST (Vector Signal Transceiver) został zaprojektowany w standardzie PXI Express i zajmuje w obudowie szerokość trzech modułów (rys. 1). Konstrukcja modułowa pozwala na tworzenie konfiguracji pomiarowych typu MIMO (wiele wejść, wiele wyjść), poprzez użycie wielu takich samych przyrządów VST umieszczonych we wspólnej obudowie.

Atutem nowego urządzenia jest z pewnością wysoka wydajność niezbędna do prowadzania prac w działach badań i rozwoju oraz niewielkie wymiary zewnętrzne. Wraz z możliwością przeprogramowywania funkcjonalności, zapewnianą przez układ FPGA pozwala to na przyspieszenie wykonywania zadań pomiarowych takich jak charakteryzacja, weryfikacja, walidacja i testy produkcyjne. VST pracuje w zakresie od 65 MHz do 6 GHz z pasmem przenoszenia do 80 MHz.

Od strony funkcjonalnej największą zmianą, zasługującą w pełni na określenie rewolucyjna, jest wbudowana macierz FPGA Virtex-6 LX195T firmy Xilinx, która może być programowana z poziomu oprogramowania LabVIEW FPGA Module. Układ FPGA jest podłączony do cyfrowych sygnałów I/Q w blokach VSA i VSG i dodatkowo do 24 linii I/O zapewniających szybkość transmisji do 250 Mbit/s.

Taka konfiguracja pozwala na wykorzystanie urządzenia w wielu różnych aplikacjach czasu rzeczywistego: do sterowaniem badanym urządzeniem podczas testów, do generowania i odbioru sygnałów radiowych w aplikacjach SDR (Software Defined Radio), emulacji kanałów radiowych w komunikacji bezprzewodowej i wielu innych zastosowań.

Architektura bloku FPGA

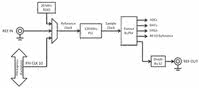

Blok FPGA transceivera VST PXIe-5644R zawiera układ Virtex-6, układ taktowania dla cyfrowego generatora sygnału baseband, pamięć DRAM i SRAM, przetworniki analogowo-cyfrowe (ADC) i cyfrowo-analogowe (DAC), cyfrowe linie I/O (PFIO), cyfrowe złącze komunikacyjne (DIO) oraz linie komunikacyjne podłączone do magistrali PXI.

Układ FPGA jest odpowiedzialny za obróbkę danych cyfrowych w urządzeniu VST i jest bezpośrednio połączony z przetwornikami, magistralą PCI Express, pamięciami oraz liniami interfejsu cyfrowego. Program sterujący dla FPGA może zostać stworzony przez użytkownika samodzielnie za pomocą LabVIEW, można też skorzystać z przykładowych projektów dostarczanych przez producenta oraz z tzw. Instrument Design VI.

Pozwalają one użytkownikom na dostęp i modyfikowanie kodu LabVIEW na poziomie procesora i FPGA (np. na PC lub z systemu operacyjnego czasu rzeczywistego) i zmiany w zakresie konfiguracji, akwizycji, generacji, przetwarzania sygnałów cyfrowych i ich synchronizacji.

Taktowanie

Transceiver VST posiada wiele wewnętrznych źródeł taktowania dostępnych z poziomu FPGA. Główny sygnał zegarowy 120 MHz jest generowany za pomocą pętli PLL i wykorzystywany do taktowania przetworników i logiki powiązanej z FPGA. Poza tym można korzystać z wewnętrznego generatora TCXO, wejścia RF IN na panelu czołowym lub użyć z zegara PXI_CLK 10 jako sygnału odniesienia dla pętli PLL.

Analogicznie główny sygnał zegarowy stanowi odniesienie dla wyjść RF IN i OUT. Mimo że jego częstotliwość jest niezmienna i ustalona na 120 MHz, mamy możliwość dzielenia lub mnożenia tego sygnału implementując odpowiedni kod na FPGA. Daje to dostęp do częstotliwości taktowania do 360 MHz.

Przetworniki i interfejsy

Transceiver VST wykorzystuje dwukanałowe 16-bitowe przetworniki ADC i DAC taktowane zegarem 120 MHz, co umożliwia obróbkę sygnału w paśmie 80 MHz. Ich działanie jest automatycznie synchronizowane z opisanym powyżej głównym zegarem taktującym dostępnym w FPGA. Takie podłączenie ułatwia wymianę danych i ich synchronizację oraz zapewnia przewidywalne opóźnienie w czasie transmisji, co jest ważne w testach aplikacji wbudowanych, takich jak radio definiowane programowo (Software Defined Radio - SDR).

Z kolei PFI 0 to dwukierunkowy, 3,3-woltowy port cyfrowy ogólnego przeznaczenia. Jest on zwykle wykorzystywany jako wejście wyzwalające lub wyjście do generacji znaczników czasu lub zdarzeń. Funkcja, jaką w systemie pełni PFI 0, jest programowana z poziomu LabVIEW.

24-cyfrowe dwukierunkowe linie I/O LV TTL mogą być konfigurowane i organizowane w oddzielne porty. Mamy do nich dostęp bezpośrednio z FPGA, dzięki czemu mogą być wykorzystane do implementacji własnych rozwiązań z poziomu modułu LabVIEW FPGA.

Pamięci DRAM i SRAM

W urządzeniu zawarto dwa banki pamięci DRAM o rozmiarze 256 MB każdy o teoretycznej przepustowości 2,1 GB/s. Każdy z nich jest dostępny z FPGA i zwykle wykorzystywany do przechowywania obwiedni generowanych przebiegów lub danych z przetworników bezpośrednio po akwizycji. Ponadto wbudowano 2 MB pamięci SRAM o maksymalnej prędkości transmisji 40 MB/s do odczytu i 36 MB/s do zapisu, która zapewnia przesyłanie danych pomiędzy poszczególnymi blokami funkcjonalnymi, np. wykorzystuje się ją do konwersji pomiędzy danymi w formacie IQ a ich reprezentacją cyfrową.