Układy ASIC/ASSP, SoC, FPGA i SoC FPGA - przegląd i przykłady

| TechnikaTytułowe grupy układów najlepiej porównywać pod kątem wymogów konkretnej aplikacji. Ogólnie można je jednak ze sobą zestawić pod względem poboru mocy, wydajności, rozmiaru oraz elastyczności zastosowania. Najmniej mocy zużywają układy ASIC/ASSP, zaś najwięcej układy FPGA. Pod kątem wydajności układy SoC ustępują obu pozostałym grupom. Elastyczność nie jest z kolei cechą układów ASIC/ASSP. Największe rozmiary mają układy FPGA, a najmniejsze zwykle układy ASIC/ASSP.

Układy ASIC/ASSP od układów elektronicznych ogólnego przeznaczenia odróżnia fakt, że realizują ściśle z góry określone zadania, w sposób zoptymalizowany pod kątem jak najmniejszego poboru mocy (energia nie jest przez nie marnowana na zasilanie niewykorzystywanych podzespołów), najwyższej wydajności i najmniejszych kosztów. Dzięki temu, że są wyposażone wyłącznie w niezbędne bloki funkcjonalne, ich zaletą są również małe rozmiary.

Ograniczenia układów ASIC/ASSP

Głównym ograniczeniem jest fakt, że układy ASIC/ASSP wykonują wyłącznie zadania, do realizacji których zostały zaprojektowane. W przyszłości nie można zatem łatwo rozszerzyć funkcjonalności urządzenia, które bazuje na układzie tego typu. Wadą układów ASIC/ASSP jest również wysoki koszt projektu i długi czas jego opracowywania. Powyższe ograniczenia sprawiają, że opłaca się z nich korzystać przede wszystkim w produkcji na masową skalę. W przeciwnym razie ich koszt jednostkowy może okazać się zbyt duży.

Układy ASIC/ASSP realizowane są w różnych technologiach. Najpopularniejszą z nich jest technologia CMOS. Zapewnia ona największą gęstość upakowania przy zarazem najniższych kosztach produkcji.

Układy ASIC/ASSP w implantach

Układy ASIC/ASSP mogą się składać wyłącznie z układów cyfrowych. Można je również zrealizować jako układy typu mixed-signal (mieszane). Wbudowane w nie komponenty analogowe stanowią przeważnie interfejs do świata zewnętrznego. Są one zazwyczaj projektowane na zamówienie konkretnego klienta. W oparciu o nie konstruuje się różne urządzenia, na przykład medyczne.

Układy tego typu są m.in. częścią urządzeń wszczepianych. Przykładami takich są: rozruszniki serca, implanty słuchowe oraz stymulatory układu nerwowego. Dzięki małym rozmiarom układów ASIC/ASSP implanty są coraz mniejsze. To ułatwia ich wszczepianie. Mogą być także dłużej zasilane z baterii. Dzięki temu rzadziej trzeba je wymieniać. Są ponadto coraz tańsze, a dzięki temu dostępne dla większej liczby pacjentów.

Co odróżnia układy SoC od ASIC/ASSP?

Układy SoC stanowią gotowe, zintegrowane systemy elektroniczne, zbudowane z wielu różnych bloków funkcjonalnych. Ich przykładowe komponenty to: procesory, procesory sygnałowe, procesory graficzne, akceleratory sprzętowe, na przykład funkcji kryptograficznych, bloki nadawczo-odbiorcze oraz bloki do obsługi różnych interfejsów komunikacyjnych.

W zależności od docelowej aplikacji bądź grupy zastosowań zawierają one więcej lub mniej tego typu, jak i innych, podzespołów. W przeciwieństwie do układów ASIC/ASSP, układy SoC nie mają bowiem ściśle ograniczonej funkcjonalności.

Przykładem są układy SoC z serii Blue Gecko z oferty firmy Silicon Labs. Można je wykorzystać do budowy m.in. urządzeń IoT, automatyki domowej i budynkowej, urządzeń pomiarowych oraz interfejsów HMI. Na rysunku 1 przedstawiono ich główne komponenty.

Blue Gecko SoC

W układach SoC z serii Blue Gecko wyróżnia się następujące sekcje: blok jednostki centralnej, którą jest 32-bitowy procesor ARM Cortex M4, blok do zarządzania pamięcią z MSC (Memory System Controller) oraz LDMA (Linked Direct Memory Access Controller), CMU (Clock Management Unit), czyli jednostkę do zarządzania sygnałem taktującym oraz EMU (Energy Management Unit). Ta ostatnia zarządza poborem mocy w różnych trybach pracy układu.

Częścią Blue Gecko SoC jest również układ nadawczo-odbiorczy do obsługi transmisji m.in. w standardzie Bluetooth Smart, blok liczników i timerów m.in. z timerem LE (Low Energy), który umożliwia realizację prostych zadań w trybie sleep oraz w trybie deep sleep, w którym pobór mocy ograniczony jest do minimum, blok obsługi transmisji szeregowej (USART, Low Energy USART, I²C), segment analogowy, z komparatorem i przetwornikami A/C i C/A, oraz akcelerator sprzętowy funkcji kryptograficznych - AES 128/256, SHA-1, SHA-2 (SHA-224, SHA-256), ECC.

Jak są zbudowane układy FPGA?

Układy FPGA składają się z matrycy bloków logicznych, które można łączyć według potrzeb, tworząc w ten sposób struktury logiczne o wymaganej funkcjonalności. Można je programować wielokrotnie.

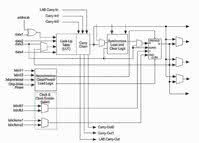

Na rysunku 2 przedstawiamy schemat podstawowego elementu logicznego układu FPGA na przykładzie LE (Logic Element) układów FPGA z serii Cyclone z oferty firmy Altera. Każdy LE składa się z następujących komponentów funkcjonalnych: czterowejściowego bloku LUT (Look-Up Table), który można zaprogramować do realizacji funkcji logicznych, programowalnego rejestru, który może pracować jako przerzutnik D, T, J-K albo RS, łańcucha przeniesień (carry chain) oraz wyprowadzeń. Te ostatnie zapewniają połączenia między wierszami i kolumnami matrycy, pomiędzy blokami LUT oraz między rejestrami sąsiadujących ze sobą LE.

Elementy logiczne tworzą bloki logiczne LAB (Logic Array Blocks). W przypadku układów FPGA z serii Cyclone jeden LAB składa się z 10 LE. W zależności od modelu układu może się on składać z od 24 do 64 kolumn LAB, podzielonych na od 13 do 32 wierszy.

Złożoność sprzętowa układów FPGA daje większe możliwości w zakresie realizacji wymaganej funkcjonalności. Niestety jest to uzyskiwane kosztem ich większego rozmiaru i większego poboru mocy w porównaniu do zarówno układów ASIC/ASSP, jak i układów SoC.

Układy ASIC/ASSP czy FPGA?

Odkąd tylko układy ASIC/ASSP i FPGA są dostępne, niezmiennie te pierwsze muszą zostać zaprojektowane i wykonane zgodnie ze specyfikacją klienta, te drugie zaś może on kupić od ręki i zaprogramować stosownie do swoich potrzeb. Z biegiem lat ewoluowały natomiast ich możliwości i zmieniała się ich opłacalność. Obie te kwestie mają kluczowe znaczenie, zwłaszcza przy wyborze układu, na bazie którego będą budowane urządzenia produkowane na masową skalę.

Możliwość szybkiej implementacji funkcjonalności i jej późniejszego zmodyfikowania w razie potrzeby jest ważną zaletą układów FPGA. Dzięki niej wprowadzanie na rynek nowych wersji urządzeń jest szybsze oraz tańsze niż w przypadku układów ASIC/ASSP.

Układy FPGA tradycyjnie nie były jednak w stanie dorównać układom ASIC/ASSP o analogicznej funkcjonalności pod względem rozmiarów, poboru mocy ani kosztu jednostkowego. Dlatego zazwyczaj znajdowały zastosowanie w urządzeniach niszowych i mniej skomplikowanych. Używano ich również do budowania prototypów.

Układy SoC FPGA

Od niedawna jednak na rynku pojawiła się jeszcze jedna grupa układów, która stanowi połączenie układów SoC i układów FPGA. Układy SoC FPGA mają już w swojej ofercie czołowi producenci układów elektronicznych, m.in. firmy takie jak: Altera, Xilinx oraz Microsemi.

Aktualnie wyróżnić można dwie metody realizacji układów SoC FPGA. Pierwsze podejście polega na wykonaniu w obrębie jednej struktury półprzewodnikowej sekcji FPGA oraz procesora wraz z pomocniczymi podzespołami.

W drugim rozwiązaniu SoC i FPGA są wykonane jako oddzielne, dyskretne układy. Następnie łączy się je ze sobą i umieszcza w jednej obudowie typu MCM (Multi-Chip Module).

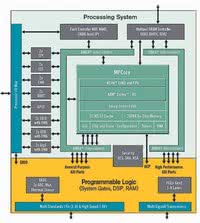

Przykładem układów typu SoC FPGA, które integrują w sobie możliwość programowej i sprzętowej realizacji wymaganej funkcjonalności, wykonanych pierwszą metodą, jest rodzina układów Zynq-7000 All Programmable SoC. Ma je w swojej ofercie firma Xilinx.

Na rysunku 3 przedstawiamy schemat blokowy układu Zynq-7000S. Jego częścią jest jednordzeniowy procesor ARM Cortex-A9 oraz układ FPGA Artix-7. Ich przykładowe zastosowania to systemy sterowania silnikami, systemy wizyjne oraz sterowniki PLC.

Układy zaliczane do kategorii SoC FPGA mają wiele zalet. Równocześnie konstruując je, trzeba sprostać licznym wyzwaniom.

SoC FPGA - zalety

Dzięki niższym częstotliwościom pracy układów FPGA, układy SoC FPGA, w których te pierwsze przejmą znaczną część zadań, będą pobierać mniej mocy. Układy FPGA charakteryzuje również determinizm czasowy, uważany za jedną z ich największych zalet.

Ponadto dzięki wydajnemu przetwarzaniu równoległemu część FPGA może znacząco przyspieszyć realizację zadań. Będzie to szczególnie zauważalne w przypadku tych najbardziej obliczeniowo obciążających. Przykładem są: operacje rozpoznawania mowy, technika sieciowa głębokiej inspekcji pakietów (Deep Packet Inspection), która może być wykorzystywana do walki z cyberprzestępcami oraz przetwarzanie dużych zbiorów danych (Big Data) w sieciach IoT.

Dzięki segmentowi FPGA w układach SoC FPGA łatwiej jest wprowadzać zmiany. Może on także pełnić funkcję łącznika z układami, gdzie zaimplementowano nowe rozwiązania, których część SoC nie obsługuje.

SoC FPGA - wyzwania

W porównaniu do układów ASIC/ASSP i SoC układy FPGA pobierają znaczne ilości mocy. Przykładowo pojedynczy blok LUT może jej zużywać w takich ilościach, jak nawet 10 bramek logicznych w układach ASIC/ASSP.

W związku z tym uzupełniając SoC o strukturę FPGA, trzeba się liczyć z tym, że pod tym względem może nastąpić pogorszenie parametrów całego układu. Aby ten niekorzystny efekt ograniczyć, powinno się w nich wdrażać techniki zarządzania poborem mocy, takie jak na przykład przechodzenie układu w tryb pracy sleep albo deep sleep.

Ze względu na rozmiary struktur FPGA, jeśli dostępna przestrzeń jest ograniczona, a wymagania odnośnie do funkcjonalności są duże, projektant zmuszony jest znaleźć rozwiązanie kompromisowe. Układy SoC FPGA wymagają też specjalnych narzędzi do programowania i testowania.

Bez nich projektanci powinni się bowiem bardzo dobrze orientować w specyfice obu tych grup układów. Potrzebne są oprócz tego narzędzia, które ułatwią optymalny rozdział zadań pomiędzy segment FPGA a podzespoły SoC.

Monika Jaworowska