Projektowanie high-speed PCB. Integralność sygnałów.

| TechnikaJedną z najczęstszych kwestii pojawiających się podczas projektowania obwodów drukowanych jest ustalenie czy realizowany układ należy do typu high-speed. Przed podjęciem próby odpowiedzi na to pytanie konieczne jest rozważenie, jakie znacznie ma termin high-speed. Jak się okazuje w praktyce, liczba możliwych odpowiedzi na tak postawione pytanie jest często równa liczbie osób, które tych odpowiedzi udzieliły. Część konstruktorów granicę, od której układ należy potraktować jako high-speed upatruje w pewnej, arbitralnie wybranej wartości częstotliwości pracy urządzenia np. 50MHz. Tymczasem inni twierdzą, że granica częstotliwości high-speed to przynajmniej 150MHz. Którzy z nich mają rację? I czy rzeczywiście kryterium częstotliwościowe jest dobre?

Czym jest high-speed?

Zagadnienia związane z problemami high-speed zostały opisane w kilku dosyć obszernych książkach posiłkujących się zaawansowanym opisem matematycznym. Celem niniejszego krótkiego wprowadzenia do technik high-speed jest zaznaczenie kilku typowych problemów tej techniki oraz ich wstępna klasyfikacja, co powinno pomóc w ich lepszym zrozumieniu. Praktyka pokazuje, że czasem istnieje poważny problem ze wstępnym zrozumieniem oraz często samym nazwaniem problemów dotyczących high-speed. Większość poruszanych zagadnień była prezentowana podczas organizowanego „Allegro high-speed Forum 2006” w Warszawie i we Wrocławiu.

W celu wprowadzenia definicji technik high-speed należy przyjrzeć się najszybciej zmieniającemu się zjawisku elektrycznemu w projektowanym układzie i sprawdzić czy czas trwania takiego zjawiska jest porównywalny z czasem propagacji sygnału pomiędzy dwiema końcówkami linii komunikacyjnej. W szczególności w układach cyfrowych najbardziej gwałtownym zjawiskiem jest moment zmiany stanu logicznego. Jeżeli czas narastania lub opadania jest porównywalny z czasem propagacji od początku do końca i z powrotem - w linii, w której sygnał jest przesyłany to można się spodziewać efektów określanych jako high-speed. Rysunek 1. przedstawia tę przybliżoną definicję graficznie.Jak widać, definicja ta nie jest bezpośrednio związana z częstotliwością pracy układu, chociaż jest oczywiste, że przebiegi cyfrowe o dużej częstotliwości maja także bardzo krótkie czasy narastania impulsów. Pozwala to przyznać częściowo rację zwolennikom definicji opartej na częstotliwości pracy układu. Jednak poważnym mankamentem takiego podejścia jest możliwości istnienia bardzo krótkich czasów narastania sygnałów w układach pracujących na względnie niskiej częstotliwości, np. 20MHz. Czas narastania zależy od bufora zastosowanego układu scalonego, więc nowoczesny bufor charakteryzujący się krótkim czasem narastania impulsów zastosowany we względnie wolnym obwodzie może być źródłem problemów określanych jako high-speed.

Problemy projektowania high-speed można wstępnie podzielić na przynajmniej trzy zagadnienia obejmujące kwestie integralności sygnałów (SI), integralności układów zasilania (PI) oraz kompatybilności elektromagnetycznej (EMC). W tym artykule zostaną poruszone jedynie sprawy wiązane z integralnością sygnałów.

SI - integralność sygnałów w PCB

Problem integralności sygnałów w płytkach PCB sprowadza się do zapewnienia prawidłowego przeniesienia informacji zawartej w sygnale wysyłanym z bufora nadajnika do bufora jednego lub większej liczby odbiorników. Bez zastosowania specjalnych technik konstrukcyjnych sygnały w urządzeniach high-speed mogą ulec i ulegają zwykle odkształceniom, które doprowadzają do zafałszowania przenoszonej informacji, czyli utraty integralności. Przykłady utraty integralności sygnałów przedstawia rysunek 2.Przyczyny te to:

Overshoot/Undershoot – przepięcia, które w skrajnym przypadku mogą doprowadzić do zniszczenia układu elektronicznego.

Multi-Crossing – zakłócenie polegające na wprowadzeniu fałszywej informacji o momencie ostatecznego przełączenie się bufora na oczekiwany stan logiczny.

Oscillation – zakłócenie wprowadzające opóźnienie spodziewanego momentu przełączenia się bufora.

Threshold – stłumienie sygnału podczas transmisji w taki sposób, że bufor nie zostanie przełączony.

Sygnały w PCB są propagowane przewodzącymi ścieżkami łączącymi bufory. Dla niskich częstotliwości, ścieżki te wykazują jedynie niewielką rezystancję i można je często potraktować jako zwarcie. W zakresie wysokich częstotliwości ścieżka przewodząca zachowuje się jak stratna linia transmisyjna o schemacie zastępczym przedstawionym na rysunku 3.Linia transmisyjna składa się z jednej lub wielu linii sygnałowych oraz linii powrotu. Linia transmisyjna zawiera elementy RLGC, opisujące jej własności stratne. Model linii transmisyjnej składa się z większej liczby czwórników RLGC (oznaczonych na rysunku 3. symbolem Δx) wystarczającej do przedstawienia całej długości linii. Znaczenie elementów RLGC jest następujące: R jest szeregową rezystancją linii sygnałowej, L jest indukcyjnością własną linii sygnałowej, G jest przewodnością związaną z upływnością izolacji, a C jest pojemnością między linią sygnałową a linią powrotu. Wartości elementów RLGC są wyznaczane na jednostkę długości linii.

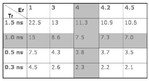

Istotne jest aby ustalić, w jakich warunkach badane połączenie na PCB można traktować jako zwarcie, a w jakich jako linię transmisyjną. Bardzo pomocne w prawidłowym rozstrzygnięciu tego problemu jest posłużenie się pojęciem długości elektrycznej, która odpowiada drodze, jaką pokonuje sygnał podczas czasu narastania lub opadania. Oczywiście należy traktować tę definicja jako zgrubną. Połączenia, których długość odpowiada 1/6 długości elektrycznej traktuje się jako linie krótkie czyli zwarcia. Definiuje się także długość krytyczną, która odpowiada połowie drogi elektrycznej. Jeżeli połączenie znajdujące się w danym otoczeniu dielektrycznym jest dłuższe od linii krótkiej i krótsze od długości krytycznej to można już spodziewać się efektów linii transmisyjnej, jeżeli zaś długość połączenia przekracza długość krytyczną to połączenie z całą pewnością należy traktować jako stratną linię transmisyjną. Rysunek 4. ilustruje tę klasyfikację, a rysunek 5. przedstawia wybrane wartości długości krytycznej w zależności od długości połączenia i środowiska dielektrycznego. Najważniejszą właściwością opisującą zachowanie linii transmisyjnej jest jej impedancja charakterystyczna. Aby ją zinterpretować warto przyjąć uproszczony, bezstratny model linii uzyskany poprzez pominięcie elementów R i G. Jest to uzasadnione postępowanie dla wysokich częstotliwości.Przeprowadzając analizę sygnałów w linii transmisyjnej w dziedzinie czasu można łatwo zauważyć, że na początku transmisji impedancja widziana od strony wejścia do linii jest niezależna od impedancji obciążenia. Linia transmisyjna składa się z bardzo dużej liczby połączonych ze sobą czwórników LC i każdy z nich musi być kolejno, jeden po drugim ładowany prądem ze źródła bufora. Wobec tego zawsze minie pewien czas do momentu, kiedy wszystkie czwórniki LC zostaną naładowane i prąd będzie płynął przez obciążenie na końcu linii. Do tego czasu wartość impedancji widzianej od wejścia będzie zależna o wartości elementów LC. Przy okazji widać, że linia transmisyjna wprowadza opóźnienie sygnału wprost proporcjonalne do jej długości.

Każda linia transmisyjna jest połączona z buforem nadajnika i buforem odbiornika, które również charakteryzują się pewną wartością impedancji. Wzajemne niedopasowanie impedancji buforów i impedancji linii prowadzi do powstawania odbić w linii transmisyjnej, których amplituda oraz kierunek są wprost proporcjonalne do wartości odpowiednich współczynników odbić. Współczynniki odbić definiuje się dla początku i końca linii transmisyjnej. Rysunek 6. przedstawia bezstratną linię transmisyjną oraz definicję jej najważniejszych parametrów.

Z punktu widzenia przenoszenia mocy najlepszą sytuacją jest dopasowanie impedancyjne linii transmisyjnej oraz dołączonych do niej buforów. Unika się wtedy odbić prowadzących do znacznych zniekształceń propagowanego sygnału. Niestety, nie zawsze jest to możliwe, a powstałe wtedy odbicia można ograniczać poprzez redukcję szybkości sygnałów przesyłanych przez linię lub poprzez skracanie długości linii transmisyjnej. Obydwie te metody w praktyce nie znajdują zastosowania, gdyż rzadko chcemy redukować zakłócenia kosztem szybkości pracy układu. Po drugie zmniejszenie długości linii transmisyjnej jest zwykle bardzo kłopotliwe ze względu na wykonane już ułożenie elementów. Trzecią metodą jest używanie tzw. układów terminujących składających się z elementów dyskretnych a czasem także z diod. Układy te pozwalają uzyskać dopasowanie impedancyjne. Typowe schematy układów terminujących łatwo znaleźć w literaturze, a ich przykładem może być szeregowo włączony rezystor. W celu obserwacji wpływu odbić na poziom napięcia w niedopasowanej linii transmisyjnej wygodnie jest posłużyć się diagramem odbić. Rozpatrzmy linię transmisyjną o następujących parametrach: długość linii 14,8mm, stała dielektryczna 4.1, impedancja linii to 50Ω, impedancja źródła 25Ω, obciążenia 150Ω, napięcie 5V. Jest to przykład tzw. linii przesterowanej ponieważ impedancja źródła jest mniejsza od impedancji charakterystycznej linii. Odpowiedni diagram odbić przedstawia rysunek 7. Analiza diagramu odbić pozwala zrozumieć, co dzieje się w linii transmisyjnej w czasie od wprowadzenia sygnału do linii transmisyjnej aż do czasu ustalenia się jej punktu pracy.Niestety w rzeczywistości bufory rzadko wykazują liniową charakterystykę impedancyjną i modelowanie ich działania nie jest zagadnieniem prostym. Bufory można modelować pełnym opisem SPICE lub opisem behawioralnym, pomijając już modele liniowe, które nadają się do symulacji na poziomie systemów oraz do bardzo ogólnego oszacowywania. Modele zawierające pełen opis SPICE są bardzo dokładne, ale wymagają czasochłonnych symulacji oraz są trudno dostępne ze względu na ochronę własności intelektualnej. Modele behawioralne są wystarczająco dokładne do analiz na poziomie systemów i buforów oraz są dużo szybsze od modeli SPICE. Modele behawioralne nie ujawniają szczegółów układowych, pomagają więc chronić producentom półprzewodników własność intelektualną. W latach 90. firma Intel wprowadziła standard IBIS – I/O Buffer Information Specification. Model zastępczy bufora wyjściowego oraz jego przykładowe charakterystyki I/V przedstawia rysunek 8.

Programy do symulacji

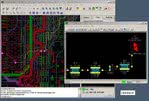

Środowisko do symulacji i analizy Allegro SI firmy Cadence Design Systems pozwala między innymi na szybką symulację połączeń na PCB przy użyciu modeli behawioralnych oraz modelu linii transmisyjnej. Używany wewnętrznie symulator TLSim jest specjalizowaną odmianą symulatora SPICE optymalizowanego pod kątem zbieżności metod numerycznych do analizy linii transmisyjnych. Allegro SI może użyć topologii istniejącego połączenia na PCB co pozwala na ekstrakcję rzeczywistych, fizycznych cech połączenia uwzględniających kształt i długość linii, warstwy na których połączenie jest prowadzone, przelotki, a także modele buforów zdefiniowanych wcześniej i powiązanych z używanymi na PCB lub na schemacie symbolami. Otrzymane w wyniku takiej ekstrakcji informacje mogą służyć jako doskonały materiał do przeprowadzenia analiz połączenia pod kątem integralności sygnałów. Rysunek 9. przedstawia proces ekstrakcji połączenia z programu Allegro PCB. Bardzo ważną cechą ekstraktora jest traktowanie połączeń miedzy buforami jako tzw. sieci rozszerzonych - X-sieci, które mogą składać się z kilku sieci połączonych elementami dyskretnymi, takimi jak np. szeregowe rezystory.W innej sytuacji, gdy ekstrakcja odbywa się na poziomie schematu ideowego lub obwodu PCB bez przeprowadzonego routingu uzyskane informacje mogą być użyte do tzw. wirtualnego projektowania, którego celem jest symulacja połączeń bazująca na modelach buforów oraz dowolnie definiowanych parametrach połączenia. Wirtualne projektowane określane jako pre-routing analisis pozwala na stworzenie kompletu reguł projektowych, których spełnienie podczas projektowania fizycznego połączenia (routingu) zapewni integralność sygnałów. Reguły projektowe dotyczą takich parametrów jak wybór warstwy, długości i szerokości połączenia oraz, co najważniejsze, wyboru rodzaju terminacji dla danej linii transmisyjnej. Rysunek 10. przedstawia wynik ekstrakcji X-Sieci przed routingiem. Widać na nim m.in. rezystor, który w normalnej sytuacji powoduje rozbicie sieci rozszerzonej na dwie osobne sieci.

Oczywiście, po zaprojektowaniu połączenia, zawsze można dokonać ekstrakcji fizycznej i wykonać analizy potwierdzające słuszność wprowadzonych podczas projektowania wirtualnego reguł projektowych. Istotną cechą programu Allegro SI jest pełna, obustronna integracja z programami Allegro Editor i Allegro Design Entry HDL, co pozwala na wykonywanie symulacji zarówno z poziomu PCB jak i z poziomu schematu ideowego. Program pozwala zarówno na ekstrakcje topologii sieci jak i automatyczne zwrotne przekazanie opracowanych podczas symulacji reguł projektowych, co oznacza, że konstruktor pracuje w jednolitym środowisku i nie musi zajmować się żadnymi konwersjami danych czy ich ręcznym wprowadzaniem. Stworzone reguły projektowe zostają automatycznie umieszczone w zarządcy reguł projektowych i są natychmiast widoczne w całym systemie do projektowania PCB. Wyniki symulacji przykładowego połączenia o topologii gwiazdy przeprowadzonej programem Allegro SI firmy Cadence przedstawia rysunek 11.

Podsumowanie

Zagadnienie integralności sygnałów nie sprowadza się oczywiście jedynie do problemów przedstawionych w tym artykule. Jednakże są to niezbędne informacje potrzebne do wstępnego zrozumienia natury tych zjawisk. Integralność sygnałów nie jest również jedynym problemem, którego rozwiązanie trzeba przewidzieć w trakcie projektowania PCB. Inne problemy takie jak integralność zasilania czy zapewnienie kompatybilności elektromagnetycznej zostaną omówione w następnych artykułach o projektowaniu high-speed PCB.

Tomasz Górecki, FlowCAD