Pętla fazowa - kiedyś i dzisiaj

| TechnikaPierwsze układy pętli synchronizacji fazy (PLL) datuje się na lata 20. ubiegłego wieku, jednak wzrost ich popularności nastąpił dopiero w momencie wprowadzenia na rynek gotowych układów scalonych realizujących tę funkcję, jak na przykład powstały w latach 70. ubiegłego wieku chip CMOS 4046. Był on jednym z pierwszych układów scalonych z pętlą fazową, które znalazły potem zastosowanie w takich aplikacjach, jak synteza częstotliwości, demodulacja i modulacja FM, konwersja napięcia na częstotliwość oraz synchronizacja danych w transmisji szeregowej.

Układ zawierał dwa rodzaje detektorów fazy (liniowy układ mnożący i wyzwalany zboczem detektor fazy/częstotliwości), generator sterowany napięciem (VCO) oraz bufor ułatwiający budowę demodulatora. Dodanie zewnętrznego dzielnika pozwalało na skonfigurowanie obwodu do pracy jako syntezatora częstotliwości od dziesiątek kiloherców do jednego megaherca. Konieczne było również stosowanie zewnętrznego filtra, jednak pozwoliło to na elastyczną regulację dynamiki działania pętli poprzez dobór elementów sprzężenia zwrotnego.

Obecnie najczęściej występującym rodzajem PLL w aplikacjach SoC jest powielacz częstotliwości, który wytwarza sygnał zegarowy w.cz. na podstawie sygnału z rezonatora n.cz. lub innego źródła częstotliwości wzorcowej. Aplikacje pętli z powielaniem częstotliwości są rozpowszechnione na rynku i wykorzystywane do taktowania układów logicznych oraz jako lokalne oscylatory w.cz. - współczesny układ SoC zawiera zwykle od 5 do 10 takich pętli PLL.

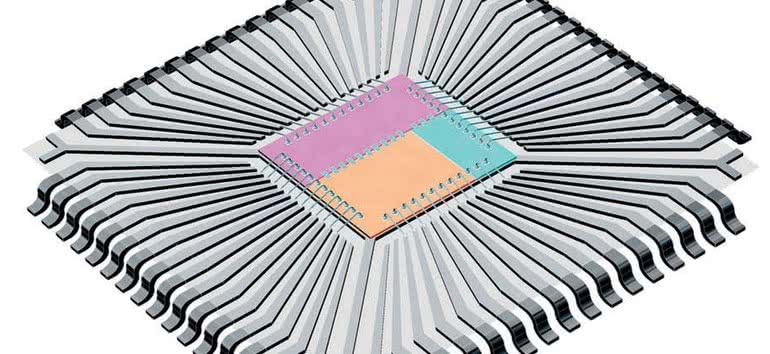

Ciekawie wygląda porównanie współczesnej pętli powielającej częstotliwość w układzie SoC ze starym rozwiązaniem z układu 4046 z rozbudowaną o zewnętrzny dzielnik i filtr (rys. 1). Pętla z układu 4046 zajęłaby kilkaset mm² powierzchni PCB, podczas gdy w pełni zintegrowany współczesny PLL zajmuje około 0,07 mm², czyli obszar około 2000 razy mniejszy. Ponadto typowa częstotliwość wyjściowa obecnych syntezerów wynosi 2 GHz, czyli około 2000 razy więcej przy podobnym zużyciu energii.

Wzrost rozdzielczości

Większość pętli PLL wykorzystywanych do syntezy częstotliwości składa się z dwóch dzielników częstotliwości: odniesienia (÷N) i wyjściowego (÷P) oraz dzielnika w sprzężeniu zwrotnym (÷M). Takie połączenie zapewnia możliwość konfigurowania wyjścia o częstotliwości FIN×M/(N×P) i rozdzielczości FIN/(N×P). Zwiększenie wartości podziału poprawia rozdzielczość, jednak dzieje się to kosztem innych ważnych parametrów.

Zwiększenie N zmniejsza częstotliwość porównawczą PLL (skok) oraz pasmo, a zmniejszenie pasma zwiększa czas ustalania synchronizacji, rozmiar filtra i tym samym obszar PLL, a także długoterminowy jitter częstotliwości. Z kolei zwiększenie wartości podziału P wymaga P razy szybszego działania generatora VCO. W wielu aplikacjach P wynosi więc od 2 do 4. Przy większych wartościach wymaganej częstotliwości VCO można przekroczyć ograniczenia procesu technologicznego lub układowe.

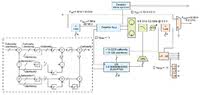

Zatem zwiększenie podziału poprzez dzielnik wyjściowy, po to aby poprawić rozdzielczość, ma także poważne wady. Jednym ze sposobów ich uniknięcia jest zastąpienie jednego z dzielników dzielnikiem o wartości niecałkowitej, jak ma to miejsce np. w PLL z ułamkowym dzielnikiem odniesienia. Uzyskanie ułamkowego dzielnika np. o wartości 10,25 jest możliwe z wykorzystaniem następującej sekwencji wartości dzielników: 10, 10, 10, 11, 10, 10, 10, 11 itd., co umożliwia prosty rejestr (rys. 2).

Następnie należy wybrać dzielnik, który będzie miał podział ułamkowy. Dzielnik wyjściowy ma tę wadę, że szum lub jitter VCO przenosi się bezpośrednio na jego wyjście, co jest zazwyczaj nieakceptowalne. W celu minimalizacji jitteru okres drgań VCO musi być mały, czyli powinien pracować on na wysokiej częstotliwości.

Ułamkowy dzielnik referencyjny lub wyjściowy to lepszy wybór, ponieważ pętla działa jak filtr dolnoprzepustowy na szum lub jitter modulacji dzielnika sprzężenia zwrotnego. Między częstotliwością VCO i częstotliwością odniesienia występuje zależność: FVCO=FREF×M/N. W większości rzeczywistych PLL wartość M jest większa niż N, więc okres VCO jest mniejszy niż okres odniesienia.

W przykładzie sekwencji pozwalającej na uzyskanie dzielnika o wartości 10,25 wzór dzielenia powtarza się co cztery cykle, czego wynikiem jest pojawienie się szumu na częstotliwości FREF/4. Użycie takiej samej metody do uzyskania wartości 10,01 wygeneruje szum na częstotliwości FREF/100. Szum widmowy jest problemem w wielu układach wykorzystujących PLL z ułamkowym dzielnikiem lewostronnym. Jeśli szum znajdzie się poniżej pasma PLL, to wynikiem może być znaczny długoterminowy jitter, nieakceptowalny w wielu aplikacjach.

Przełomem w rozwoju PLL z ułamkowym dzielnikiem odniesienia było zastosowanie w 1993 roku modulacji delta-sigma do ditherowania podziału dzielnika sprzężenia zwrotnego (rys. 2). Technika ta pozwala przesunąć szum za pomocą ditheringu (rozpraszania) na PCB do wysokich częstotliwości, w których może być łatwo odfiltrowany przez pętlę fazową.

Dzięki temu mogły powstać pętle z ułamkowymi dzielnikami, w których niepożądane składowe wywołane niecałkowitym podziałem zostały niemal całkowicie usunięte. Parametry zintegrowanych pętli z ułamkowym dzielnikiem referencyjnym są wciąż gorsze od wydajności ich odpowiedników z dzielnikiem całkowitym z powodu zbyt małego pasma do odfiltrowania szumu ditheringu. Mniejsze pasmo powoduje, że PLL gorzej tłumi szum fazowy VCO.

W najnowszych PLL szum ditheringu modulatora delta-sigma jest likwidowany przez zastosowanie odpowiedniej korekcji bezpośrednio w filtrze pętli. Zysk w takiej sytuacji może wynieść od 10 do 20 dB, co pozwala na zwiększenie pasma PLL z ułamkowym dzielnikiem odniesienia przy jednoczesnym zmniejszeniu zajmowanej powierzchni, szumu fazowego oraz jitteru. Tym sposobem wydajność PLL z ułamkowym dzielnikiem referencyjnym można zwiększyć do poziomu wydajności osiąganej przez PLL z dzielnikiem całkowitym.

Wzrost jakości

Od początku lat 90. ubiegłego wieku w układów scalonych tworzonych w procesach CMOS zaczęto integrować cewki. Ich współczynniki dobroci Q były początkowo niskie w porównaniu do komponentów dyskretnych lub podobnych cewek do aplikacji w.cz., ale zastosowanie miedzi zamiast aluminium w warstwie metalizacji przyczyniło się do zmniejszenia rezystancji szeregowej i zwiększenia współczynnika dobroci Q.

Od dziesięcioleci w układach scalonych umieszczane są też różne formy kondensatorów, a użycie cewek wraz z kondensatorami w generatorze VCO przyczynia się do znacznego wzrostu skali integracji. Ponadto dzięki rozwojowi technik CMOS nastąpił wzrost częstotliwości i zmniejszenie wymiarów cewek, przez co tworzenie półprzewodników z cewkami umieszczonymi w strukturze stało się ekonomiczne.

Dobre parametry oscylatorów LC w zintegrowanych scalonych pętlach fazowych sprawiają, że pętle PLL sprawdzają się nawet w aplikacjach wymagających niskiego szumu fazowego, takich jak transmisja danych w synchronicznych sieciach optycznych i komunikacja komórkowa, w których wymagany długoterminowy jitter musi być zwykle mniejszy niż 1 ps.

Stan obecny

Obecnie w wielu układach PLL stosuje się cyfrowy filtr pętli sprzężenia zwrotnego zamiast analogowego. Przewagą cyfrowego filtra pętli nad analogowym jest mniejszy rozmiar (rys. 3), który w analogowej pętli fazowej zależy głównie od pasma. W przypadku dużego pasma filtr pętli zajmuje ok. 50% powierzchni zajmowanej przez syntezer.

Przy małym paśmie filtr może wykorzystać znaczną część obszaru, a pętla analogowa może ponadto wymagać filtra zewnętrznego, który zajmie dodatkowy obszar PCB oraz cenne piny we/wy. Z kolei w wyniku rozwoju procesów technologicznych powierzchnia zajmowana przez sumatory i rejestry cyfrowego filtru ma coraz mniejsze znaczenie.

W analogowej PLL pompa ładunku oraz filtr pętli przetwarzają sygnały PWM z cyfrowego detektora fazy na impulsy prądowe i dalej wytwarzają analogowe napięcia przestrajające VCO, który wytwarza częstotliwość proporcjonalną do analogowego napięcia sterującego.

Cyfrowemu detektorowi fazy pętli analogowej odpowiada w pętli cyfrowej analogowo-cyfrowy przetwornik fazy lub czasu, a VCO jest zastąpiony przez DCO. Powstały obwód jest typem przetwornika C/A, w którym wielkością analogową jest częstotliwość zamiast napięcia. Oprócz mniejszej powierzchni, przewagą cyfrowego filtra pętli są mniejsze szumy. Szum kwantyzacji wynosi 0,5N, gdzie N oznacza liczbę bitów, więc w celu dwukrotnego zmniejszenia szumu należy dodać jeden bit.

Jest to prostsze działanie niż walka o parametry jakościowe filtru analogowego. Tym sposobem można łatwo zniwelować szum kwantyzacji w cyfrowym filtrze pętli kosztem niewielkiej powierzchni. Takie działanie przenosi jednak problem na konstrukcję wysokiej jakości przetwornika czasu na wartość cyfrową oraz na generator DCO. Zaprojektowanie tych elementów tak, aby działały z dużą liczbą efektywnych bitów, wciąż stanowi duże wyzwanie.

Aplikacje dla mniejszych PLL

Rozwój procesów technologicznych umożliwił integrację większej liczby pętli PLL w układach SoC, a oprócz syntezy częstotliwości ważne stały się również inne zastosowania PLL. Jednym z nich jest wsparcie dla systemów komunikacji szeregowej między układami scalonymi wymagające zintegrowania pary obwodów serializacji i deserializacji (SERDES).

Główną korzyścią komunikacji tego typu jest zmniejszenie zajmowanej powierzchni w stosunku do zbioru równoległych linii wejścia-wyjścia. Zaletą jest też zmniejszenie złożoności płytki drukowanej, ponieważ łącza szeregowe wymagają mniejszej liczby ścieżek. Działanie serializacji i deserializacji zależy od sygnału zegarowego wygenerowanego przez pętlę fazową.

Serializer wymaga mnożącej częstotliwość pętli o małym jitterze jako przekaźnika, która mnoży częstotliwość zegarową interfejsu równoległego, aby otrzymać częstotliwość interfejsu szeregowego. Długoterminowy jitter pętli wynosi zwykle mniej niż 1% rms okresu zegara, co daje 1 ps rms dla 10 Gbps.

Odbiornik wymaga obwodu odzyskiwania sygnału zegarowego oraz danych (CDR - Clock Data Recovery) synchronizującego przebieg zegarowy między nadajnikiem a odbiornikiem. Obwody CDR już od kilkudziesięciu lat znajdują zastosowanie w komunikacji optycznej, jednak w ciągu ostatniej dekady stały się tak małe, a ich zużycie mocy spadło na tyle, że integracja układów SERDES stała się praktyczna.

Dzięki miniaturyzacji pętle fazowe znajdują też nowe zastosowania. Przykładami mogą być PLL likwidujące opóźnienie zegara oraz wielofazowe PLL do generowania od 4 do 32 zegarów wyjściowych o stałym przesunięciu fazowym, które stosuje się w odbiornikach w.cz. i wielokanałowych obwodach CDR.

Grzegorz Michałowski