Redukcja mocy w wysokowydajnych układach FPGA

| TechnikaUkłady logiczne nie wykazywały dotąd wysokiego poboru mocy statycznej, jednak zmieniło się to radykalnie wraz z rozwojem procesu technologicznego. Prąd upływowy układów logicznych jest obecnie głównym problemem w FPGA. Ponieważ moc statyczna w takiej sytuacji rośnie, jej zużycie w układach wykonanych w procesach technologicznych 65nm i nowszych staje się kwestią kluczową, jeśli nie stosuje się technik oszczędzania.

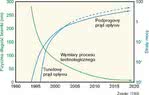

Na pobór mocy statycznej składa się głównie tunelowy prąd upływu przez cienką warstwę tlenku izolującego bramkę oraz podprogowy prąd upływu (rys. 1). Całkowity pobór mocy stanowi suma mocy statycznej i dynamicznej. Moc statyczna jest zużywana przez zaprogramowany, ale niepracujący układ FPGA. W układzie logicznym wynika ona głównie z prądu spoczynkowego, powstającego, gdy obwód nie jest obciążony (rys. 2).

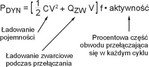

Moc dynamiczna jest zużywana podczas funkcjonowania urządzenia i wynika z przełączania tranzystorów oraz ładowania i rozładowywania obciążenia pojemnościowego. Największy wpływ na ten rodzaj mocy ma ładowanie pojemności, wartość napięcia źródła zasilania oraz częstotliwość zegarowa (rys. 3).

Moc dynamiczna maleje zgodnie z prawem Moore’a w wyniku rozwoju procesu technologicznego, ponieważ następuje spadek pojemności pasożytniczych oraz obniżają się wartości wykorzystywanych napięć zasilających. Jednak wyzwaniem technologicznym staje się sytuacja, w której implementuje się coraz więcej obwodów oraz wzrastają maksymalne częstotliwości taktowania układów FPGA.

Programowalna technologia zarządzania mocą

Postęp w dziedzinie architektur, technik wytwarzania obwodów oraz zmniejszenie wymiarów tranzystorów w nowych procesach technologicznych pomaga rozwiązywać problemy związane ze zużyciem mocy. Przykładem jest układ Stratix III firmy Altera i jej programowalna technologia zarządzania mocą (Programmable Power Technology), redukująca moc w najnowocześniejszych układach FPGA.

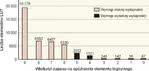

Elementy logiczne wysokowydajnych układów FPGA zapewniają maksymalną szybkość oraz generują wysokie straty mocy. Technologia PPT wykorzystuje fakt, że większość obwodów jest wykonanych z dodatkowym zapasem mocy (excess slack) i w związku z tym nie wymaga elementów o najwyższej wydajności. Rysunek 4 pokazuje typowy wykres zapasu mocy, w którym większość ścieżek logicznych reprezentowanych po lewej ma rezerwy mocy, a jedynie kilka kluczowych potrzebuje elementów o maksymalnej wydajności, aby spełnić wymagania czasowe układu. Dzięki tej technologii struktura logiczna Stratix III może być zaprogramowana na poziomie bloków logicznych LAB (Logic Array Block) do zapewnienia wysokiej szybkości lub niskiego zużycia mocy elementów logicznych, w zależności od wymagań konkretnej ścieżki logicznej (rys. 5). Tym sposobem, niewielki odsetek obwodów pracuje w trybie wysokiej szybkości, podczas gdy pozostałe funkcjonują w trybie małego poboru mocy.

Dalsze ograniczenie zużycia mocy może wynikać z zaprogramowania trybu oszczędzania mocy w nieużywanych komórkach logicznych, blokach DSP oraz pamięciach TriMatrix.

Ustawialne napięcie rdzenia

W układzie Stratix III mogą być stosowane różne napięcia rdzenia, w zależności od wymagań dotyczących wydajności. Napięcie rdzenia na poziomie 0,9V zapewnia minimalną szybkość oraz oszczędność pobieranej mocy o około 30% w stosunku do napięcia 1,1V, które gwarantuje najwyższą całkowitą wydajność. Moc dynamiczna zależy od kwadratu napięcia rdzenia, podczas gdy moc statyczna zależy od napięcia rdzenia podniesionego do potęgi 2,5, więc zmniejszenie może znacznie zredukować obie te moce. Napięcie rdzenia zasila wszystkie bloki LAB, DSP oraz pamięci i ma wpływ na wydajność całej struktury układu.

Połączenie technologii zarządzania mocą z wykorzystaniem różnych napięć rdzenia może zapewnić redukcję nawet do 50% mocy dynamicznej dla napięcia 1,1V (rys. 6). Zużycie mocy statycznej może się znacznie różnić, w zależności od stopnia wykorzystania zasobów, takich jak bloki DSP oraz pamięci TriMatrix.

Suma mocy statycznej i dynamicznej zależy od napięcia rdzenia oraz stosunku elementów pracujących w trybie wysokiej szybkości do elementów o niskim poborze mocy. W większości przypadków można osiągnąć redukcję całkowitej mocy na poziomie ponad 50%.

Proces technologiczny

Do zwiększenia wydajności oraz efektywnego zarządzania mocą w układach wykonanych w procesie technologicznym 65nm stosuje się różne strategie. Firma Altera w swoich układach FPGA wykorzystuje potrójną warstwę izolującą bramkę w celu zmniejszenia prądu upływowego kanał–źródło i dren–źródło. Zwiększa to napięcia progowe tranzystorów i zmniejsza ich szybkość przełączania. Wykorzystywana jest także technologia naprężonego krzemu (strained silicon), która zwiększa ruchliwość nośników ładunku w tranzystorach i pozwala na wzrost prądu sterującego bez zwiększenia prądu upływowego. Stosuje się również izolatory o niskiej stałej dielektrycznej, co ma bezpośredni wpływ na zmniejszenie poboru mocy dynamicznej.

Minimalna moc, maksymalna wydajność

W celu osiągnięcia maksymalnej wydajności układ FPGA Stratix III wykorzystuje moduły o architekturze ALM (Adaptive Logic Module) oraz sieć połączeń MultiTrack. Kombinacja tych elementów zapewnia większą gęstość upakowania modułów logicznych i krótsze trasy sygnałowe. Używana w Stratix III hierarchiczna struktura zegarowa może wykorzystywać do 360 oddzielnych zegarów. Elementy logiczne ze wspólnymi zegarami są grupowane w bloki LAB, a dany sygnał zegarowy jest wykorzystywany tylko w tych elementach logicznych, które go używają, w celu minimalizacji zużycia mocy.

Oszczędne wykorzystywanie pamięci

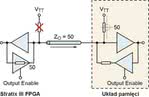

Pamięci DDR (Double Data Rate) są jednymi z obecnie najczęściej stosowanych obecnie i mogą wymagać dużej mocy. W celu zmniejszenia zapotrzebowania na moc powinno się stosować technologię OCT (On-Chip Termination) i pamięci DDR3. Istotne jest, aby podczas zapisu i odczytu z zewnętrznej pamięci wykorzystywać bufor o dopasowanej impedancji. Jeśli wykorzystywana jest linia transmisyjna o impedancji charakterystycznej 50Ω, podczas zapisywania do pamięci potrzebny jest dopasowany bufor z włączoną szeregowo impedancją o tej samej wartości. Podczas odczytu danych z pamięci, pożądane jest doprowadzenie równoległego rezystora 50Ω do napięcia terminacji. Mechanizm ten nie jest wykorzystywany jedynie przez pamięci DDR, ale także przez RLDRAM oraz QDRRAM. Dzięki wykorzystaniu technologii OCT, rezystor terminacji układu FPGA może być włączony lub odłączony, w zależności od rodzaju wykonywanej operacji. W czasie zapisu, impedancja bufora wyjściowego FPGA musi być dopasowana do linii transmisyjnej. Jednak użyty w tym celu rezystor równoległy do VTT marnuje moc i redukuje zakres możliwych zmian sygnału. Aby temu zapobiec, rezystor może być odłączony (rys. 7). Podczas odczytu, włączony równoległy rezystor zapewnia terminację linii transmisyjnej, co zmniejsza odbicia pogarszające integralność sygnału oraz zdolność do niezawodnego odczytu danych.

Znaczące korzyści technologii OCT widoczne są podczas zapisu z FPGA lub w trybie bezczynności. W pierwszym przypadku oszczędność mocy statycznej może wynieść 1,6W dla magistrali 72-bitowej. Ponadto podczas zapisu osiągnięta jest terminacja linii oraz nie ma potrzeby użycia dużej liczby rezystorów, co oszczędza koszt i zmniejsza złożoność układu.

Pamięć DDR3 wymaga 30% mniej mocy niż DDR2, ponieważ wykorzystuje napięcie zasilania na poziomie 1,5V zamiast 1,8V. Przykładowo, układ DDR2 z jednym 72-pinowym interfejsem o przepustowości 400Mb/s oraz z technologią OCT pobierałby 3,9W. Stosowanie OCT z wyłączonym równoległym rezystorem terminacji podczas bezczynności lub zapisu może oszczędzić 1,6W. Jeśli wykorzysta się zarówno pamięci DDR3, jak i technologię OCT, moc spada do 1,6W, oszczędzając całkowicie 2,3W na każdym interfejsie. Jeżeli w układzie FPGA znajdują się cztery interfejsy pamięci to całkowita zaoszczędzona moc wyniesie 9,2W.

Podsumowanie

Przejście do wytwarzania układów w procesach technologicznych 65nm i mniejszych zapewnia oczekiwane zgodnie z prawem Moore’a korzyści wynikające ze zwiększonej wydajności i gęstości upakowania tranzystorów. Jednak wzrost wydajności wpływa na wzrost zużycia mocy. Pobór mocy statycznej może się znacznie zwiększyć, jeśli nie stosuje się żadnej z opisanych metod. Podobnie jest w przypadku mocy dynamicznej, która rośnie w wyniku wzrostu pojemności elementów logicznych oraz większych częstotliwości przełączania tranzystorów. Przezwyciężenie powyższych problemów przez postęp w technice obwodów, wykorzystanie innowacyjnych architektur i procesów technologicznych zapewnia efektywne rozwiązanie dla obecnych, coraz bardziej złożonych układów FPGA.

|

Tabele

|

Grzegorz Michałowski