Podstawy bezpośredniej syntezy częstotliwości DDS

| TechnikaW miarę upowszechniania się komunikacji bezprzewodowej wykorzystywane są coraz bardziej złożone modulacje, aby spełnić wymagania aplikacji w zakresie szybkości transmisji danych, ograniczenia zakłóceń, kosztów i niskiego zużycia energii. Tworzenie obwiedni takich sygnałów wymaga stabilnych źródeł sygnałów w.cz., w których można ustawiać częstotliwości i fazę przy dużej czystości widmowej. Takie parametry zapewniają źródła wykorzystujące bezpośrednią syntezę częstotliwości (DDS).

Syntezer typu DDS generuje przebiegi analogowe przy użyciu metod cyfrowych, co umożliwia programowalność przy dużym stopniu integracji (jeden chip) i małym koszcie. Dodatkowo DDS umożliwia niemal natychmiastową zmianę częstotliwości lub fazy, co czyni go głównym źródłem zegara dla zaawansowanych technik modulacji cyfrowej, takich jak FSK lub do rozpraszania widma czy pracy ze skokami częstotliwości. W rezultacie DDS szybko zastępuje pętle PLL i inne analogowe źródła RF, jednocześnie oferując wysoką stabilność i czystość sygnału wyjściowego.

Jak działa synteza DDS?

Synteza cyfrowa oparta jest na programowanym liczniku nazywanym akumulatorem fazy, który generuje rosnące liczby. Wartości te są okresowe i reprezentują chwilową fazę fali wyjściowej, od zera do 2π radianów. Są one traktowane jako wejście adresowe do pamięci próbek przekształcającej wartości w falę sinusoidalną (rys. 1). Najczęściej pamięć zawiera próbki sinusoidy, ale mogą to być także wartości przebiegów trójkątnych, piłokształtnych i innych.

Dane wyjściowe tabeli wyszukiwania faz do amplitudy są przesyłane do przetwornika cyfrowo-analogowego (DAC) i przekształcane w nim na przebieg analogowy. Ponieważ na wyjściu przetwornika występują skoki napięcia wynikające z kroku kwantyzacji, na koniec wymagany jest filtr dolnoprzepustowy tłumiący niepożądane odpowiedzi spektralne.

Akumulator fazy

Akumulator fazy jest licznikiem modulo N, który ma 2N stanów. Stan licznika zwiększany jest wraz z każdym impulsem wejściowego zegara taktującego o ustalony skok M (tzw. słowo przestrajające). Wielkość tego przyrostu określa częstotliwość fali wyjściowej.

Akumulator fazy ma na ogół od 24 do 48 bitów. Przy 24 bitach zawiera on 224 (16 777 216) stanów. Liczba ta reprezentuje całkowitą liczbę wartości faz napięcia wyjściowego od 0 do 2π radianów lub pośrednio osiągalny minimalny przyrost fazy w jednym kroku. W przypadku 24-bitowego akumulatora fazy ta rozdzielczość wynosi 3,74×10–7. W przypadku zastosowania większego akumulatora fazowego przyrost fazy staje się jeszcze drobniejszy. Jednym ze sposobów wizualizacji działania akumulatora fazowego jest spojrzenie na jego działanie jako koła fazowego (rys. 2).

Stany akumulatora są przedstawiane jako punkty leżące na kole. W tym przypadku, dla uproszczenia, akumulator ma 16 stanów. Jeśli M=1, jak na górnym schemacie, przyrost kroku na każdym zegarze wynosi jeden, a wszystkie stany są kolejno wybierane w całym okresie.

Na prawo od koła fazowego wyświetlana jest wartość analogowa odpowiadająca każdemu stanu. Analogowa fala wyjściowa składa się z jednego cyklu skwantowanej fali sinusoidalnej zawierającej szesnaście wartości. Okres drgań przebiegu wyjściowego to 16 cykli zegara taktującego (pełny obrót).

Na dolnym diagramie M=2. Sygnał analogowy składa się teraz z dwóch cykli, każdy o ośmiu amplitudach, co daje w sumie szesnaście stanów. Gdy przestrojenie M jest ustawione na dwa, częstotliwość wyjściowa jest teraz dwa razy większa niż poprzednio.

Oznacza to, że częstotliwość wyjściowa syntezera DDS jest ustalana przez wartość M i wzrasta proporcjonalnie do wartości przestrajającej. Częstotliwość próbkowania pozostaje stała dla danego zegara taktującego, czas między próbkami wyjściowymi też jest stały. Częstotliwość wyjściowa DDS zależy od wartości M. Im przestrojenie jest większe, tym w każdym cyklu wyjściowym jest mniej kroków. Słowo dostrajające może być zwiększane do momentu, aż będą tylko dwie próbki na cykl, a więc na wyjściu pojawi się połowa częstotliwości zegara taktującego. Co do zasady, synteza DDS jest ograniczona do tego zakresu przez kryterium Nyquista i równa fOUT=M·fC/2N; fC to częstotliwość zegara taktującego, a N to wielkość akumulatora fazy w bitach.

Wartość liczbowa na wyjściu akumulatora fazy, która jest chwilową fazą sygnału wyjściowego, jest wykorzystywana do sterowania przetwornikiem DAC. Liczba bitów przetwarzania przetwornika jest z reguły mniejsza od wielkości akumulatora. Ta redukcja służy do zmniejszenia komplikacji syntezera ograniczenia poboru mocy, niemniej powoduje także powstanie fałszywych składowych spektralnych w sygnale wyjściowym, które muszą być odfiltrowane.

Wyjściowy filtr dolnoprzepustowy

Przebiegi przedstawione na rysunku 2 są bogate w harmoniczne ze względu na ich schodkowy kształt. W rezultacie wymagany jest filtr dolnoprzepustowy do usunięcia niepotrzebnych harmonicznych z widma, a także innych fałszywych produktów częstotliwościowych wynikających z mechanizmu syntezy DDS.

Na przykład widmo na wyjściu DDS przy taktowaniu o częstotliwości wyjściowej mniejszej niż fC/2 pokazano na rysunku 3. Widać tam prążek fOUT wraz z widmami lustrzanymi powyżej i poniżej zegara oraz kolejne harmoniczne zegara.

Zakres częstotliwości wyjściowej generatora DDS zawiera się od 0 do limitu Nyquista, czyli fC/2. Kształt widma zbliżony do funkcji sin(x)/x to efekt kwantyzacji, a jej zera występują przy wielokrotnościach częstotliwości zegara. Aby poprawić płaskość widma i zniwelować sinusoidalny kształt, można zastosować korektor amplitudy.

Aby pozbyć się składowych niepożądanych, trzeba zastosować filtr dolnoprzepustowy z ostrym odcięciem powyżej zakresu częstotliwości DDS, żeby znacznie zmniejszyć amplitudę komponentów widmowych powyżej częstotliwości Nyquista. Z uwagi na to, że nie można uzyskać stromego nachylenia charakterystyki odcięcia, zakres częstotliwości DDS rzadko jest rozszerzany aż do częstotliwości Nyquista i z reguły zostawia się spory zapas po to, aby konstrukcja filtru nie była krytyczna.

Syntezery na bazie komercyjnych układów DDS

Zanim przystąpi się do wyboru układu syntezera, należy rozważyć niezbędną jego funkcjonalność, wymagany zakres częstotliwości wyjściowych, amplitudy i kształt sygnału, rozdzielczość i możliwości modulacji. Ważnym kryterium jest ponadto czystość sygnału, a także zakres dynamiki wolny od zafałszowań (SFDR), całkowite zniekształcenie harmoniczne (THD) i szum fazowy.

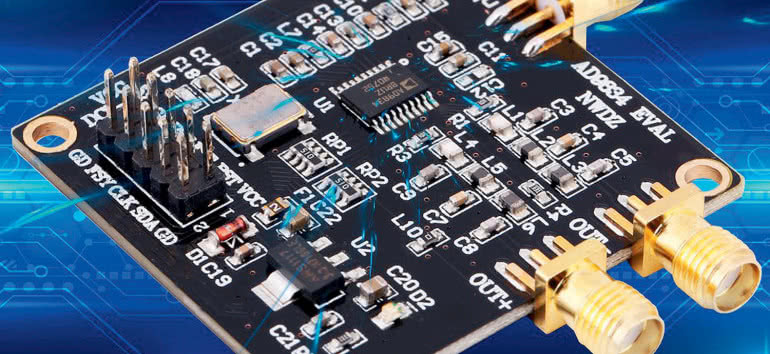

Dobrym przykładem niskomocowego DDS-a jest AD9834BRUZ-REEL7 firmy Analog Devices (rys. 4). Jest on sterowany przez trzyprzewodowy interfejs szeregowy, zużywa tylko 20 mW mocy przy zasilaniu 3 V. Na wyjściu generuje sinus, piłę i prostokąt o maks. częstotliwości do 25 MHz (zegar 50 MHz).

Akumulator fazy ma długość 28 bitów, co daje rozdzielczość 0,186 Hz przy częstotliwości taktowania 50 MHz. Szum fazowy zależy również od jakości sygnału zegara MCLK i jest pokazany jako funkcja off setu względem nośnej (rys. 5). W przypadku AD9834 szum fazowy wynosi –120 dBc/Hz przy off secie 1 kHz w stosunku do nośnej dla FOUT 2 MHz i MCLK 50 MHz.

Wbudowany w syntezer DAC ma rozdzielczość 10 bitów, a jego wąskopasmowy SFDR jest zwykle lepszy niż –78 dB.

AD9834 ma podwójne rejestry dla częstotliwości i fazy, co ułatwia tworzenie modulacji. Pamięć sinusa w ROM może być omijana w celu sterowania przetwornikiem cyfrowo-analogowym za pomocą wyjścia akumulatora fazowego w celu uzyskania przebiegu piłokształtnego, a bit znaku jest wyprowadzony na zewnętrzny pin dostarcza fali prostokątnej.

AD9834 DDS jest obsługiwany przez ADIsimDDS, internetowe, interaktywne narzędzie do projektowania, które pozwala projektantom oceniać różne konfiguracje, w tym ustalać częstotliwości wyjściowe, wartości przestrajające i zegary referencyjne (rys. 6).

Pracę z ADIsimDDS rozpoczyna się od wyboru określonego chipa. Potem wprowadza się częstotliwość zegara i żądaną częstotliwość wyjściową, a program oblicza wartość przestrojenia. Wyświetlacz pokazuje widmo wyjściowe DDS, w tym sygnał wyjściowy, harmoniczne, sygnały lustrzane DAC i zegara oraz harmoniczne zegara. Symulator filtrów można zastosować do wyjścia DDS, aby zobaczyć wpływ różnych filtrów na widmo wyjściowe.

Lepsze parametry ma AD995-2YSVZ-REEL7, który pozwala na taktowanie do 400 MHz i może wytwarzać sygnały sinusoidalne do 200 MHz przy niższym szumie fazowym i SFDR określonym na >80 dB przy 160 MHz (off set ±100 kHz) AOUT. W porównaniu bezpośrednio do AD9834, jego wąskopasmowy SFDR wynosi zwykle –70 dB przy 20 MHz, ale oczywiście zależy to od częstotliwości.

AD9952 nie ma wejścia MCLK. Zamiast tego ma wbudowany kwarcowy oscylator zegarowy z pętlą PLL, która może pomnożyć częstotliwość zegara 4–20 razy (rys. 7). Wbudowanie do wnętrza struktury zegara taktującego pozwoliło osiągnąć szum fazowy o wartości ≤ –120 dBc/Hz przy off secie 1 kHz.

AD9952 ma 32-bitowy akumulator fazy i 14-bitowy DAC. Podobnie jak poprzednik, ten chip jest sterowany także przez interfejs szeregowy.

Jeszcze szerszy zakres częstotliwości wyjściowych zapewnia układ AD9957BSVZ-REEL. Może być taktowany częstotliwością do 1 GHz i dostarczać sygnału wyjściowego do 400 MHz. Ma 32-bitowy akumulator fazy i 14-bitowy szybki przetwornik cyfrowo-analo- Digi-Key Electronics https://www.digikey.pl/ gowy, co pozwala wykorzystać DDS do pracy jako modulator kwadraturowy generujący komponenty fazy IQ z użyciem 8 rejestrów fazy/częstotliwości. Dostępny jest ponadto opcjonalny filtr odwrotny SINC w celu kompensacji omówionego wcześniej kształtu widma sin(x)/x.

Podsumowanie

Syntezery DSS zapewniają dużą stabilność, szybkość reakcji i powtarzalność w generowaniu sygnałów w.cz., oferując wiele kształtów przebiegów wyjściowych i zaawansowane możliwości modulacji, w tym także takie ze skokową zmianą częstotliwości i fazy. Dostępne narzędzia projektowe i zestawy upraszczają ich wybór i integrację.

Rich Miron, Digi-Key Electronics

https://www.digikey.pl/