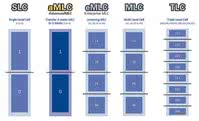

Aby zapewnić klientom osiągnięcie optymalnej niezawodności, wydajności i stosunkowo niskiego całkowitego kosztu posiadania rozwiązania pamięci masowej na NAND Flash, firma ATP wprowadziła na rynek nowy typ pamięci "aMLC" (advancedMLC). Stanowią one w pewnym sensie alternatywę dla układów SLC z punktu widzenia kosztu zakupu oraz mocną alternatywę dla pamięci MLC pod względem zapewnienia lepszej żywotności. W artykule wyjaśniono architekturę aMLC, a przede wszystkim zalety, które aMLC wnosi do urządzeń pamięci NAND Flash w porównaniu z technologią MLC jako jej znacznie żywotniejszy następca.

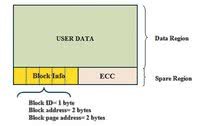

Każdy chip NAND Flash podzielony jest na bloki, a każdy blok składa się z wielu stron. Blok jest minimalną jednostką dla operacji kasowania, podczas gdy strona jest minimalną jednostką dla operacji odczytu lub zapisu (rys. 2). Każda strona może zostać rozdzielona na region danych i region bloków zapasowych. Region zapasowy to miejsce, gdzie są przechowywane informacje o ECC (Error Correction Code) i parzystości, a także pokrewne informacje o F/W, takie jak tabela mapowania i systemu plików. Dane użytkownika mogą być zapisywane tylko w obszarze danych (rys. 3).

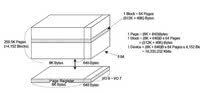

Biorąc rysunek 4 jako przykład, widać, że pamięć składa się z 4152 bloków. Na każdy blok zawiera 64 strony. Rozmiar regionu zapasowego to 640 bajtów. Występuje on co 8 kB istniejących w obszarze danych.

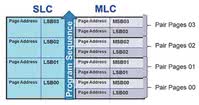

Rysunek 5 pokazuje różnice pomiędzy sekwencją programowania Flash SLC i MLC. W chipach MLC jedna komórka zawiera dwa bity danych, co jest realizowane przez podział zakresu ładowania pojemności bramki tranzystora MOSFET stanowiącego komórkę pamięci na 4 oddzielne podzakresy, a każdej parze bitów danych przyporządkowane jest odpowiednie napięcie VTH woltów. Stan 10 może być reprezentowany wzorem danych LSB strony "0" i strony MSB "1". Analogicznie, stan 01 może być reprezentowany wzorem danych "0" LSB strony i "1" na stronie MSB. Przebieg programu z MLC ma podążać zgodnie z kolejnością: LSB->MSB->LSB->MSB... i tak dalej.

Rysunek 6 pokazuje stany dystrybucji napięcia VTH dla komórki w technologii MLC w jednej stronie/sektorze. Przy założeniu, że liczba komórek z każdego wzoru danych w jednej stronie/sektorze jest równa, poszczególne stany VTH, znane jako 11, 10, 00 i 01, można zobrazować rozkładem krzywej Gaussa. Należy zauważyć też, że margines zakłóceń jest niemal identyczny między jednym stanem VTH a drugim. Aby zwiększyć niezawodność technologii MLC, zwłaszcza z ograniczoną liczbą cykli programowania/kasowania (3000 razy), margines zakłóceń jest najważniejszym czynnikiem, aby to móc wykonać. Gdy jest on lepszy, liczba cykli P/E może również znacznie się poprawić.

Przy użyciu zaawansowanego oprogramowania firmware producenta nośnika, 4 stany w chipie MLC są zamieniane programowo na 2. Dane o kodach 10 i 01 są przenoszone do 1 i 0, a większy margines zakłóceń między 1 i 0 skutkuje większą liczbą cykli P/E dla pamięci tego typu i lepszym czasem przechowywania danych (parametr Data Retention).

Porównanie pamięci MLC, eMLC oraz aMLC w zakresie trzech kluczowych parametrów: żywotność, wydajność i czas przechowywania danych, przedstawiono na rysunku 7 Zazwyczaj wytrzymałość bloku SLC wynosi od 60 tys. do 100 tys. cykli programowania, a żywotność typowego chipa klasy MLC osiąga wartość około 1,5 ~ 3 tys. cykli.

Żywotność układów klasy Enterprise MLC (eMLC) to ok. 10 tys., podczas gdy stosunek wydajności do data retention w pamięciach eMLC stanowi niestety mniej niż połowę w porównaniu z konsumenckimi pamięciami MLC. W porównaniu do powyższych typów pamięci zalety aMLC są znaczne. Układy aMLC firmy ATP zapewniają minimalną żywotność 40 tys. cykli, a kompromis wydajności do data retention (jak w eMLC) nie występuje.

Podsumowanie

Rozwiązanie firmy ATP aMLC zapewnia efektywność kosztową w połączeniu z dużą żywotnością, wysoką wydajnością i wysoką niezawodnością dla urządzeń pamięci masowej. Pamięci aMLC wykorzystywane są do budowy nośników SSD 2,5", SlimSATA i mSATA.

Marcin Malinowski, Product Manager

CSI Computer Systems for Industry

www.csi.pl