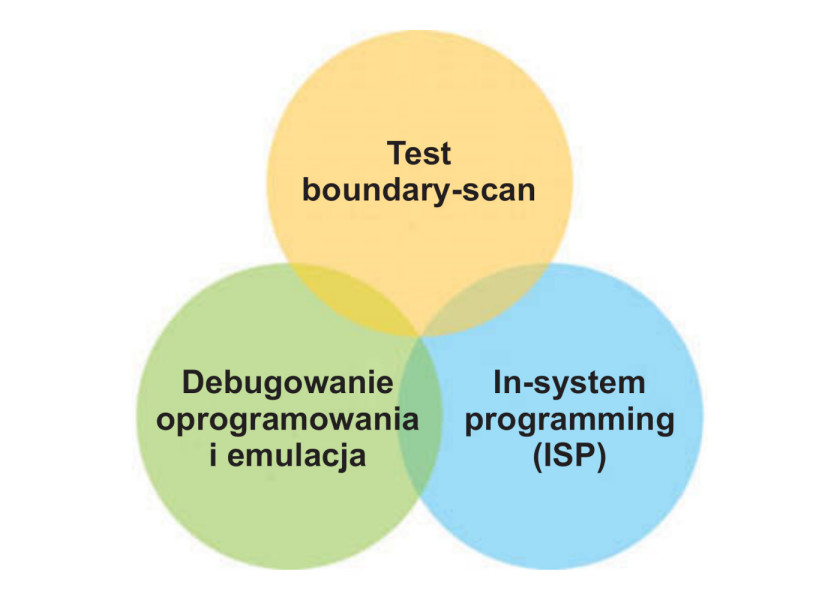

Narzędzia do debugowania i programowania są zwykle powiązane z JTAG w ten sposób, że wykorzystują 4-przewodowy protokół komunikacyjny w tym standardzie, a więc pokrywają jeden niewielki aspekt tego rozwiązania. Tymczasem cała reszta niesie ze sobą znacznie większą funkcjonalność. Te cztery linie sygnałowe, znane pod wspólną nazwą Test Access Port (testowy port dostępowy) albo w skrócie TAP, są częścią standardu IEEE 1149.1. Został on opracowany w celu dostarczenia rozwiązań do testowania połączeń, na zmontowanych płytkach drukowanych (PCBA) bez konieczności zapewnienia fizycznego dostępu do kontaktów elektrycznych (za pomocą sprężystych szpilek kontaktowych, tzw. łoża fakira) lub punktów kontaktowych dodanych do projektu w liczbie niezbędnej do przeprowadzenia testu funkcjonalnego. TAP został zaprojektowany do współdziałania z zaszytymi w układach scalonych specjalnymi rejestrami, które zostały dodane właśnie w celu umożliwienia testowania połączeń za pomocą JTAG. Korzyści wynikające z istnienia TAP bardzo szybko dostrzegli producenci chipów i wykorzystali to rozwiązanie do rozwijania funkcjonalności związanych z dostępem do pamięci wewnętrznej w układach programowalnych i debugowania.

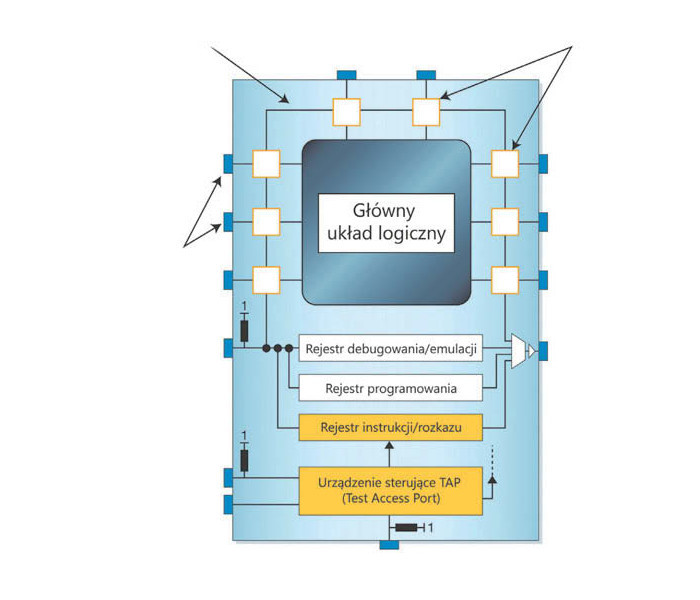

Główny rejestr, jaki został dodany do układu specjalnie do celów testowania za pomocą JTAG, jest nazywany rejestrem boundary-scan (BSR).

Jak sama nazwa wskazuje, jego poszczególne bity odpowiadają sygnałom pojawiającym się na granicy fizycznej układu, a więc między jego częścią funkcjonalną a pinami, poprzez które jest on podłączony do płytki. Stąd bardzo często testowanie z użyciem JTAG jest określane jako boundary-scan (skanowanie po ścieżce krawędziowej, czyli brzegu układu).

Rejestry boundary-scan mogą pracować w dwóch trybach. W trybie funkcjonalnym nie mają one żadnego wpływu na działanie układu. Tak dzieje się, gdy układ pracuje normalnie. W trybie testowym odłączają one część funkcjonalną urządzenia od pinów wyjściowych, stąd poprzez aktywację trybu testowego mogą one być wykorzystane do kontroli sieci połączeń elektrycznych na PCB i monitorowania pojawiających się tam wartości sygnałów.

Odłączenie pinów od wnętrza układu sprawia, że testy połączeń z użyciem boundary-scan stają się znacznie łatwiejsze od tradycyjnych testów funkcjonalnych, ponieważ do badań nie jest wymagana żadna dodatkowa konfiguracja urządzenia albo jego rozruch. Dostęp do mechanizmu kontroli i monitorowania wszystkich linii sygnałowych jest możliwy z poziomu 4-przewodowego TAP. Innymi słowy, JTAG znacznie zmniejsza wymagania co do fizycznego dostępu wymaganego do przetestowania zmontowanej płytki drukowanej.

Zastosowania

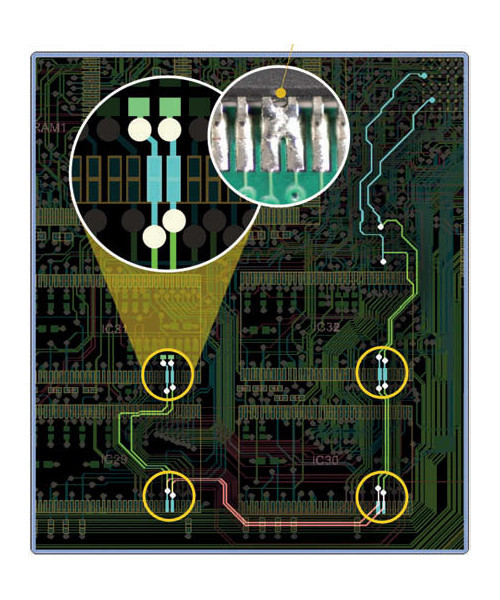

Istnieją dwie główne metody użycia techniki boundary-scan do testowania PCB. Pierwszy to testowanie połączeń, szczególnie przydatny do wykrywania zwarć. Jest on oparty wyłącznie na możliwościach kryjących się w JTAG-u, sieci połączeń na płytce drukowanej oraz – w przypadku produktów XJTAG – także na funkcjonalności istniejącej logiki. Drugi sposób rozszerza te możliwości za pomocą uaktywnionych przez JTAG układów do komunikowania się z obwodami peryferyjnymi bez rejestrów JTAG, takimi jak pamięci RAM DDR i Flash.

Zaawansowany test XJTAG

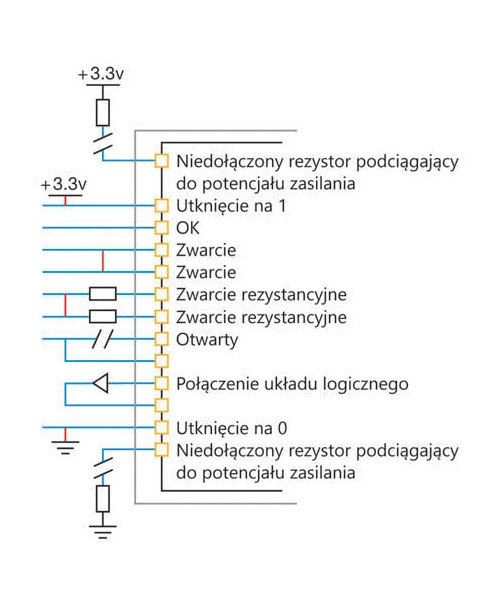

Testowanie układu z użyciem JTAGa sprawdza, czy sieć połączeń na płytce drukowanej odpowiada dokładnie temu, co określa projekt. Testy pozwalają wykryć zwarcia, przerwy, poprzez zadawanie wartości testowych na jednym końcu i odczyt wartości docelowych na drugim końcu. Różnice w sygnaturach wyjściowych i wejściowych świadczą o błędach. W taki sposób można też zapewnić brakujące rezystory podciągające. Zaawansowany test połączeń oferowany przez XJTAG dodatkowo pozwala na wykrycie potencjalnych zwarć za rezystorami szeregowymi a także na testowanie w otoczeniu układów logicznych, których zachowanie można opisać tablicą prawdy. To ważna i unikalna cecha rozwiązania firmy XJTAG.

A co z układami, które nie współdziałają z JTAG?

Wiele chipów w tym mikroprocesory i macierze FPGA zwykle współdziałają z JTAG, niemniej zawsze znajdą się jakieś wyjątki. Pamięci DDR, SDRAM, SRAM, pamięć Flash, układy wejścia/ wyjścia (MDIO), ethernetowe PHY, interfejsy SPI oraz czujniki temperatury z wyjściem I²C, zegary czasu rzeczywistego, przetworniki analogowo-cyfrowe (ADC) i przetworniki cyfrowo-analogowe (DAC) to tylko kilka przykładów półprzewodników bez JTAG. Test poprawności połączeń w tym przypadku też będzie informować o zwarciach, jednak nie pozwoli sprawdzać przerw w obwodach. Można to obejść częściowo z wykorzystaniem komunikacji z takim nieobsługiwanym układem z poziomu chipa obsługującego JTAG. Przykładem może być zapis danych testowych do pamięci z użyciem JTAG i potem odczyt weryfikacyjny.

Ile pracy wymaga stworzenie testów XJTAG dla urządzenia?

Przy użyciu bibliotek standardowych dla podzespołów nieobsługujących JTAG, które dostarcza firma XJTAG, można szybko stworzyć zestaw testów bez konieczności pisania własnego kodu. Biblioteki zawierają modele dla wszystkich typów części od rezystorów przez bufory i bramki do pamięci DDR3. Ponieważ skanowanie ze ścieżką krawędziową niezależnie steruje pinami w chipach, ten sam model może być wykorzystywany niezależnie od platformy sprzętowej interfejsu.

Aby uruchomić jakikolwiek test boundary- scan, niezbędne jest ponadto posiadanie informacji o komponentach znajdujących się na płytce. Informacje te zawierają pliki BSDL (języka opisu dla boundary- scan), które dostarczają producenci podzespołów.

Zaletą testowania z wykorzystaniem JTAG jest to, że niezbędna część sprzętowa sprowadza się do prostego interfejsu. Nie trzeba sondy typu fl ying probe, AOI, czy X-Ray ani łoża fakira. Testowanie takie nie wymaga też miejsca i łatwo je wdrożyć dla prototypów. Co więcej, systemy testowe opracowane na tym wczesnym etapie cyklu projektowego mogą być łatwo ponownie użyte oraz rozszerzone, tworząc wersje produkcyjne.

BGA i NRE pokazują możliwości JTAG

Coraz większa liczba chipów jest wytwarzana w obudowach BGA (Ball Grid Array), czyli do montażu SMT w obudowie bez wyprowadzeń. Z uwagi na to, że połączenia są tutaj ukryte pod obudową układu scalonego, nie można korzystać z tradycyjnych metod testowania (np. głowic szpilkowych). Ale za pomocą prostego interfejsu 4-żyłowego JTAG możliwe jest sprawdzenie połączeń bez wymaganego dostępu fizycznego do pinów BGA.

Z kolei NRE (jednorazowe koszty inżynierskie) to opłaty ponoszone na przygotowanie testów. W klasycznych rozwiązaniach mogą być one wysokie. W wielu przypadkach używając JTAG można je znacznie ograniczyć lub wyeliminować.

W przypadku produkcji małoseryjnej koszty opracowania oprzyrządowania testowego są szczególnie dokuczliwe. W tych przypadkach tylko fl ying probe jest akceptowalną kosztowo metodą, niestety testowanie w ten sposób jest zwykle bardzo czasochłonne. W takiej sytuacji testowanie metodą JTAG wygrywa szybkością oraz optymalnymi kosztami.

Mniejsze koszty prac rozwojowych

Mikroprocesory oraz FPGA komunikują się z układami peryferyjnymi na wiele sposobów, stąd tradycyjne testy funkcjonalne wymagają kosztownego dopasowania do wymagań klienta każdej nowej wersji płytki drukowanej. Testowanie z XJTAG zmniejsza koszty, ponieważ bazuje za każdym razem na takim samym interfejsie JTAG. Kolejną obniżkę zapewnia prostszy proces realizacji testów na etapie produkcji.

Doskonała diagnostyka usterek

Boundary-scan pozwala też na diagnostykę serwisową i pomaga realizować szybkie naprawy. Oprogramowanie XJTAG daje również możliwość wskazania lokalizacji usterki.

Wiele płytek, które normalnie trafiłyby do kosza, daje się w ten sposób naprawić, tym bardziej że nie jest wymagane, aby układy elektroniczne na płytce działały. Testowanie XJTAG nie wymaga ich aktywacji, a część komponentów takich jak pamięci daje się przetestować bez konieczności uruchamiania mikroprocesora, sygnału zegarowego itd.

Warsztaty

FlowCAD Poland, który jest dystrybutorem XJTAG w Polsce, zaprasza na organizowane w wybranych terminach warsztaty pozwalające na zapoznanie się z opisaną technologią w formie całodziennego spotkania, podczas którego uczestnicy mają dostęp do stanowiska laboratoryjnego XJTAG. Warsztaty są prowadzone przez inżynierów firmy XJTAG. Zainteresowanie osoby zachęcamy do sprawdzania na naszej stronie www.FlowCAD.pl dat następnych organizowanych warsztatów.

Tomasz Górecki

FlowCAD

tel. 58 732 74 77, www.FlowCAD.pl