Napięcia zasilające o parametrach wymaganych przez poszczególne sekcje i podzespoły na płytce zapewniają stabilizatory napięcia. Są one rozprowadzane za pośrednictwem sieci dystrybucji zasilania – PDN tworzą wszystkie połączenia od wyjść stabilizatorów do zacisków komponentów elektronicznych, pozostałych elementów i części PCB, jak przelotki, ścieżki, płaszczyzny zasilania i masy.

Linie PDN są prowadzone przez całą płytkę drukowaną i podłączonych jest do nich wiele podzespołów. Konsekwencją tego jest ich narażenie na zaburzenia generowane przez komponenty PCB, szczególnie dokuczliwe w projektach high-speed.

Ich sprzęganie się z PDN negatywnie wpływa na pracę urządzenia na kilka sposobów. Przede wszystkim zakłócenia powyżej dopuszczalnego poziomu zmieniają napięcia docierające do odbiorników. To powoduje, że podzespoły na PCB, zwłaszcza układy scalone, mogą działać nieprawidłowo, jeśli zostaną przekroczone wartości progowe ich napięć zasilających.

Nawet jeśli PDN zapewnia napięcia w granicach tolerancji, zakłócenia z sieci dystrybucji zasilania mogą jednak powodować inne problemy, sprzęgając się z liniami sygnałowymi i liniami zasilania, a za ich pośrednictwem z wejściami stabilizatorów napięcia, przenosząc się na ich wyjścia. Są też być źródłem problemów z kompatybilnością elektromagnetyczną. Dlatego trzeba eliminować zaburzenia PDN. Zachowując w projekcie płytki drukowanej integralność sieci zasilania zyskujemy pewność, że napięcia będą dystrybuowane w granicach tolerancji i że unikniemy innych niepożądanych zjawisk.

Co zakłóca PDN?

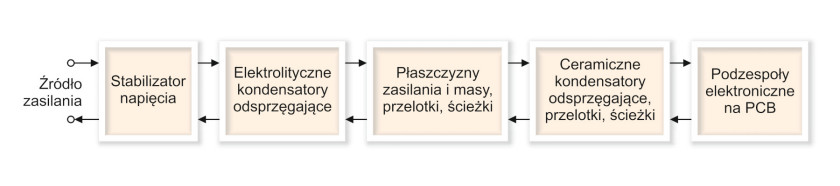

Na rysunku 1 przedstawiono uproszczony schemat blokowy PDN. Główne komponenty sieci dystrybucji zasilania PCB to: stabilizatory napięcia, ich kondensatory, przeważnie elektrolityczne (tantalowe, aluminiowe, polimerowe), płaszczyzny zasilania oraz masy, przelotki i ścieżki, kondensatory odsprzęgające, zazwyczaj ceramiczne, przelotki oraz ścieżki do zacisków zasilania i masy podzespołów elektronicznych. Żeby ograniczyć zaburzenia zakłócające PDN należy na tej podstawie przeanalizować ich potencjalne źródła i przyczyny.

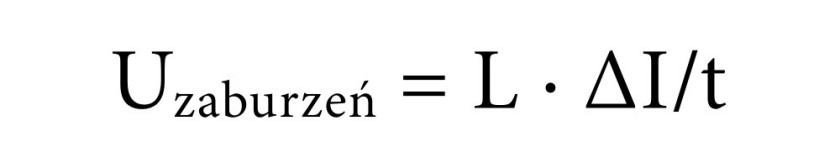

Chcąc oszacować spadek napięcia w sieci dystrybucji zasilania trzeba uwzględnić jej impedancję. Oprócz tego należy wziąć pod uwagę to, że w układach cyfrowych, wewnątrz i na ich zaciskach, przy przełączaniu z jednego poziomu logicznego na drugi, prąd pobierany z zasilania także się zmienia. Ta zmiana zachodzi bardzo szybko – czas narastania i opadania mieści się typowo w przedziale od poniżej jednej do kilku nanosekund i indukuje na zaciskach układu napięcie:

gdzie L jest indukcyjnością pętli utworzonej przez ścieżkę sieci zasilania i uziemienia, czyli PDN, tr – czasem narastania przy przełączaniu poziomu logicznego, a ΔI zmianą prądu pobieranego przez układ scalony z zasilania. Z tego równania można wyciągnąć kilka wniosków.

Im większe będzie ΔI, tym większe będzie napięcie zaburzeń. Zatem jeżeli jednocześnie nastąpi n przełączeń stanu logicznego, w jednym albo większej liczbie układów podłączonych do tej samej linii zasilania, w równaniu trzeba będzie skorygować składnik ΔI/tr na n·ΔI/tr, w związku z czym n razy większe będzie również Uzaburzeń. Ma to szczególne znaczenie w przypadku takich podzespołów jak układy FPGA, mikrokontrolery, pamięci czy układy ASIC, które po pierwsze mają wiele wejść i wyjść, a po drugie złożoną strukturę wewnętrzną i mogą wykonywać proste lub złożone programy. Oznacza to ogromną liczbę, z dużym prawdopodobieństwem, jednoczesnych przełączeń stanów logicznych, a zatem silne zaburzenia przenoszone na PDN.

Są też one tym większe, im mniejsza jest wartość czasu narastania tr, obecnie zaś parametr ten jest sukcesywnie zmniejszany, w odpowiedzi na rosnące potrzeby w zakresie szybkości przesyłu oraz przetwarzania danych.

Taka zależność łączy także Uzaburzeń oraz indukcyjność L, która w tym przypadku ma wiele źródeł. Przede wszystkim każda pętla w obrębie PDN (wewnątrz układu scalonego, od wewnątrz do jego zacisków, od zacisków do padów PCB, ścieżek, przelotek, od kondensatorów odsprzęgających do płaszczyzn zasilania i masy, a w końcu do stabilizatorów napięcia) ma indukcyjność pasożytniczą proporcjonalną do jej obszaru, zwykle rzędu nH. Ponadto kondensatory odsprzęgające – zarówno elektrolityczne, jak i ceramiczne – nie są podzespołami idealnymi i też mają indukcyjność, którą charakteryzuje parametr ESL (Equivalent Series Inductance). Typowo wynosi on kilkadziesiąt nH w przypadku kondensatorów elektrolitycznych i kilka nH w kondensatorach ceramicznych. Warto od razu zaznaczyć, że składnik L równania) jest jedynym, na które projektant PDN ma w praktyce wpływ.

Projektowanie PDN

Przystępując do projektowania sieci dystrybucji zasilania PCB należy przeanalizować, w jaki sposób impedancja PDN (ZPDN) będzie się zmieniać wraz z częstotliwością zaburzeń w jej spodziewanym zakresie. W tym celu należy wyznaczyć docelową impedancję ZTPDN.

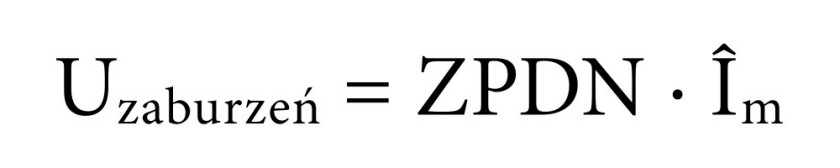

Jeśli Imax jest maksymalnym prądem pobieranym z zasilania, ten w zależności od tego, ile stanów logicznych jest jednocześnie przełączanych i jak szybko to następuje, będzie się zmieniał od 0 do Imax. Widmo prądu zaburzeń z kolei obejmować będzie zakres częstotliwości od 0 do fm = 0,5/tr, a amplituda sinusoidalnego przebiegu prądu zaburzeń przy dowolnej częstotliwości w tym paśmie będzie mniejsza niż Îm = ½ Imax. Napięcie zaburzeń opisuje wówczas równanie:

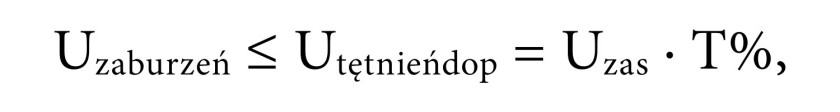

To napięcie zaburzeń pojawi się jako napięcie tętnienia na linii zasilającej Uzas. Aby układy scalone podłączone do niej działały prawidłowo musimy upewnić się, że Uzaburzeń nie przekracza dopuszczalnego napięcia tętnienia napięcia zasilania komponentu. Można to zapisać:

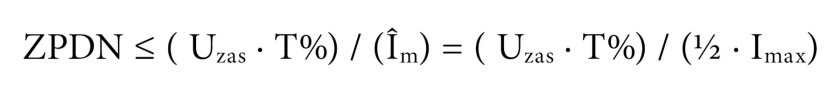

gdzie T% to wspominane tętnienia (wyrażone w procentach). Stąd:

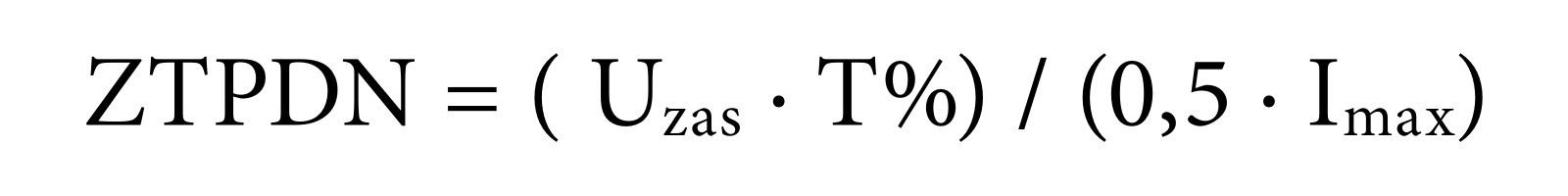

oraz

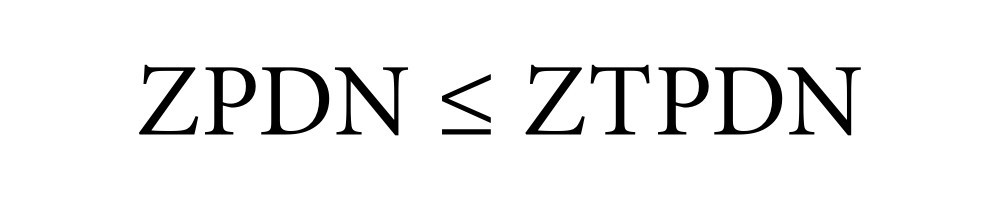

W związku z tym impedancja sieci dystrybucji zasilania PCB w całym zakresie częstotliwości zaburzeń powinna spełniać warunek:

Podsumowując, procedura projektowania PDN powinna obejmować następujące kroki: najpierw należy określić największą częstotliwość zaburzeń fm = 0,5/tr, potem należy obliczyć docelową impedancję ZTPDN dla każdej linii zasilającej. Następnie, korzystając z oprogramowania, trzeba przygotować wykres impedancji w funkcji częstotliwości w zakresie od 0 do fm, sprawdzając jak na ten przebieg i możliwość spełnienia warunku 6 wpływa na projekt PDN. Trzeba tu pamiętać, że na tym etapie nie mamy już wpływu na podzespoły funkcjonalne PCB, jak układy scalone, ale impedancję sieci dystrybucji zasilania możemy kontrolować dobierając komponenty systemu zasilania, czyli stabilizatory napięcia i kondensatory odsprzęgające.

Jaki wybrać kondensator i projektować ścieżki?

W przypadku kondensatorów elektrolitycznych typowe częstotliwości rezonansowe mieszczą się w zakresie od kilku kHz do 100 kHz, dlatego w analogicznym przedziale są one w stanie utrzymać niską impedancję PDN. Ich ESL z kolei wynosi od 10 do 20 nH. Ich pojemność zaleca się zatem dobrać tak, żeby ich impedancja była mniejsza niż ZTPDN przy 1 kHz. Warto także w zakresie ich wyboru przestrzegać kilku wskazówek praktycznych. W przypadku kondensatorów tantalowych nie zaleca się korzystania z tych ze zbyt małą wartością parametru ESR – optymalnie powinien być spełniony warunek ESR ≈ 0,5 ZTPDN. Ich pojemność z kolei powinno się dobrać tak, żeby ich impedancja przy niższej częstotliwości rezonansowej była mniejsza niż √(ZTPDN ² – ESR²).

Powyżej górnej częstotliwości rezonansowej kondensatorów elektrolitycznych dominuje składowa indukcyjna ich impedancji, która w związku z tym będzie sumarycznie większa niż ZTPDN. Dlatego należy skorzystać również z ceramicznych kondensatorów odsprzęgających. Ich częstotliwości rezonansowe mieszczą się w zakresie od kilku 100 kHz do kilku 100 MHz i to w tym zakresie odgrywają one dominującą rolę w kontrolowaniu impedancji PDN i utrzymywaniu jej poniżej ZTPDN. Charakteryzuje je także bardzo niskie ESR – rzędu kilku miliomów do kilku dziesiątek miliomów. Gdy z kolei chodzi o ESL należy wziąć pod uwagę nie tylko wartość tego parametru kondensatora, ale również indukcyjność pętli przelotek i ścieżek łączących wyprowadzenia zasilania i masy układu scalonego z kondensatorami oraz z płaszczyznami zasilania i masy.

Jeśli chodzi o indukcyjność pętli ścieżek zaleca się by: ścieżki wykonywać jako możliwie najkrótsze (ceramiczne kondensatory odsprzęgające należy umieścić jak najbliżej układu scalonego) oraz szerokie (zapewni to małą wartość impedancji charakterystycznej) i zapewnić jak najmniejszy odstęp między warstwą komponentów a płaszczyzną uziemienia i zasilania (to też gwarantuje małą wartość impedancji charakterystycznej). Zasady projektowe powszechnie przyjmowane w przypadku przelotek to z kolei: wykonywanie ich z możliwie dużą średnicą i blisko siebie.

Monika Jaworowska