TSMC zmniejsza skalę przedsięwzięcia inwestycyjnego i uruchomi produkcję w technologii 40nm o mniejszej przepustowości niż to miało miejsce przy wprowadzaniu poprzednich generacji procesów. Decyzja ta podyktowana jest coraz mniejszą liczbą klientów firmy, decydujących się na rozpoczęcie produkcji układów w najnowocześniejszych procesach technologicznych. Klienci TSMC, pochłonięci kosztami opracowywania architektury oraz wytwarzania układów, niechętnie angażują się w kosztowny rozwój technologii następnej generacji. Trend ten widoczny był już w przypadku przejścia do procesu technologicznego 45nm, kiedy to zainteresowanie okazało się mniejsze niż początkowo zakładano. Aby zmniejszyć ryzyko własne, TSMC rozpocznie produkcję stopniowo.

Według analityków, taka polityka firmy jest dowodem, iż producenci półprzewodników niechętnie biorą na siebie ciężar utrzymania branży w zgodzie z prawem Moore’a. Widoczne jest zmniejszenie skali, w jakiej wprowadzane są innowacje w dziedzinie technologii produkcji. W porównaniu z latami dziewięćdziesiątymi ubiegłego wieku, kiedy to producenci półprzewodników, korzystając z popularności modelu działalności typu fabless, niezależnie od koniunktury chętnie wprowadzali nowe generacje procesów technologicznych na szeroką skalę, branża wydaje się dziś ostrożniej podchodzić do zmian. Obecnie większość firm zajmujących się wytwarzaniem półprzewodników nadal chce oferować najnowocześniejszą generację procesów, jednak są one wprowadzane w postaci linii produkcyjnych o mniejszej produktywności. Stanowi to zabezpieczenie przed niepewną sytuacją na rynku. Producenci boją się powtórzenia sytuacji, gdy inwestycja w nowe hale produkcyjne nie zwracała się z powodu niedostosowania możliwości produkcyjnych do wymagań rynku.

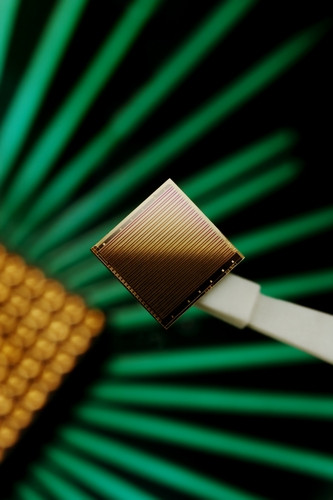

Cechy procesu 40nm

- dostępne wersje ogólnego przeznaczenia (40G) oraz małej mocy (40LP) |

TSMC nadal innowacyjne

Pierwszych płytek półprzewodnikowych wytworzonych w procesie 40nm możemy oczekiwać w drugim kwartale tego roku. Według przedstawicieli firmy, produkcja będzie w pełni dostępna dla zleceniodawców pod koniec 2008 roku. Zdaniem większości obserwatorów branży, omawiany wymiar charakterystyczny jest tylko krokiem w celu wprowadzenia standardu opartego na wymiarze technologicznym 32 nm. TSMC zapowiada dostępność tej technologii pod koniec 2009 roku, czyli około dwa lata po wprowadzeniu procesu 45nm. Wydaje się, iż to właśnie na badaniach nad nią firma zamierza skupić swoje prace badawcze, podczas gdy proces 40nm ma wypełnić lukę na rynku, celując w potrzeby najbardziej wymagających klientów. Ponadto, ma to udowodnić, iż TSMC jest nadal liderem innowacyjności w branży. Dodatkowo, plany firmy obejmują podjęcie prac badawczych nad technologią 22nm.

Przerwa pomiędzy technologiami 32nm a 45nm jest o 8 miesięcy dłuższa niż w przypadku 45nm a 65nm, co każe przypuszczać, iż 40nm odegra większą rolę niż poprzednia generacja przejściowa o wymiarze charakterystycznym 55nm. TSMC zamierza wprowadzić dwie wersje tego procesu, 40G, ogólnego przeznaczenia, oraz 40LP, zoptymalizowaną na niski pobór mocy. Nowa technologia pozwoli na 2,65 razy większe upakowania tranzystorów w stosunku do 65nm. Przykładowo, komórka pamięci SRAM w tym wypadku będzie charakteryzować się wymiarem 0,242 μm2. W zakresie oszczędności energii uzyskano poprawę o 15% w stosunku do procesu 45nm. Technologia 40nm wykorzystuje litografię immersyjną o długości fali światła 193nm oraz materiały dielektryczne. Logika zapewnia wsparcie dla zastosowań bezprzewodowych w postaci LPG (low-power, triple-gate oxide).

Aby zredukować koszta własne, firma TSMC rozwija projekt w kooperacji z innymi firmami. Poza wsparciem dla metod opracowanych przez TSMC, proces 40nm wykorzystuje własność intelektualną firm trzecich oraz narzędzia EDA.

Jacek Dębowski