Jednym z kluczowych wymagań projektantów współczesnych systemów embedded jest uzyskanie przewidywalnego czasowo zachowania (deterministycznego). W praktyce sprowadza się to do skrócenia czasu reakcji na zmiany zachodzące w zarządzanych procesach: natychmiastowej odpowiedzi na dane wejściowe pochodzące z czujników, portów komunikacyjnych czy interfejsu użytkownika. Efekt ten można uzyskać przez zwiększanie mocy obliczeniowej układów, jednak jest to metoda nieoptymalna. Aby uniknąć programowej obsługi podstawowych procesów, Microchip stosuje w swoich mikrokontrolerach peryferia pracujące niezależne od rdzenia (Core Independent Peripherals). Nowością w tej technologii jest programowalny układ bramek logicznych (Configurable Logic Block), który został zintegrowany w nowej rodzinie 8-bitowych mikrokontrolerów producenta, układach PIC16F131xx.

Parametry i peryferia

W poniższej części testu omówiono rozwiązania CIP i CLB oraz to, w jaki sposób pozwalają zachować moc obliczeniową układów na potrzeby zarządzania aplikacją, podczas gdy same przejmują prostsze zadania (obsługa przycisków, niektórych wyświetlaczy, przeliczanie wartości pobieranych z przetworników). Jednak w pierwszej kolejności warto przyjrzeć się specyfikacji oraz budowie mikrokontrolerów PIC16F131xx.

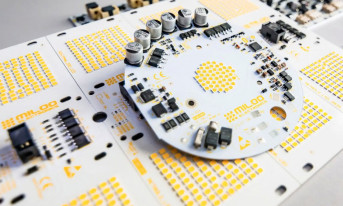

Omawiane układy zostały oparte na klasycznej, 8-bitowej architekturze harwardzkiej. Występują w wersjach do montażu THT oraz SMD w obudowach DIP, DFN, SSOP, TSSOP, SOIC oraz VQFN z 6, 12 lub 18 liniami IO. Dużym atutem układów jest szeroki zakres napięcia zasilania: od 1,8 do 5,5 V. Przy taktowaniu 32 MHz minimalny czas wykonania instrukcji wynosi 125 ns. Dostępne układy mają od 256 B do 1024 B pamięci SRAM oraz do 14 kB pamięci programu (Flash).

Dla projektantów przygotowano bogaty wybór układów peryferyjnych, takich jak generatory PWM, liczniki/timery 8- i 16-bitowe, kontroler magistrali szeregowej EUSART, port MSSP (Host Synchronous Serial Port) mogący pracować w trybie obsługi interfejsu I2C lub SPI, konfigurowalne komparatory o skróconym czasie reakcji (50 ns), 8-bitowy przetwornik cyfrowo-analogowy (DAC) oraz 10-bitowy przetwornik analogowo-cyfrowy z możliwością realizacji obliczeń (ADCC).

Core Independent Peripherals

Peryferia pracujące niezależnie od rdzenia (CIP, Core Indpendent Peripherals) są cechą charakterystyczną rodzin PIC i AVR. Pozwalają one realizować pewne zadania (np. komunikację z czujnikami) w tle, bez wykorzystania mocy obliczeniowej procesora, która jest dostępna w całości do celów realizacji głównego programu, co prowadzi do zmniejszonego zużycia energii oraz uproszczenia programu. Takie peryferia mogą służyć do obsługi transmisji danych (I2C, CAN, USB), odmierzania czasu (timery), generowania sygnałów PWM czy pracy z sygnałami analogowymi (ADC, OP-AMP, DAC).

Układ CLB

Najważniejszą innowacją wprowadzoną w mikrokontrolerach PIC16F131xx jest umieszczenie w ich strukturze niezależnych, konfigurowalnych elementów logicznych (ze względu na sposób ich działania układ ten zalicza się do peryferiów CIP). Określa się je skrótem CLB (Configurable Logic Block) i służą one zapewnieniu bezpieczeństwa i natychmiastowego czasu reakcji systemu dzięki realizacji sprzętowej. CLB oparto na strukturach znanych z układów FPGA, tj. oferujących możliwie najkrótszy czas przetwarzania sygnałów wejściowych. CLB działa z użyciem podstawowych bramek logicznych, które mogą być przez projektanta dowolnie konfigurowane na potrzeby konkretnej aplikacji. Dodatkowo CLB pozwalają zminiaturyzować docelowe urządzenie, bo ograniczają liczbę wymaganych elementów zewnętrznych.

Dostępne typy bramek logicznych

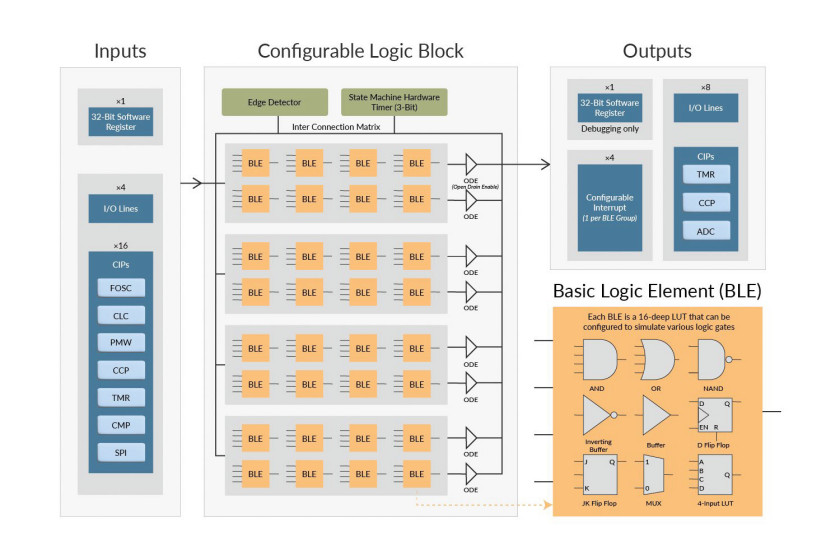

Na strukturę CLB składają się dyskretne komponenty tworzące 32 jednakowe komórki, z których każda stanowi tzw. podstawowy element logiczny (BLE, Basic Logic Element). Wszystkie z nich są taktowane zboczem narastającym sygnału CLBCLK. W zależności od potrzeb komórka symuluje jeden, określony na etapie programowania, układ logiczny. Może to być:

- bramka AND/OR (maks. 4 wejścia),

- bramka NAND/NOR (2 wejścia),

- bramka XOR/XNOR,

- inwerter lub bufor,

- przerzutnik typu D lub J-K,

- konfigurowalna tablica LUT (Lookup Table, do 4 wejść).

Sygnały wejściowe i wyjściowe dla tej logiki mogą pochodzić z 32-bitowego rejestru dostępnego z poziomu programu, reprezentować stan na liniach I/O mikrokontrolera, a także z generatora PWM, timera/licznika, a nawet bufora magistrali SPI. Wyjścia bramek można podłączyć do przetwornika, timera, fizycznych linii wyjściowych (pinów) układu. Opcjonalnie: każda z 4 grup komórek może wygenerować przerwanie obsługiwane przez program. Wyjścia komórek BLE są 3-stanowe.

Podsumowując, można powiedzieć, że projektant otrzymuje do dyspozycji w pełni konfigurowalną strukturę zbliżoną do FPGA zaimplementowaną w nowoczesnym, 8-bitowym mikrokontrolerze. Na przechowywanie ustawień przewidziano 102 bajty pamięci wewnętrznej.

Konfiguracja i programowanie

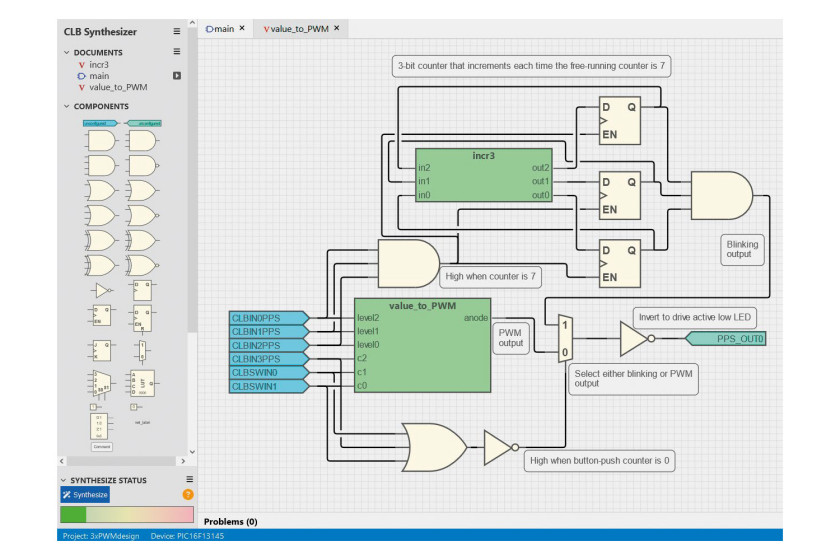

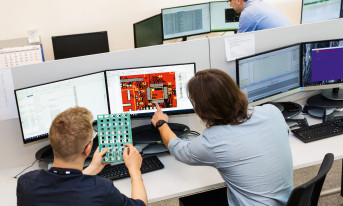

Proces konfigurowania CLB przeprowadza się z użyciem oprogramowania CLB Synthetizer, który jest oparty na graficznym interfejsie. Jego używanie jest jednoznaczne z przygotowaniem schematu blokowego, dzięki czemu program pozostaje czytelny nawet dla osób niezaznajomionych z pełną funkcjonalnością środowiska.

Program udostępniono w formie wtyczki (pluginu) do IDE MPLAB X. Z narzędzia można też skorzystać w zwykłej przeglądarce, gdyż jest dostępne jako aplikacja sieciowa. Efektem pracy w CLB Synthetizer jest plik konfiguracyjny, który następnie należy zaimportować do projektu, lub plik źródłowy w języku Verilog (rozszerzenie clb).

Budowa schematu odbywa się metodą przeciągania symbolicznych bloków oraz łączenia ich między sobą i z predefiniowanymi liniami wejścia/wyjścia. Praca w MPLAB daje się opisać w siedmiu krokach:

- Ustawienie sygnałów taktujących (zegarowych),

- Ustawienie bloków cyfrowych, takich jak UART, I2C, TMR i innych,

- Dodanie peryferiów analogowych, takich jak ADCC, DAC,

- Dodanie do projektu CLB poprzez utworzenie schematu blokowego z komponentami wchodzącymi w skład komórek BLE oraz zdefiniowanie połączeń pomiędzy nimi i sygnałami wejściowymi,

- Wykonanie syntezy (utworzenie pliku konfiguracyjnego),

- Na zakończenie należy zdefiniować i przypisać funkcjonalność używanym w projekcie wejściom/wyjściom mikrokontrolera.

- Finalnie dochodzi do wygenerowania kodu Melody.

Microchip przygotował szereg praktycznych przykładów zastosowania CLB do realizacji różnych zadań. Są to m.in. obsługa przesuwalnego rejestru programowalnych diod LED WS2812, sprzętowy debouncing przycisków, kodowanie/dekodowanie modulacji Manchester, multipleksowanie wartości 4-bitowej na sygnały sterujące wyświetlaczem 7-segmentowym.

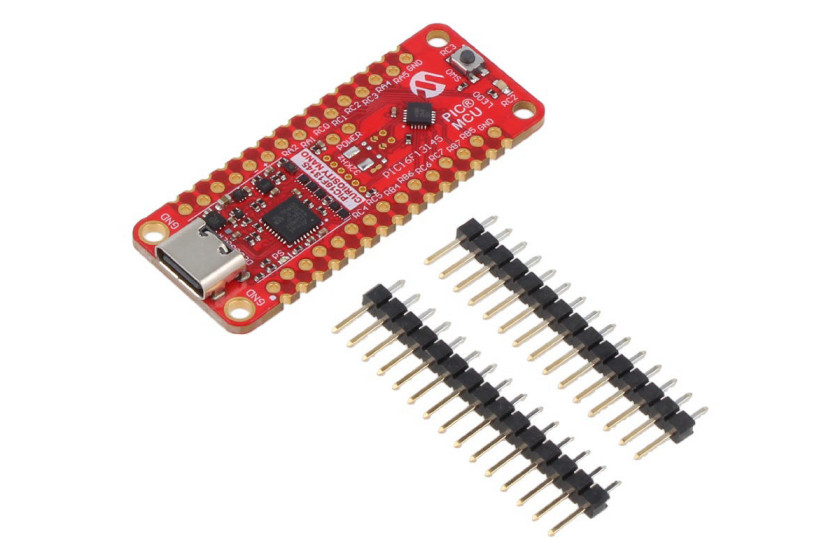

Zestaw uruchomieniowy Curiosity Nano

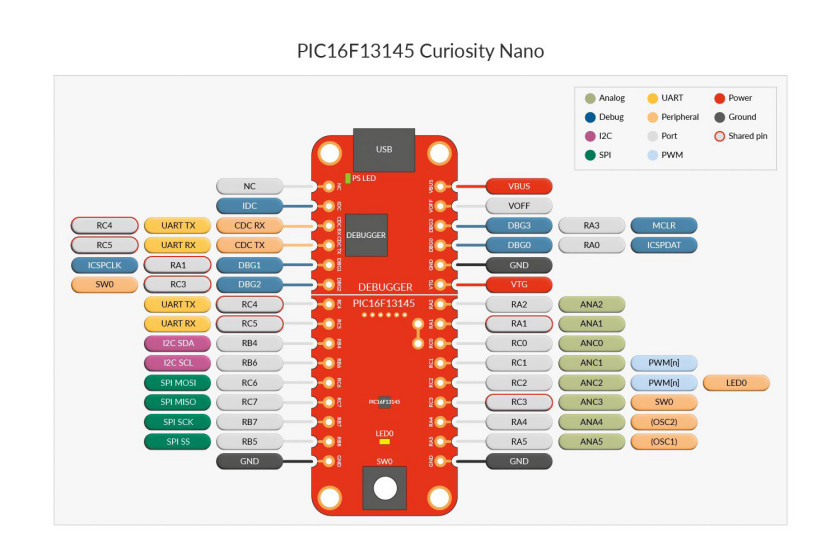

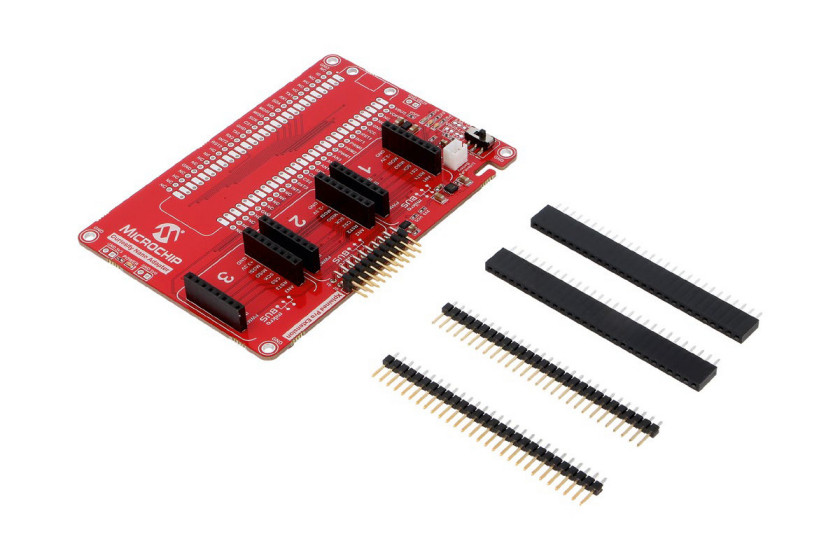

Platforma Curiosity Nano to zestawy ewaluacyjne ze zintegrowanym debuggerem, programatorem i dostępem do pinów mikrokontrolera. Dzięki temu stanowią znakomite narzędzie szkoleniowe i edukacyjne. Oczywiście, również dla rodziny PIC16F131xx opracowano specjalną płytkę Curiosity Nano EV06M52A z PIC16F13145. Funkcjonalność zestawu uruchomieniowego można poszerzyć przez wykorzystanie adapterów dedykowanych płytkom Curiosity Nano.

Zestawy te mają uniwersalne złącze kołkowe (żeńskie) służące osadzeniu płytki Curiosity Nano. W przypadku AC164162 obwód wyposażono w kilka interesujących elementów, jak 3 złącza zgodne ze standardem mikroBUS stosowanym w modułach Click producenta Mikroe. Warto w tym miejscu zaznaczyć, że z katalogu TME jest dostępnych ponad tysiąc różnych modeli takich płytek. Na PCB znalazło się też złącze rozszerzeń Xplained Pro. Ponadto całość może być zasilana z użyciem akumulatorów, gdyż adapter ma zintegrowany układ ładowania oraz zarządzania mocą kompatybilny z ogniwami litowo-jonowymi i litowo-polimerowymi.

TME

tel. 42 645 55 55

www.tme.eu