Wielowyjściowe układy zegarowe ispClock5400D

Wielowyjściowe układy zegarowe 50-400 MHz o błędzie jitteru 6ps rms

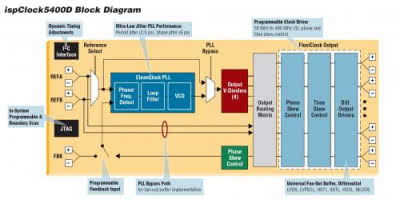

Firma Lattice Semiconductor wprowadza do oferty dwa nowe układy zegarowe rodziny ispClock5400D przeznaczone do generacji różnicowych sygnałów taktujących o bardzo małym błędzie jitteru w systemach komunikacyjnych i komputerowych (PCI Express, ATCA, MicroTCA, AMC). ispClock5406D i ispClock5410D zawierają odpowiednio 4 i 10 wyjść. Obsługują szereg standardów logicznych.

Mogą pracować w trybie rozpraszania widma (spread spectrum). Bieżąca konfiguracja jest przechowywana w wewnętrznej pamięci nieulotnej i może być zmieniana za pośrednictwem portu JTAG. Niektóre parametry mogą być ponadto regulowane w trakcie pracy układu za pośrednictwem interfejsu I²C.

Różnice faz pomiędzy sygnałami wyjściowymi mogą być indywidualnie i precyzyjnie kompensowane w celu uniknięcia błędów czasowych spowodowanych np. różnymi długościami ścieżek na płytce drukowanej. Do konfiguracji układów zegarowych ispClock5400D można wykorzystać np. oferowane przez Lattice narzędzie PAC-Designer (www.latticesemi.com/pac-designer).

Charakterystyka serii ispClock5400D:

- zakres częstotliwości sygnałów wyjściowych: 50-400 MHz,

- maksymalny jitter w okresie: 2,5ps,

- maksymalny jitter cykl-cykl: 29ps,

- typowy jitter fazy (RMS): 6ps,

- regulacja wyjściowych różnic fazowych: zakres ±12ns, krok 156ps,

- regulacja wyjściowych różnic czasowych: 16 ustawień, krok 18ps,

- maksymalny statyczny offset fazy: 100ps,

- formaty sygnałów wyjściowych: LVDS, LVPECL, HSTL, SSTL, HCSL, MLVDS,

- dostępne napięcia VCCO dla poszczególnych wyjść: 1,5V, 1,8V, 2,5V, 3,3V.

ispClock5406D i ispClock5410D są produkowane w obudowach QFN-48 i QFN-64 w wersji na komercyjny i przemysłowy zakres temperatur. Ceny hurtowe wynoszą odpowiednio 3,95 i 5,50 USD przy zamówieniach 1000 sztuk.

|

Więcej na www.latticesemi.com |