Efekt tych działań jest taki, że złożone systemy zasilające dostarczające wielu napięć wyjściowych dla poszczególnych bloków systemu coraz rzadziej buduje się z wykorzystaniem wielu konwerterów typu POL, połączonych w łańcuch i zasilanych z pośredniej magistrali. Raczej przetwarza się wysokie napięcie zasilające bezpośrednio do wartości docelowej, bo to pozwala na budowę zasilacza z mniejszej liczby komponentów.

Dla dostawców bloków zasilających trend ten jest wielkim wyzwaniem technicznym, gdyż na rynku pojawia się zapotrzebowanie na modułowe konwertery nieizolowane typu POL (niPOL) o dużej sprawności, małych wymiarach i akceptujące napięcia wejściowe zmieniające się w bardzo szerokim zakresie od 10:1 przez 12:1 aż po nawet 36:1.

Opracowanie wydajnych konwerterów o takiej funkcjonalności nie jest możliwe w ramach nieustannej powolnej ewolucji, która od zawsze towarzyszy rozwojowi systemów zasilających. Usprawnienia w zakresie sterowania, materiałów magnetycznych, lepszych elementów przełączających, technik pracy synchronicznej, wydajnych driverów, wyższych częstotliwości pracy dają zbyt mało efektów, aby zapewnić oczekiwane przez rynek parametry i zmiany, które można nazwać przełomowymi.

Aby zwiększać jednocześnie sprawność konwersji i zmniejszać wymiary komponentów, trzeba zwiększać częstotliwość pracy zasilaczy. Proces ten jest jednak mocno ograniczony przez trzy ważne zjawiska:

Pierwsze to tzw. twarde przełączanie, bo aby obniżyć straty, dąży się do tego, aby proces przełączenia klucza w zasilaczu trwał jak najkrócej. Producenci MOSFET-ów czynią wiele wysiłku, aby elementy te były zdolne do natychmiastowego odcinania prądu przy wysokim napięciu i stale poprawiają parametr FOM (Figure of Merit), ale pomijając parametry tranzystorów, szybkie przełączanie powoduje oscylacje, przepięcia, tym bardziej uciążliwe, im wyższa jest częstotliwość tego procesu. Drugim problemem jest obecność diody równoległej w tranzystorze MOSFET. Przy dużych częstotliwościach przełączania jej charakterystyka w kierunku i zaporowym rozmija się w czasie z pracą tranzystora i staje się powodem strat mocy. Trzeci problem to straty wynikające ze sterowania. Im szybciej chce się sterować MOSFET-em, tym wymagana jest większa moc zasilania dla drivera.

Ile w praktyce jest tych strat?

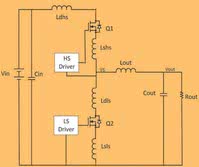

Na rysunku 1 pokazano schemat stopnia mocy typowego konwertera obniżającego napięcie (buck) z zaznaczonymi indukcyjnościami pasożytniczymi. Założono, że będzie on zasilany z napięcia 36 V i na wyjściu da 12 V/8 A, pracując z częstotliwością 650 kHz z dławikiem 2 μH lub 1,3 MHz i dławikiem 1 μH. Przy rezystancji RDS(ON)=10 mΩ, indukcyjnościach pasożytniczych na poziomie 300 pH, przeprowadzono symulację działania.

Wyniki pokazano na rysunku 2, gdzie zilustrowano moc traconą w "górnym" tranzystorze w zależności od napięcia Vs, prądów przewodzenia obu tranzystorów i prądu wyjściowego. Wskazują one, że duże straty mocy pojawiają się przy włączaniu tranzystorów, przy wyłączaniu są mniejsze. Dodatkowo obszar, gdzie źródłem strat jest RDS(ON), jest niewielki, co wynika z pewnością z ogromnego postępu, jakiego dokonali producenci tranzystorów w ostatniej dekadzie w zakresie strat przewodzenia. Średnie straty wyniosły 1,5 W przy 650 kHz, z czego na przewodzenie 0,24 W, przy załączaniu 1,047 W, a wyłączaniu 0,213 W. Innymi słowy, największe straty powoduje załączanie Q1.

Na rysunku 3 pokazano w powiększeniu proces załączania, z widocznym 30-nanosekundowym czasem martwym pomiędzy przewodzeniem Q1 i Q2 a działaniem w tym czasie diody równoległej tranzystora, która jest spolaryzowana w kierunku przewodzenia. Ładunek, który gromadzi się w złączu w czasie tego przewodzenia, musi być potem usunięty (tzw. reverse recovery).

W czasie przewodzenia diody zawartej w Q1 napięcie na Q1 jest wysokie, bliskie napięciu zasilania, stąd w drugiej części cyklu rozpoczynający przewodzenie Q1 musi usunąć ładunek z diody przy dużym napięciu, co jest źródłem wspomnianych strat mocy przy załączaniu Q1. Dopóki ładunek ze złącza diody zintegrowanej z Q1 nie zostanie usunięty, Q1 nie może wejść w rejon pracy z niską rezystancją RDS(ON). Stan taki trwa do momentu, aż cały ładunek zostanie usunięty z obszaru złącza.

Straty mocy mogą być nieco ograniczone poprzez przyspieszenie działania Q1 (większą wydajnością drivera), co powoduje skrócenie czasu rekombinacji nośników w diodzie tranzystora Q2 i szybszy wzrost napięcia w punkcie Vs. Ale zysk ten na skutek obecności indukcyjności pasożytniczych nie ma większego znaczenia praktycznego, bo szybkie zmiany sygnału skutkują większymi oscylacjami, które na skutek obecności pojemności Millera mogą się przenosić na bramkę MOSFET-a i zaburzać jego przewodzenie, zwłaszcza gdy tranzystory mają niskie napięcie UGS(TH). Innymi słowy zmiana ta wymaga dołożenia obwodów gaszących, w których powstają straty mocy niwelujące ewentualne zyski.

Praca z dużą częstotliwością przełączania

Ten sam układ (co pokazano na rys. 1) przesymulowano w kolejnym kroku w warunkach pracy z wyższą częstotliwością przełączania i mniejszą wartością indukcyjności, tak dobraną, aby wartości płynących prądów pozostały takie same. Przy 1,3 MHz straty mocy w górnym mosfecie wzrosły do 2,73 W, przy czym wzrost dotyczy strat związanych z załączaniem i wyłączaniem tranzystorów, bo straty na przewodzeniu, z uwagi na taką samą wartość prądu przewodzenia, nie zmieniły się. Dla całego konwertera wzrost strat w tranzystorze Q1 da się przeliczyć na 1,2% spadek sprawności, wywołany wyższą częstotliwością przełączania. Oczywiście do tego dochodzą inne straty, np. w materiałach magnetycznych. Oznacza to, że aby zapewnić wyższą sprawność konwertera, trzeba wyeliminować straty związane z załączaniem tranzystorów kluczujących.

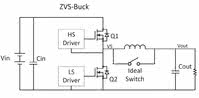

Topologia ZVS

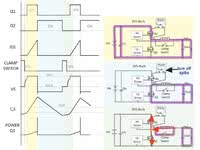

W konwerterze w topologii ZVS (Zero Voltage Switching) tranzystor Q1 jest załączany, gdy napięcie na nim jest bliskie zera, co uzyskuje się na skutek zjawiska rezonansu (rys. 4). Prąd płynący przez Q1 jest także wówczas bliski zera. Maksymalny prąd płynący przez tranzystor oraz dławik zasilacza jest określany przez czas załączenia tranzystora Q1, napięcie na tej indukcyjności i jej wartość. W czasie załączenia Q1 energia jest gromadzona w dławiku i dostarczana do kondensatora wyjściowego. Prąd płynie w obwodach zaznaczonych na rysunku 5, a straty mocy w konwerterze są największe w rezystancji RDS(ON) przewodzącego tranzystora, straty przełączania są pomijalne.

W kolejnym kroku Q1 jest wyłączany, potem przez krótką chwilę rzędu 10 ns przewodzi jego dioda równoległa. Na tyle krótko, że nie ma to przełożenia negatywnego na straty mocy. Warto zauważyć, że nie ma w tym momencie strat związanych z wyłączaniem Q1.

Dalej załączany jest tranzystor Q2 i energia zgromadzona w indukcyjności jest przekazywana do obciążenia. W momencie, gdy prąd w indukcyjności osiągnie zero, Q2 dalej przewodzi, pozwalając, aby trochę energii z kondensatora wyjściowego "przelało się" do dławika. Efekt ten widać po tym, że kierunek prądu w dławiku delikatnie zmienia się na przeciwny (obszar w kolorze niebieskim na rys. 5).

Gdy kontroler zasilacza uzna, że energii w indukcyjności jest już dość, Q2 jest wyłączany i zamykany jest przełącznik łączący punkt Vs z wyjściem VOUT. Przełącznik izoluje prąd płynący przez dławik od wyjściowego, a zasilanie dla wyjścia jest pobierane z pojemności wyjściowej.

Gdy faza ta zakończy się, przełącznik jest rozwierany, a energia zgromadzona w dławiku rezonuje z połączeniem równoległym pojemności wyjściowych tranzystorów Q1 i Q2, co powoduje, że napięcie w węźle Vs podnosi się do VIN. Oscylacje rozładowują pojemność wyjściową Q1, ładują pojemność Q2 i pozwalają załączyć Q1 w chwili, gdy napięcie Vs jest zbliżone do VIN, czyli bezstratnie (sekcja zielona na rysunku). Ważna uwaga jest taka, że gdy przełącznik jest zamknięty, prąd krąży w zaznaczonej na różowo pętli, a gdy jest wyłączony, tak jak pokazuje czerwona strzałka.

Dzięki temu, że tranzystory przełączają przy napięciu bliskim zera, straty mocy związane z załączaniem i wyłączaniem są wyeliminowane. Dzięki przełącznikowi zamykającemu prąd w dławiki zlikwidowano straty w diodzie równoległej MOSFET-a.

Dzięki przełączaniu przy zerowym napięciu wpływ efektu Millera jest znacznie mniejszy, przez co driver sterujący może mieć mniejszą wydajność prądową i tym samym mniejsze straty.

Porównanie obu rozwiązań

Aby ocenić zysk energetyczny wynikający z nowej technologii, poddano symulacji układ konwertera ZVS o takich samych parametrach jak poprzedni, dla częstotliwości 1,3 MHz. Średnie straty mocy w Q1 wyniosły 1,33 W, a więc mniej niż dla tradycyjnej topologii pracującej z dwukrotnie mniejszą częstotliwością. Różnica w stratach dla tej samej częstotliwości była jeszcze większa - 1,37 W.

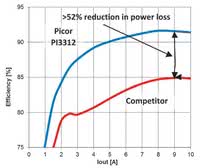

Na rysunku 6 pokazane zostały krzywe sprawności energetycznej pomiędzy dwoma podobnymi rozwiązaniami bazującymi na tradycyjnej topologii i ZVS. W obu przypadkach użyte zostały gotowe konwertery obniżające napięcie z 24 do 2,5 V (9,6:1) przy prądzie 10 A. Jak widać, przy pełnym obciążeniu różnica w sprawności 6,5% jest większa dla rozwiązania ZVS, co przekłada się na 52% mniejsze straty mocy.

Przykład konwertera ZVS dostępnego w handlu

Rys. 6. Porównanie sprawności konwertera ZVS-Buck 9.6:1 step down 24 V - 2,5 V @ 10 A z rozwiązaniem pracującym bez przełączania ZVS

Jednym z doskonałych przykładów, jakie korzyści daje topologia ZVS, jest seria konwerterów Picor PI33xx (na zdjęciu). Są one umieszczone w małej obudowie SiP o rozmiarach 10×14 mm i wymagają dołączenia z zewnątrz jedynie dławika i kilku kondensatorów. Układy są zdolne do dostarczania mocy wyjściowej do 120 W, a ich maksymalna sprawność wynosi 98%. Konwertery mogą być zasilane napięciem do 36 V i generują napięcie wyjściowe 1-15 V (10 A) przy sprawności lepszej od 86%. Szerokie pasmo pętli sprzężenia zwrotnego 100 kHz z marginesem fazy 55° zapewnia dobrą odpowiedź impulsową i stabilność. Szybkość reakcji na zmianę obciążenia jest krótsza niż 20-30 μs.

Konwertery PI33xx mogą być łączone równolegle i pracować synchronicznie. przy niskich obciążeniach realizują pracę w trybie oszczędnościowym z gubieniem impulsów sterujących, co zapewnia wysoką sprawność bez obciążenia.

C. R. Swartz

SE Spezial Electronic Sp. z o.o.

spezial.pl