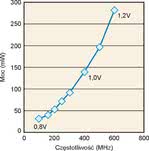

Ponieważ pobór mocy przez układy logiczne CMOS w stanie spoczynku jest bardzo mały, wiele z metod bazuje na wyłączaniu chwilowo nieużywanych bloków funkcjonalnych. Moc pobierana jest ponadto proporcjonalna do częstotliwości sygnału zegarowego, dlatego kolejnym sposobem ograniczania zużycia energii jest sterowanie sygnałem zegarowym tak, aby miał on najniższą wartość zapewniającą w danej chwili dostateczną wydajność przetwarzania.

Rys. 1. Pobór mocy w procesorze sygnałowym wbudowanym w mikroprocesor Blackfin firmy Analog Device, w zależności od częstotliwości pracy i wymaganego napięcia zasilania

Widać więc, że zagadnienie zmniejszenia poboru mocy jest skomplikowane i musi uwzględniać związki między poszczególnymi parametrami. Mimo opisywanych wad takiej regulacji, dynamiczne przestrajanie parametrów wielu parametrów jest stosowane i będzie opisane w dalszej części artykułu.

Mniejszy - większy kłopot

W większości przypadków prąd pobierany przez układy CMOS w stanie statycznym pomija się. Postęp w miniaturyzacji powoduje jednak, że dla najnowszych technologii półprzewodnikowych prąd upływu jest dość duży nie może być już dłużej pomijany. W najnowszych technologiach 90nm lub 45nm związane z nim straty mocy mogą sięgać aż 50% rozpraszanej mocy.

Wzrost skali integracji oznacza też zwiększenie pojemności pasożytniczych pomiędzy poszczególnymi elementami na strukturze scalonej i wzrost dynamicznego poboru prądu.

Wpływ na to ma również ciągłe zwiększanie częstotliwości zegarowej, które jest praktykowane ze względu na rosnące potrzeby w zakresie szybkości przetwarzania sygnałów.

Złożenie się trzech opisanych wcześniej zjawisk, czyli większego prądu upływu, większej liczby tranzystorów w układzie, oraz większych częstotliwości zegara powoduje, że producenci oferują układy CMOS optymalizowane pod względem pracy z bardzo niskim napięciem (1V i mniej). Mniejsze napięcie zmniejsza pobór mocy dynamicznej, ale także korzystnie wpływa na zmniejszenie prądu upływu. Takie rozwiązanie ma jednak podstawową wadę, która sprawia, że układy przeznaczone do pracy z bardzo niskimi napięciami są jednocześnie przeznaczone do pracy z mniejszymi częstotliwościami.

Dwie techniki

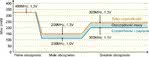

Rys. 2. Pobór mocy przez procesor Intel PXA 255 w zależności od zasilania i częstotliwości pracy. Odpowiednie dostosowanie ustawień parametrów procesora do jego obciążenia umożliwia oszczędność energii.

Decyzje podejmowane na etapie projektowania mają szczególny wpływ na sprawność projektowanego urządzenia i w znacznej mierze określają, czy uda się spełnić założenia w kwestii poboru mocy przez daną aplikację. Każde zaniedbanie na etapie projektu sprzyjające zwiększeniu poboru mocy wpływa niekorzystnie na wydajność całego systemu lub może go nawet całkiem zdestabilizować. Pomysły analizowane na tym etapie obejmują przede wszystkim wybór sprzętu i architektury oraz strategii projektowania.

Na pobór mocy urządzenia bezsprzecznie wpływa sprawność jego elementów składowych. Z tego powodu najważniejszą decyzją, od której należy rozpocząć projektowanie jest wybór korzystnych pod względem energetycznym podzespołów. Ponadto jedną z oczywistych metod wydaje się być po prostu odłączanie od zasilania nieaktywnych elementów układu. W wielu przypadkach tylko mały ułamek całego układu jest aktywny przez cały czas. W związku z tym znaczący spadek zużycia energii może zostać osiągnięty poprzez podzielenie układu na wiele obszarów i doprowadzaniu zasilania tylko do aktywnych części. Mimo, że pomysł z założenia wydaje się prosty w praktyce pociąga za sobą wiele problemów w procesie projektowania. Innym podobnym rozwiązaniem jest podział układu na tzw. wyspy napięciowe. Jest to technika polegająca na zasilaniu różnych części układu mniejszym napięciem, w zależności od wymagań nałożonych na częstotliwość pracy. Obie te metody są szeroko opisane w literaturze.

Wykorzystać możliwości układowe

Producenci układów scalonych wyposażają je zazwyczaj w różnorodne możliwości ograniczania poboru mocy, głównie dzięki wprowadzeniu trybów pracy. Jednym z najpowszechniejszych sposobów jest wykorzystanie trybu „sleep”, który mają praktycznie wszystkie układy cyfrowe. Coraz częściej dostępne bywają również tryby głębszego uśpienia, co oczywiście pozwala w jeszcze bardziej efektywny sposób zredukować pobieraną moc. Jest to jednak przeprowadzane kosztem większych opóźnień wymaganych do powrotu układu do pełnego stanu, w którym znajdował się układ przed wprowadzeniem w tryb oszczędzania. W takim przypadku moc pobierana jest jedynie w celu utrzymania zawartości pamięci.Do wnętrza układów wbudowuje się również funkcje wspierające dynamiczną zmianę napięcia oraz częstotliwości. Programowalne zegary pozwalające aplikacji na ograniczanie mocy dynamicznej proporcjonalne do zmniejszenia częstotliwości i przestrajalne źródła napięcia pozwalają na dynamicznej regulacji częstotliwości i napięcia zasilania z poziomu oprogramowania. Przykładem możliwości jakie daje taka regulacja może być procesor Intel PXA255, który pobiera moc 0,80mW/MHz jeżeli pracuje z częstotliwością 400MHz i napięciem 1,3V. Gdy częstotliwość pracy zostanie zmniejszona do 200MHz, a napięcie do 1V również pobierana moc jest mniejsza i wynosi 0,58mW/MHz.

Mniejszy pobór mocy zapewnia również inicjowanie systemu przy pozostawieniu niektórych podsystemów nie zasilonych do momentu, gdy stanie się to rzeczywiście niezbędne. Start systemu, w którym uaktywniane są od razu wszystkie jego składniki jest przyczyną znaczących strat mocy. System jest zazwyczaj inicjowany z maksymalną częstotliwością zegara. W tym czasie z pewnością zostaną włączone również takie podsystemy, które nie są aktualnie potrzebne lub w przypadku danej aplikacji mogą nawet nigdy nie być uruchomione.

W przypadku urządzeń przenośnych częstą sytuacją jest zmiana źródła zasilania z sieciowego na bateryjne, np. w laptopach. W tym przypadku system operacyjny rejestruje informację o zmianie trybu zasilania i wprowadza w życie ograniczenia polegające na przykład na zwolnieniu szybkości procesora, skróceniu czasu oczekiwania do momentu wyłączenia ekranu i dysku twardego, czy też zmniejszeniu jaskrawości ekranu. Zadaniem systemu operacyjnego jest osiągnięcie kompromisu pomiędzy wydajnością urządzenia, a staraniem o wydłużenie czasu pracy na zasilaniu bateryjnym. Podobna technika może być zastosowana w przypadku urządzeń zasilanych wyłącznie na baterie, w których w momencie, gdy zostaje wykryty niski poziom pozostałej energii zostają podjęte podobne kroki, ograniczające działanie niektórych funkcji.

Sztuka oszczędnego programowania

Rys. 4. Hipotetyczny nowoczesny procesor pracujący z niższą częstotliwością. Pomimo to, sumaryczny pobór mocy jest większy niż na rys. 3.

Istotne jest, aby oprogramowanie obsługujące dany system było zoptymalizowane pod kątem jego możliwości przetwarzania. Biorąc pod uwagę pobór mocy wydajniej napisane oprogramowanie oznacza zazwyczaj dłuższy czas, w którym system może pracować w trybie uśpienia, lub w którym szybkość przetwarzania danych przez procesor może być zmniejszona. Umiejętne wykorzystanie instrukcji może skutkować różnym zapotrzebowaniem energetycznym. Jest to przedmiotem analizy metod bazujących na wpływie zastosowania poszczególnych instrukcji na sprawność systemu.

Często dobrym rozwiązaniem ograniczającym zużycie energii jest oszczędność osiągnięta kosztem dokładności obliczeń, nie zawsze niezbędnej dla prawidłowości działania danej aplikacji. W przypadku niektórych zastosowań precyzyjny wynik nie ma aż tak dużego znaczenia. Akceptacja straty pewnej dokładności może tymczasem w znaczący sposób uprościć proces przetwarzania wyników, a przez to zmniejszyć również pobór mocy.

Monika Jaworowska