MAX10 - nowa generacja FPGA firmy Altera

| TechnikaUkłady MAX10 z oferty Altery to niebanalne połączenie bazującej na komórkach SRAM technologii FPGA i Flash, które zintegrowane w jednej obudowie tworzą niebanalną, rekonfigurowalną platformę sprzętową o dużych zasobach logicznych, bogatym wyposażeniu sprzętowym (wbudowane m.in. pętle PLL i 12-bitowe przetworniki ADC), dużej szybkości pracy i niewielkim poborze mocy.

Prefiks nazwy rodziny MAX10 może sugerować przynależność do rodziny układów CPLD - jak starsze układy MAX - ale to tylko zabieg marketingowy: MAX10 to pełnokrwiste FPGA, bazujące na architekturze użytej w rodzinie Cyclone IV, wyposażone we wbudowaną nieulotną pamięć konfiguracyjną Flash.

Jest to pierwsza - w ofercie Altery - rodzina układów programowalnych o dużych zasobach logicznych, która nie wymaga użycia zewnętrznego konfiguratora, który nie tylko ograniczał możliwości ochrony własności intelektualnej, ale zwiększał także koszt wykonania urządzenia i wydłużał czas startu od chwili włączenia zasilania.

Drugim zabiegiem marketingowym producenta jest nazwanie układów MAX10 mianem "Generation 10", co ma zapewne sugerować rewolucyjne zmiany użytej architektury, ale - jak już wspomniałem - bazuje ona na dobrze przetestowanej konstrukcji z Cyclone IV, która przez lata dowiodła swoich zalet.

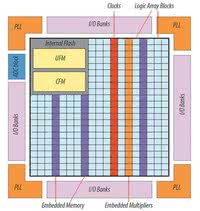

Schemat blokowy układów MAX10 pokazano na rysunku 1. Wbudowana w układ pamięć nieulotna Flash-NOR jest podzielona na dwa podstawowe obszary:

- pamięć konfigurującą CFM, w której jest przechowywany obraz konfiguracji FPGA. Większość dostępnych typów układów z serii MAX10 (poza układami o najmniejszych zasobach logicznych - tabela 1) wyposażono w dwa banki wewnętrznej pamięci konfiguracyjnej, dzięki czemu można dokonywać błyskawicznej "rekonfiguracji" sprzętu (przez podmianę aktywnego obszaru pamięci), bez konieczności zatrzymywania pracy całego systemu.

- pamięć Flash dla aplikacji użytkownika (UFM - User Flash Memory), dostępna w układzie za pośrednictwem magistrali Avalon Memory-Mapped, o maksymalnej pojemności dochodzącej do niemal 6 Mb. Pamięć ta może być używana jako równoległa z taktowaniem do 116 MHz i maksymalnej szerokości słowa 32 bity lub jako szeregowa, z maksymalną częstotliwością taktowania wynoszącą ok. 7,25 MHz.

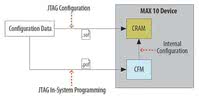

Rys. 2. Użytkownik ma w układzie MAX10 dostęp przez JTAG zarówno do wewnętrznej pamięci nieulotnej Flash jak i pamięci konfigurującej CRAM

Sposób działania wewnętrznych pamięci konfiguracyjnych oraz ich programowanie przedstawiono na schemacie blokowym na rysunku 2. Jak widać, użytkownik może bezpośrednio modyfikować pamięć konfiguracyjną CRAM (komórki SRAM) oraz niezależnie Flash, a także wymusić automatyczną konfigurację matrycy FPGA po włączeniu zasilania. Dzięki takiemu rozwiązaniu podczas prac projektowych układ można wielokrotnie konfigurować bez ryzyka naruszenia trwałości pamięci nieulotnej.

Obydwa obszary pamięci Flash są podzielone na sektory, które można programować niezależnie od siebie, co zwiększa trwałość pamięci nieulotnej, która i tak jest duża - producent deklaruje minimalną liczbę cykli kasowanie-zapis wynoszącą 10000 w pełnym zakresie temperatur oraz trwałość zapisanych danych nie krótszą niż 20 lat przy temperaturze otoczenia nie wyższej niż +85°C.

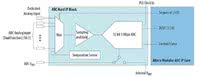

Drugą - rzadko spotykaną w układach PLD atrakcją - są wbudowane w układy MAX10 przetworniki ADC o rozdzielczości 12 bitów (rys. 3). W zależności od wersji układu i zastosowanej obudowy, są one wyposażone w jeden lub dwa przetworniki ADC (SAR), o łącznej liczbie kanałów wejściowych wynoszącej maksymalnie 18.

Układy są wyposażone w jedno lub dwa wejścia analogowe, pozostałe linie wejściowe mogą być wykorzystywane z puli uniwersalnych I/O. Maksymalna częstotliwość próbkowania sygnału analogowego przez ADC wynosi 1 MHz, sygnał taktujący jest generowany przez zdefiniowane przez producenta generatory PLL.

Interesującym zabiegiem producenta, praktycznie niespotykanym w rozwiązaniach konkurencyjnych, jest wyposażenie kanałów wejściowych w programowany dzielnik napięcia, który umożliwia pomiar napięć o wartości dwukrotnie większej niż napięcie zasilania ADC. Przetwornik wyposażono ponadto w półprzewodnikowy (diodowy) czujnik temperatury, który jest dołączony do jednego z wejść przetwornika ADC. Podczas pomiaru temperatury przetwornik domyślnie jest taktowany sygnałem zegarowym o częstotliwości 50 kHz.

Nieco mniej spektakularnym elementem wyposażenia układów MAX10 są konfigurowalne porty GPIO przystosowane do implementacji sprzętowego interfejsu zewnętrznej pamięci EMIF (rys. 4), który w trzech najmniejszych układach z rodziny obsługuje pamięci SRAM, w pozostałych także pamięci SDRAM: DDR3, DDR2 i LPDDR2.

Ze względu na dużą częstotliwość taktowania interfejsu pamięci zewnętrznej (do 303 MHz w przypadku pamięci DDR3/DDR3L) producent przewidział możliwość dynamicznej modyfikacji fazy sygnału taktującego, która jest realizowana w zależności od napięcia zasilającego i temperatury w taki sposób, aby zminimalizować straty czasu podczas cykli zapisu/odczytu danych.

Prezentowane układy są wyposażone także w sprzętowe multiplikatory 9×9 lub 18×18 bitów, które można wykorzystać do implementacji sprzętowych bloków obliczeniowych dla aplikacji DSP - na przykład często stosowanych bloków MAC (Multiply-ACcumulate). Ich maksymalna liczba (w zależności od typu układu) wynosi 144, analogicznie do pozostałych elementów architektury, także multiplikatory są bardzo elastyczne, można je konfigurować, dobierając sposób pracy i interfejs komunikacyjny do wymogów aplikacji.

Ostatnim elementem wyposażenia układów MAX10, na który warto zwrócić szczególną uwagę, są wbudowane generatory sygnałów zegarowych bazujące na syntezerach PLL, których może być w układzie 2 lub 4 (w zależności od typu). Umożliwiają one generowanie precyzyjnych sygnałów taktujących, dystrybuowanych wewnątrz układu za pomocą odpowiednich linii zegarowych.

Wymienione elementy wyposażenia układów MAX10 upraszczają implementację IP core’ów kompletnych rdzeni mikrokontrolerowych lub mikroprocesorowych, w tym dystrybuowanego przez Alterę NIOS II w wersji "e", który w najprostszym przypadku może korzystać z wewnętrznych zasobów pamięci Flash i SRAM użytkownika (ulokowanej w blokach M9K), bez konieczności używania jakichkolwiek pamięci zewnętrznych.

Producent wraz z wprowadzeniem na rynek nowych układów udostępnił nową wersję środowiska Quartus II (od 15.0 w górę) z bibliotekami umożliwiającymi syntezę projektów na układy MAX10, dostępne są także tanie zestawy startowe z tymi układami. Jednym z najpopularniejszych jest Altera MAX 10 Evaluation Kit (fotografia 5).

Zastosowano w nim układ w obudowie LQFP144 (10M08SAE144-C8GES) w dość skromnym otoczeniu, co jest częściowo rekompensowane przez złącze zgodne z Arduino Rev. 3, dzięki któremu do współpracy z układem MAX10 można użyć dowolnych ekspanderów (shieldów) Arduino, przy czym muszą być one przystosowane do zasilania napięciem 3,3 V.

Nowa platforma sprzętowa Altery to poważny ukłon w stronę użytkowników, których dotychczasowe architektury systemów bazujących na FPGA zniechęcały stopniem skompilowania i ceną. Możliwość łatwego zintegrowania w FPGA kompletnego mikroprocesora o budowie "na życzenie" oraz zestawu własnych bloków peryferyjnych są sporą zachętą do korzystania z układów MAX10 dla konstruktorów, którym zależy na zoptymalizowaniu projektu pod kątem wydajności obliczeniowej, poboru mocy, nakładu pracy i ceny kompletnego rozwiązania.

Piotr Zbysiński