Stosowane dotychczas komórki 1-bitowe mogą przyjmować dwa stany: zero lub jeden. Mają one zostać zastąpione w przyszłości komórkami 4-bitowymi zdolnymi przechowywać szesnaście różnych stanów.

Technologie zapisu wielobitowego MirrorBit i MirrorBit Quad

W technologii MirrorBit, w przypadku której podwojenie gęstości upakowania informacji osiągnięto dzięki zastosowaniu dwóch osobnych bitów do przechowywania informacji umieszczonych po przeciwnej stronie komórki pamięci (rys. 1). Każdy z bitów pracuje w sposób binarny i może być bezpośrednio odczytywany przez kontroler pamięci. Odczyt lub programowanie komórek zlokalizowanych po jednej ze stron komórki odbywa się w sposób niezależny od danych zgromadzonych po drugiej stronie.

Tymczasem firma Spansion zaprezentowała układy wykonane w procesie 90nm, w których wykorzystano technologię MirrorBit Quad bazującą na opracowanych przez Saifun Semiconductors – pamięciach NROM. Następna generacja pamięci Spansion, opartych o proces 65nm i technikę MirrorBit Quad pojawi się na rynku w drugiej połowie 2008 roku. Warto zauważyć, że od 4-bitowej komórki wymagane będzie zapamiętanie szesnastu różnych stanów, np. w postaci jednego z szesnastu dopuszczalnych poziomów napięcia.

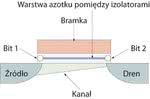

NROMKomórka pamięci NROM zawiera warstwę azotku otoczoną dwoma warstwami tlenku krzemu będącego izolatorem. Warstwa azotku pełni rolę pułapki, w której przechowywane są elektrony. Składają się na nią dwa oddzielne regiony, zlokalizowane na końcach komórki, w których przechowywane są dwa niezależne bity. Każdy region może być zaprogramowany lub skasowany poprzez uwięzienie lub usunięcie ładunku w warstwie azotku. Umożliwia to przechowywanie informacji bez konieczności rozwiązywania złożonych problemów towarzyszących technologiom operującym kilkoma poziomami napięć wewnątrz pojedynczej komórki. Zbędne staje się rozpoznawanie jednego z kilku stanów napięć na rzecz binarnej reprezentacji danych (rys.). Każdy region wewnątrz komórki pamięci NROM może być programowany lub kasowany niezależnie od pozostałych. Programowanie odbywa się na zasadzie podania napięcia, które spowoduje, że ujemnie naładowane elektrony zostaną uwięzione w warstwie azotku w pobliżu końca jednej z komórek. Skasowanie zawartości komórki polega na podaniu napięcia, pod wpływem którego dodatnie ładunki zostaną wprowadzone do warstwy azotku, usuwając ujemny ładunku wewnątrz komórki zgromadzony na etapie programowania. Pamięć NROM może być programowana i kasowana szybciej niż ma to miejsce w tradycyjnej technologii bazującej na tranzystorach z pływającą bramką, gdyż do zaprogramowania komórki potrzeba znacznie mniejszego ładunku. Czas ten jest dodatkowo skracany ze względu na specyficzną budowę komórek pamięci NROM. |

Pływająca bramka MLC

Technologia MLC wykorzystuje do przechowywania informacji pływającą bramkę tranzystora, w której umieszczana jest określona liczba elektronów. Programowanie komórki pamięci polega na kontrolowanym umieszczaniu w rejonie kanału tranzystora określonego ładunku, którego wartość musi być większa od bariery potencjału na złączu Si-SiO2. Jest to warunek niezbędny do uwięzienia wewnątrz pływającej bramki ładunku. Standardowe pamięci wymagały nieco mniej niż 5000 elektronów do przechowania bitu 1 lub ponad 30000 elektronów dla bitu 0. Podczas odczytu pojedynczej komórki o obecności lub nieobecności ładunku świadczy zachowanie tranzystora będącego, odpowiednio, w stanie przewodzenia bądź odcięcia.

Możliwość precyzyjnego kontrolowania liczby elektronów umieszczanych wewnątrz bramki tranzystora jest kluczem do budowy pamięci z komórkami wielobitowymi. Otrzymuje się w ten sposób analogowe urządzenie, w którym można rozróżnić więcej niż dwa stany. Pamięć taka przechowuje już nie bity, a określoną liczbę elektronów. Możliwość umieszczania ładunków tak, aby ich liczba zawierała się w jednym z czterech, odgórnie określonych przedziałów, pozwala przechowywać cztery bity. Każdy z tych czterech stanów ma przypisaną odpowiednią kombinację zer i jedynek. Histogram z rys. 3. przedstawia rozrzut między programowaną liczbą elektronów (połowa jednego z czterech przedziałów) oraz rzeczywistą liczą elektronów umieszczonych wewnątrz bramki. Warte zauważenia jest, że osiągnięto precyzję na poziomie 0,3V tj. około 3000 elektronów.

Zwiększanie pojemności bitowej pojedynczej komórki wymaga precyzyjnego kontrolowania ładunku wewnątrz bramki tranzystora, znaczących innowacji w używanej technologii oraz rozległego zrozumienia i scharakteryzowania zachowania komórek pamięci, procesów ich wytwarzania oraz testowania. Dużym wyzwaniem dla producentów półprzewodników jest wytwarzanie pamięci w technologii MLC z komórkami przechowującymi 2 bity. Sytuacja ulegnie pogorszeniu w przyszłości, gdyż wprowadzenie komórek 4-bitowych podniesie poziom skomplikowania układów sterujących oraz technologii produkcji takich pamięci.

Różnica napięć pomiędzy sąsiednimi poziomami logicznymi w komórce pamięci MLC wynosi 1,5V. Staje się ona jeszcze mniejsza w układach przechowujących 4 bity w jednej komórce - wynosi ona typowo 0,2V stanowiąc tym samym jedynie 13% napięcia dzielącego sąsiednie poziomy logiczne w układach MLC. Prowadzi to do nieuchronnego zwiększenia liczby błędów podczas odczytu układów z komórkami 4-bitowymi. Niezbędna staje się implementacja kodów ECC (Error-Correcting Code), które pozwolą na eliminację przekłamań podczas odczytu. Dalsze zwiększanie stopnia skomplikowania procesu produkcji pociągnie za sobą konieczność wydłużenia kodów ECC. Przykładowo w procesie 70nm stosowanym przy produkcji pamięci MLC wykorzystano kod 4-bitowy, ale jego rozmiar może ulec wydłużeniu do 8 lub 15 bitów, gdy pamięci będą produkowane w procesie 50nm. Jeszcze lepsze zabezpieczenia będą niezbędne, gdy pojedyncza komórka będzie miała przechowywać 4 bity. Toshiba produkując pamięci w procesie 70nm, w których komórki mają organizację 4-bitową, musi brać pod uwagę zwiększone wymagania co do długości kodu ECC. Stosuje się w nim dodatkowe strony pamięci zabezpieczające poprawność pracy. Wzrost zajmowanej w ten sposób powierzchni krzemu wynosi około 15% w porównaniu do komórek 2-bitowych w technologii MLC.

Działania firm

Pomimo wzrostu złożoności procesu produkcji, stosowanie komórek 4-bitowych pozwala zmniejszyć rozmiar struktury półprzewodnikowej. Przykładem mogą być pamięci ORNAND produkowane przez firmę Spansion w dwóch różnych technologiach: MirrorBit oraz MirrorBit Quad. Umieszczenie 4 bitów prowadzi do ograniczenia wielkości struktury półprzewodnikowej o 42%, przy zachowaniu tego samego procesu technologicznego.

Cechą charakterystyczną komórek 4-bitowych jest wzrost liczby impulsów wymaganych do odczytu i zapisu danych w pamięci. Prowadzi to do konieczności znacznego zwiększenia częstotliwości sygnałów taktujących i tym samym zaburzeń EMI. Wpływają one na pracę tranzystorów z pływającą bramką, które stanowią podstawowy element tych pamięci. Algorytm wykorzystywany do odczytu i zapisu danych musi uwzględniać istnienie EMI, aby zapobiec utracie integralność sygnałów i pogorszeniu jakość pracy pamięci.

Zapis i odczyt komórek pamięci operujących na 16 poziomach napięcia musi być połączony z bieżącą kontrolą i wyliczaniem kodów korekcyjnych ECC. Obniża to, niestety, znacznie wydajność pracującego układu. Wykonane w tym kierunku eksperymenty wykazały, że wydajność takich pamięci jest zbliżona do pamięci NOR Flash - zapis odbywa się z prędkością 0,62MB/s. Jest to wynik niespełniający wymagań stawianych przez współczesne standardy i konieczne staje się zwiększenie szybkości zapisu. Jednym ze sposobów jest przygotowanie specjalistycznego kontrolera współpracującego z pamięcią. Musi on zagwarantować możliwie największą wydajność osiąganą w końcowym produkcie. Oznacza to, że np. aparat fotograficzny powinien zapisywać zdjęcia na karcie pamięci możliwie szybko. Podobnie wygląda sytuacja z zapisem muzyki w popularnych odtwarzaczach MP3. Przy zapisie z szybkością na poziomie 0,62MB/s zapełnienie karty pamięci o pojemności 2GB zajmie 55 minut.

W kierunku 4 bitów

Firma Toshiba mocno zaangażowała się w rozwój nowej technologii. Rozpoczęła m.in. tworzenie nowego typu pamięci opartego 4-bitowe. Ponadto w planach rozwoju pojawiła się technologia 3-bitowych komórek pamięci i została uwzględniona jako rozwiązanie tymczasowe.

Jednym z czynników zapewniających ciągły rozwój pamięci jest nieustanne doskonalenie procesu litografii przez producentów półprzewodników, którzy m.in. zmniejszają wymiar charakterystyczny w stosowanym procesie technologicznym. Umożliwia to zwiększanie pojemności pamięci przy zachowaniu stałych wymiarów krzemowego podłoża. Proces ten nie może być jednak doskonalony w nieskończoność i potrzebne są nowe metody pozwalające systematycznie zwiększać gęstość upakowania danych. Jedną z takich metod jest właśnie zwiększanie pojemności bitowej pojedynczej komórki.

Pamięci oparte o 3-bitowe oraz 4-bitowe komórki powinny pojawić się na rynku pomiędzy rokiem 2009 a 2011. Producenci zapowiadają także badania nad pamięciami trójwymiarowymi, które mają bazować na kilku warstwach półprzewodnika ułożonych na jednym podłożu. Ma to doprowadzić do zwiększenia pojemności pojedynczego układu scalonego.

Podsumowanie

W przeciągu najbliższych dwóch lub trzech lat na rynku pamięci NAND Flash powinny pojawić się szybsze i bardziej niezawodne układy wykorzystujące komórki wielobitowe. Zapis i odczyt ośmiu lub szesnastu stanów napięć, jakimi będzie operować nieustannie zmniejszana komórka, będzie stanowić coraz większe wyzwanie dla producentów. Będzie wymagać zaawansowanych projektów oraz opracowywania algorytmów pracy i zabezpieczenia kodami ECC. Niezbędna do osiągnięcia tego celu będzie bardzo ścisła współpraca producentów półprzewodników i projektantów kontrolerów. Znaczącą rolę na przestrzeni najbliższych kilku lat odegrają technologie przygotowane do obsługi pamięci 4-bitowych oparte o dedykowane kontrolery scalone oraz specjalistyczne algorytmy programowe. Wysoko zoptymalizowany i niezawodny algorytm zapisu i odczytu pamięci będzie jednym z najważniejszych czynników decydujących o sukcesie 3-bitowy i 4-bitowych pamięci na rynku.

|

Tabele |

Jakub Borzdyński