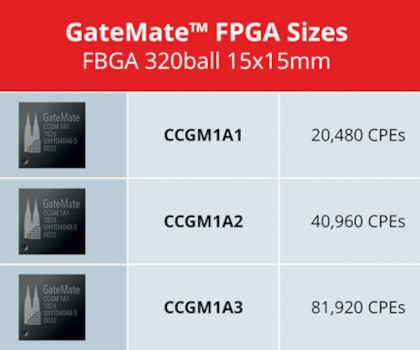

Układy GateMate powstały w odpowiedzi na potrzeby rynku w zakresie rozwiązań zapewniających jednocześnie duże zasoby logiczne z małym poborem mocy, co zwykle stanowi poważny problem w układach FPGA opartych na SRAM. Dodatkowo udało się wyprodukować chipy w małych obudowach i w korzystnej cenie. Produkcja odbywa się w GF Factory 1 w Dreźnie w oparciu o energooszczędną technologię 28SLP. Minimalizuje to ryzyko ograniczeń handlowych, ceł i zakłóceń w łańcuchach dostaw. Pierwszym układem z rodziny jest A1, który jest już dostępny w ilościach produkcyjnych, kolejny A2 będzie dostępny jako próbki w drugim kwartale 2023 roku.

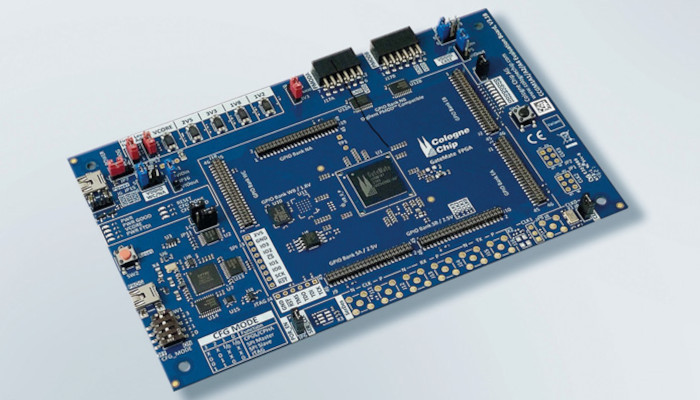

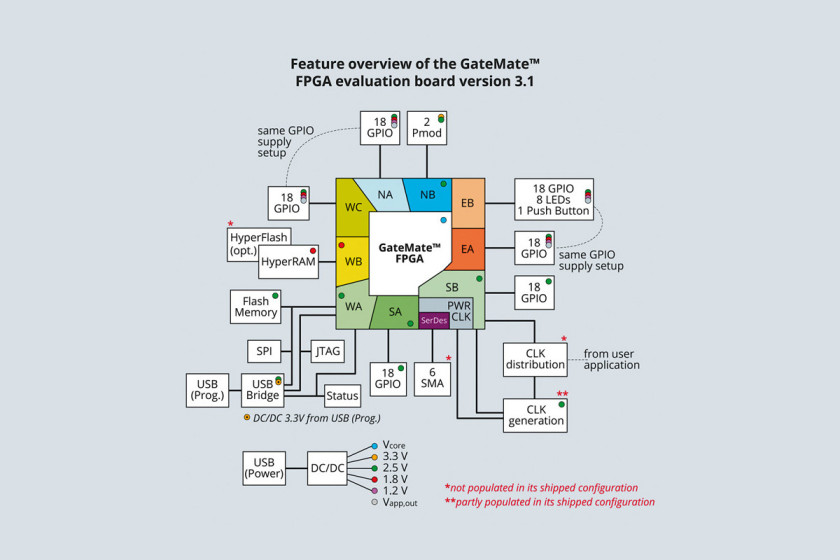

Płytka ewaluacyjna GateMate z układem FPGA GateMate A1 zapewnia wszystkie wymagane komponenty, takie jak pamięć, zegar i interfejsy oraz pozwala na regulację napięcia zasilania dla rdzenia i IO. Dzięki temu można regulować wydajność i zużycie energii przez system. Dostępne interfejsy i zasoby to:

- USB host, JTAG, SPI, SerDes, Pmod,

- wbudowana pamięć Flash i moduł HyperRAM,

- 108 linii GPIO, 7 LED,

- VCore (od 0,9 do 1,1 V) i Vio (od 1,2 do 2,5 V).

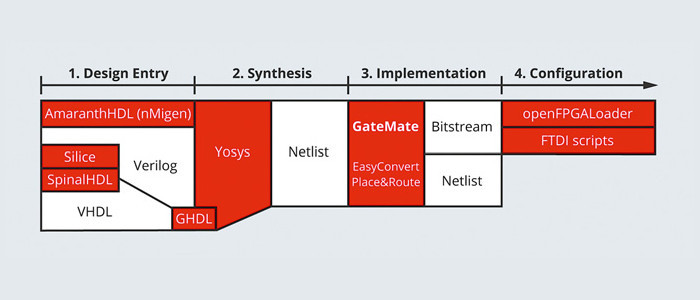

Oprogramowanie narzędziowe dostępne na GitHubie, zawiera narzędzia syntezy Verilog lub VHDL, Place & Route, generatory kodu dla symulatorów i programatora. Przykładowy cykl projektowy pokazano na rysunku.

Synteza RTL z VHDL-a lub Veriloga jest przeprowadzana przy użyciu pakietu open source Yosys. W przypadku VHDL dostępna jest wtyczka GHDL do Yosysa, można również użyć innych języków opisu HDL lub narzędzi Verilog. Synteza generuje reprezentację projektu w postaci netlisty, co pozwala na symulację i dalej na rozmieszczenie i generowanie pliku wyjściowego. Symulację synchronizacji można przeprowadzić za pomocą zewnętrznego symulatora Icarus Verilog Simulator i przeglądarki GTKWave Waveform Viewer. Plik konfiguracyjny jest ładowany do FPGA lub zewnętrznej pamięci Flash za pomocą OpenFPGALoader.

Charakterystyka GateMate FPGA:

- Zasoby logiczne: 20 000 do 500 tys. komórek,

- Dual port SRAM 1280 kbit

- Trzy tryby pracy: niski pobór mocy, ekonomiczny, wydajny (0,9, 1, 1,1 V)

- Obudowa BGA

- Wymagane tylko dwie warstwy sygnałowe na PCB

- Linie GPIO konfigurowalne jako single-ended lub LVDS.

- Mała liczba bitów konfiguracyjnych

- Konfiguracja przez 4-bit SPI

- Brak dużego poboru prądu w czasie rozruchu

- Wiele schematów taktowania

- Dual-port block RAM od 1 do 80 bitów, konfigurowalne również jako FIFO

- Można zaimplementować mnożniki o dowolnej szerokości bitowej

- SERDES 2,5 Gbit/s

- Konfigurowalne podciąganie linii pull-up/pull-down

- Wsparcie dla ADC i DAC z dodatkowymi rdzeniami IP

Codico Poland

Pawel.Pajda@codico.com

tel. 12 417 10 83 w. 21