Przykładem może być pojawienie się i szybka popularyzacja obudów fan-out WLP (FO WLP), które zapewniają wysoki stopień miniaturyzacji i zawierają między krzemową strukturą a płytką drukowaną specjalną warstwę RDL rozprowadzającą połączenia z bardzo upakowanej powierzchni krzemu na większy obszar.

Obecnie obudowy fan-out uznaje się za niezbędny element dla obudowywania złożonych struktur półprzewodnikowych wykorzystujących przelotki TSV i dla układów SoC. Kolejny krok, jaki jest zapowiadany to przejście z obróbki produkcyjnej struktur na okrągłych krążkach krzemu do prostokątnych formatów panelowych (PLP - panel-level packaging), które pozwolą na łatwiejsze pakowanie równolegle wielu struktur oraz poprawę uzysku produkcyjnego. Obudowywanie struktur w procesie panelowym jest dzisiaj rozważane przez wielu producentów układów scalonych, w tym przez większość tych, którzy przespali wejście na rynek wersji fan- -out lub zajęli się alternatywnymi rozwiązaniami jak eWLB (embedded wafer level ball grid array) i teraz są zainteresowani nadrobieniem opóźnienia technologicznego.

Układy scalone pakowane w procesie panelowym mają się pojawić na rynku już w 2018 roku, ale debiuty nie będą łatwe z uwagi na brak standardów. Każda firma ma własne rozmiary panelu i technologię montażu, a na dodatek ocenia się, że na niezbędne urządzenia trzeba wydać 120-140 mld dolarów. To duży wydatek nawet dla sporych producentów półprzewodników.

Fan-out - co to oznacza w układach scalonych?

Struktura typowego chipa o 100 wyprowadzeniach ma wielkość 3×3 mm i odległość między kolejnymi kontaktami wynosi ok. 100 μm (rys. 1). Te kontakty, które są ułożone na bokach krzemu, trzeba rozprowadzić na większą powierzchnię (fan-out) dolnej części obudowy układu scalonego o wymiarach ok. 5×5 mm. Po takim rozproszeniu raster wyprowadzeń wynosi 0,4 mm, co umożliwia montaż SMT. W przypadku chipów z przelotkami TSV, gdzie pola kontaktowe są rozmieszczone równomiernie na spodzie (raster 280 μm), fan-out zapewnia przede wszystkim zwiększenie rastra do wartości możliwej do obsłużenia w procesie SMT. W układach wielostrukturowych fan-out odpowiada też za połączenia wewnętrzne między strukturami (rys. 2).

| Rys. 1. Fan out zapewnia zwiększenie rastra wyprowadzeń do wartości akceptowalnej przez proces SMT: po lewej struktura scalona i jej wyprowadzenia, po prawej - obudowa układu scalonego | Rys. 2. Obudowa FO-PLP = brak bondingu, brak ramki montażowej i wiele struktur w jednym układzie scalonym (np. sterownik PWM, tranzystory mocy, zintegrowane podzespoły pasywne IPD) |

O co chodzi w tym panelowym montażu?

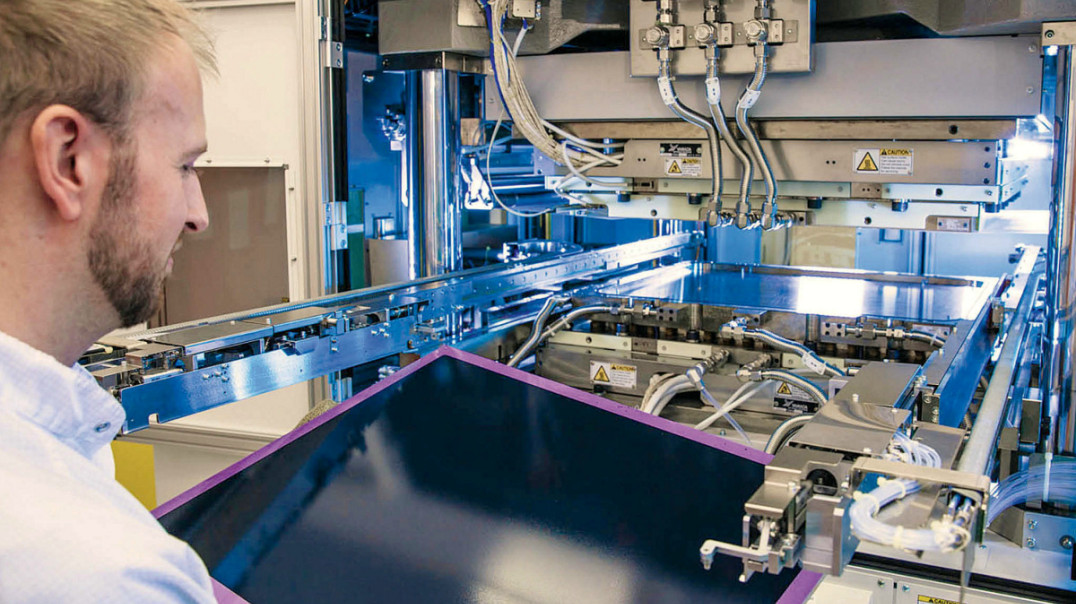

Panelowy montaż struktur FO-PLP będzie w elektronice dużą zmianą, ponieważ wiąże się z odejściem od przetwarzania okrągłych krzemowych płytek podłożowych. W uproszczeniu będzie tak, że płytka krzemowa po wykonaniu procesu produkcyjnego będzie cięta na struktury. Następnie będą one testowane i w kolejności następnie nanoszone na dużych rozmiarów materiał podłożowy (na przykład folię polipropylenową z warstwą miedzi) o prostokątnym formacie (panel) - jak na zdjęciu. Dalsze operacje technologiczne są wykonywane już nie na okrągłym płatku krzemu, ale na dużym prostokątnym panelu. Naklejone struktury są następnie laminowane (a więc zalewane tworzywem), co chroni je mechanicznie od górnej strony i tworzy obudowę. Dalej tworzona jest warstwa redistribution layers (RDL) odpowiadająca za rozprowadzenie wyprowadzeń struktur na większą powierzchnię (spód) gotowej obudowy. Warstwa RDL odpowiada też za połączenia międzystrukturowe w układach wielochipowych SoC. Na koniec na gotowej RDL nanoszone są kulki stopu lutowniczego niezbędne do montażu SMT (rys. 3).

| Rys. 3. Kolejne operacje podczas pakowania struktur metodą panelową |

Korzyści z panelu są takie, że za jednym zamachem przetwarza się więcej struktur, bo jest on znacznie większy od krążka krzemu. Uszkodzone struktury scalone są eliminowane na wczesnym etapie produkcji i tym samym nie psują do uzysku produkcyjnego w dalszych operacjach. No i wiele czynności technologicznych, wspólnych dla układów zawierających wiele struktur, co jest dzisiaj już standardem w elektronice, wykonuje się na dużej powierzchni, a więc taniej i szybciej. Warstwa RDL przypominająca bardzo cienką płytkę drukowaną łącząca kulki stopu lutowniczego z polami TSV (rys. 4) pozwala też wytwarzać anteny i falowody, które mogą być integrowane wewnątrz obudów scalonych między strukturami.

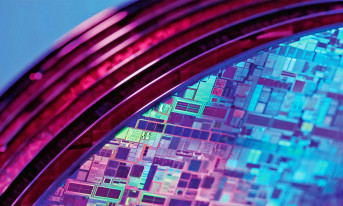

| Rys. 4. Przekrój obudowy FO-PLP | Rys. 5. Panel kontra wafer - porównanie wielkości | Rys. 6. Tak wygląda warstwa redystrybucji połączeń odpowiedzialna za "fan-out" |