Chociaż wydajność nowoczesnych układów cyfrowych stale rośnie, powiększa się znaczenie zapewnienia efektywnego przesyłu danych pomiędzy różnymi komponentami w systemie, przede wszystkim między procesorem i pamięcią, które determinuje wydajność i zużycie energii. Ciekawym rozwiązaniem może być tutaj tzw. in-memory computing (IMC), czyli technologia, która jako sposób ominięcia wąskiego gardła w przepływie danych proponuje przeniesienie części obliczeń do układu pamięci. Dopiero po wstępnej analizie wyselekcjonowane i użyteczne dane są przesyłane do procesora do dalszej obróbki. Jeszcze niedawno rozwiązania tego typu były traktowane jako kosztowna i niepewna alternatywna dla rozwiązań tradycyjnych, gdzie rozwój opiera się na stałym zmniejszaniu wymiaru technologicznego procesu. Dopiero gdy wymiary tranzystorów doszły do punktu krytycznego, a koszty projektowania i produkcji zaczęły stanowić zaporę, takie opcje doszły do głosu.

Potencjalne zastosowania IMC

Technologie IMC są szczególnie obiecujące w aplikacjach operujących na gigantycznych zbiorach danych. To przede wszystkim systemy sztucznej inteligencji, duże sieci IoT czy inteligentne auta, w których ogromna ilość danych musi być przeprocesowana w szybkim tempie. Koszty przesyłu danych stają się w tym przypadku czynnikiem blokującym. Już teraz architekci tych aplikacji zmagają się z problemami dużego poboru mocy i opóźnień. Przykładowo, autonomiczne auto może zebrać nawet 4 TB danych w ciągu dnia, a zdolność ich prawidłowej analizy w czasie rzeczywistym jest kwestią bezpieczeństwa.

Przeniesienie części obliczeń do układu pamięci ma sens z perspektywy maksymalizacji wydajności i zmniejszenia czasu reakcji systemu. Coraz częściej użycie wydajniejszych komponentów nie stanowi rozwiązania, jako że w tych aplikacjach nie można stawiać znaku równości między szybkością działania aplikacji a szybkością procesora. Zwiększenie mocy obliczeniowej procesora i pamięci fizycznie zintegrowanej z procesorem jako rozwiązanie przestaje być skalowalne, a koszty przesyłu danych niwelują zysk ze stosowania najbardziej wydajnych procesorów, prowadząc do strat energii i nieakceptowalnych opóźnień. Do niedawna głównym tematem prac nad optymalizacją tych aplikacji było, jak zmniejszyć liczbę obliczeń, natomiast teraz prace dotyczą głównie możliwości ograniczenia transferu danych. Połączenia elektryczne pomiędzy komponentami w systemach są słabo skalowalne, a zaawansowane technologie pakowania struktur chipów nadal drogie.

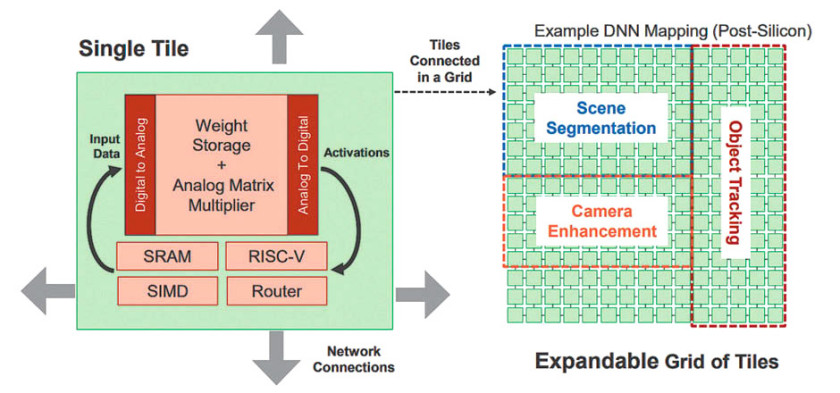

Większość popularnych typów pamięci potencjalnie może być wzbogacona o funkcje logiczne, wliczając w to DRAM, SRAM, MRAM czy ReRAM. Można wyróżnić dwa główne podejścia do integracji funkcji obliczeniowych: oparcie całego procesu na danych cyfrowych w uczeniu maszynowym lub wykorzystanie funkcji analogowych. Różnice między nimi polegają głównie na szybkości działania i precyzji. W przypadku realizacji analogowej niezbędne jest użycie przetworników DAC i filtrów analogowych. Nie jest to sposób dokładny, ale zysk na prędkości i poborze mocy kompensuje niedogodności. Uczenie maszynowe z reguły polega na wykonania szeregu stosunkowo prostych i podobnych obliczeń ogromnej ilości danych, co wymaga przede wszystkim wysokiej przepustowości i małych opóźnień.

Większość rozwiązań tego typu nadal znajduje się w stadium badań i rozwoju, jednak są też pojedyncze komercyjne wdrożenia. Przykładem innowacji w tym zakresie jest układ zaprezentowany przez firmę Mythic (USA), w którym część analogowych obliczeń odbywa się w pamięci Flash w oparciu o sieci neuronowe, czyli dane są przepuszczane przez rzędy elementów wykonujących równolegle podstawowe operacje według zdefiniowanych wag. W tradycyjnym podejściu, zbiór danych i wagi musiałyby każdorazowo zostać pobrane z pamięci do rejestrów procesora, obliczone, a wynik przesłany do pamięci. W układzie Mythic architektura opiera się na szeregu elementarnych kostek upakowanych w sieć, gdzie każda zawiera poza danymi układ logiczny do przeprowadzenia operacji na danych. Technologia jest rozwijana przede wszystkim z myślą o zastosowaniach w AI.

In-memory computing - bariery do pokonania

Jak z każdą nową technologią, przejście z fazy badań i rozwoju do pełnej komercjalizacji wymaga przezwyciężenia wielu przeszkód. Optymizm twórców tych rozwiązań nie jest podzielany przez wszystkich ekspertów, a wiele sceptycznych głosów wskazuje na techniczne problemy, które są nadal nierozwiązane. Jednym z nich są różnice w technologii układów logicznych i pamięci. Te pierwsze są nastawione na wydajność i pobór mocy, podczas gdy pamięć głównie na gęstość zapisu. Połączenie obydwu funkcji w pojedynczym układzie będzie musiało prowadzić do kompromisów.

Dodatkowo, układy pamięci mają mniejsze uzyski produkcyjne, co często wynika z mniej stabilnego procesu produkcji. Jednak w tradycyjnych zastosowaniach, dzięki korekcji błędów, jest to pomijalny problem i praktycznie niezauważalny przez użytkownika. Co innego, jeśli układ ma dokonywać obliczeń, wtedy każde przekłamanie w danych wpływa na końcowy wynik. Jeśli obliczenia te dotyczą krytycznej funkcji aplikacji, np. w inteligentnym samochodzie decydują o bezpieczeństwie użytkownika, nie jest to akceptowalne.

Kolejnym czynnikiem blokującym jest czas życia układów pamięci, które będą w tej sytuacji w intensywnym użyciu. Liczba cykli potrzebnych do korekcji wag w sztucznej sieci neuronowej w fazie uczenia może przewyższać dopuszczalną liczbę cykli zapisu/odczytu niektórych technologii.

Podsumowanie perspektyw IMC

Potencjalne obszary zastosowań IMC to segmenty rynku nadal znajdujące się na etapie rozwoju, jednak przewidywalnie o dużym potencjale wzrostu. Można się więc spodziewać, że szersze zainteresowanie rozwiązaniami IMC zacznie się, kiedy docelowe rynki jak IoT czy autonomiczne auta wejdą w dojrzałą fazę. Wykorzystanie tej szansy będzie wymagało pokonania wielu barier technicznych, przede wszystkim tej najtrudniejszej, czyli przygotowania technologii do wymogów produkcji masowej.

Jacek Dębowski