Z jednej strony składamy urządzenia z kilku gotowych zintegrowanych "klocków". Z drugiej strony przestajemy panować nad tym jak te "klocki" w środku działają. Produkując urządzenia elektroniczne musimy te współczesne "proste" konstrukcje testować.

I tu znowu, z jednej strony przy wysokim uzysku produkcyjnym układów scalonych mamy gwarancję prawidłowego działania całych bloków funkcjonalnych i wydawać by się mogło niewiele do weryfikacji, a z drugiej mamy piętrzące się trudności przy realizacji jakichkolwiek testów.

Wielowarstwowe obwody drukowane, obudowy BGA, gęstość upakowania ścieżek i wyprowadzeń wykluczają tradycyjne środki takie jak klasyczne przyrządy pomiarowe, testery ostrzowe itp. Albo nie ma możliwości dotarcia do punktu pomiarowego, albo człowiek nie jest w stanie ogarnąć takiej ilości sygnałów.

Czy można ograniczać się tylko do optycznej weryfikacji jakości montażu? Czy tylko do sprawdzenia funkcjonalnego urządzenia - działa nie działa? Taka praktyka jest już zbyt często stosowana i co praktycznie oznacza przerzucenie testu na klienta końcowego.

Użytkownik coraz częściej po zakupie znajduje wady ukryte towaru i udaje się do serwisu po wymianę podzespołów lub upgrade oprogramowania. Nikogo to już nie oburza, o ile nie grozi poważnym niebezpieczeństwem.

Nawet w wydawać by się mogło newralgicznym przemyśle samochodowym co chwila mamy do czynienia z wezwaniami do serwisu. Są jednak obszary elektroniki gdzie błąd jest niedopuszczalny, gdzie często producent musi wydać certyfikat mając pewność, że urządzenie zostało w pełni przetestowane.

Maksymalne pokrycie testami staje się więc kluczowym zadaniem w produkcji urządzeń elektroniki lotniczej, wojskowej, medycznej, samochodowej, kolejowej. W tych obszarach trzeba mieć maksymalną pewność, że urządzenie będzie działało prawidłowo również w rzadko występujących i często nie testowanych sytuacjach awaryjnych.

W artykule zaprezentowano technologię "Boundary-Scan" (B-S) zwaną też ścieżką krawędziową. Jest to metoda testowania pakietów i urządzeń elektronicznych na wszystkich etapach procesu produkcji - w fazie projektowania i w fazie wytwarzania. Pozwala ona zautomatyzować procesy generowania testów, ich realizacji i diagnostyki uszkodzeń.

Jest to, uniwersalna technologia, której wdrożenie w firmie wprowadza nową jakość testowania dla różnych produkowanych urządzeń. Można zadać sobie retoryczne pytanie, czy jesteśmy w stanie na produkcji w pełni zweryfikować urządzenie i czy istnieje jakaś jedna uniwersalna metoda testowania urządzeń elektronicznych?

Niestety zawsze trzeba stosować różne komplementarne działania, a planować je już na etapie projektowania, aby nie tworzyć trudno testowalnych urządzeń. Prezentowany w artykule sposób też nie jest lekarstwem na całe zło.

Na pewno nie zastąpi dobrze zaprojektowanego dla danej aplikacji testu funkcjonalnego wykonywanego często w oparciu o specjalnie zaprojektowane stanowisko i specjalnie wykonane przyrządy. Nie zastąpi też testerów optycznych AOI i rentgenowskich AXI.

Testy funkcjonalne mają jednak ograniczone możliwości diagnostyki, a optyczne i rentgenowskie pozwalają tylko zweryfikować jakość lutowania. Metoda B-S stanowi znakomite uzupełnienie tych klasycznych metod, w szczególności przy braku dostępu do punktów pomiarowych (obudowy BGA, druki wielowarstwowe).

Jest bowiem uniwersalną technologią automatycznego generowania, przeprowadzania testów i diagnozowania uszkodzeń, która po wdrożeniu bez dodatkowych inwestycji może być stosowana w kolejnych projektach. Boundary-Scan to nowa jakość w firmie, to wyższa jakość produktów.

IEEE1149.1

Tytułowa norma to klucz do stosowania testu B-S. Praktycznie możemy bowiem rozważać tę technologię, gdy w projekcie mamy co najmniej 2-3 układy scalone kompatybilne z tym standardem.

Są to najczęściej mikrokontrolery (np. ARM) i programowalne struktury logiczne PLD i FPGA. Od razu trzeba też rozwiać wątpliwości i stwierdzić, że już pojedyncze układy IEEE1149.1 pozwalają testować szerszy zakres niż one same, a mianowicie pozwalają testować całe ich otoczenie.

Mylna jest często wyrażana opinia - "Boundary-Scan jest nie dla nas, bo mamy na pakiecie tylko pojedyncze kompatybilne układy".

Struktura układu scalonego z mechanizmem Boundary-Scan

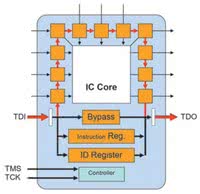

Kompatybilność z normą IEEE1149.1 oznacza, że układ jest wyposażony w mechanizm , który z punktu widzenia pojedynczego układu pozwala buforować tzn. odłączać/przyłączać poszczególne wyprowadzenia od/do struktury układu i konfigurować je w rejestr szeregowy z wejściem TDI i wyjściem TDO.

Te komórki buforowe są sterowane wewnętrznie przez TAP (Test Access Port) za pośrednictwem linii TMS, TCK i rejestru IR (Instruction Register). Każdy taki układ na pakiecie jest identyfikowany poprzez ID i może być włączony w łańcuch testowy na pakiecie. Przy czym w trakcie testów poszczególne układy mogą być pomijane w łańcuchu poprzez rejestr Bypass.

Idea Boundary-Scan

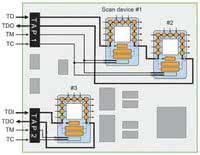

Mając zrealizowane na pakiecie łańcuchy testowe utworzone z połączonych szeregowo komórek buforowych poszczególnych wyprowadzeń, mówiąc z pewnym uproszczeniem, można metodą rejestru przesuwnego dowolnie je wysterować i odczytać ich stan.

Co więc można zrobić z Boundary-Scan?

- można przetestować samą infrastrukturę B-S (linie JTAG) na pakiecie,

- przeprowadzić test połączeń między poszczególnymi wyprowadzeniami układów,

- testować funkcjonalnie układy cyfrowe na pakiecie odpowiednio je sterując i odczytując stan wyjść m.in. pamięci,

- testować pewne bloki funkcjonalne cyfrowe i mixed-signal nie wyposażone w mechanizmy B-S, a tylko "otoczone" przez układy z B-S,

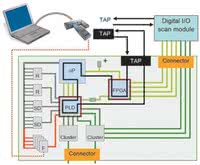

- można, używając zewnętrznych adapterów we/wy, weryfikować sygnały na złączach pakietu,

- mając dostęp do magistral poprzez linie procesora wyposażone w B-S, można programować w układzie pamięci Flash,

- programować w systemie układy PLD, FPGA, μC,

- integrować B-S z testami funkcjonalnymi urządzeń.

Czy to mało? To więcej niż mogliśmy dotychczas weryfikować klasycznymi metodami. Już w najprostszym teście połączeń z Boundary-Scan weryfikujemy połączenia pomiędzy wewnętrznymi komórkami buforowymi, a więc wewnętrzne połączenia wyprowadzeń i struktury układu, jakość lutowania, przejścia między warstwami obwodów drukowanych, ścieżki połączeń na druku. Która metoda daje więcej?

Automatyzacja testowania

Nową jakością wnoszoną przez technologię Boundary-Scan są automatyzacja procesów przygotowania testów, ich realizacji, diagnostyki uszkodzeń i ich wizualizacja na tle projektu PCB, SCH lub innej formie graficznej. W tym zakresie jest wyraźna jej przewaga nad innymi technikami testowania.

Oprogramowanie użytkowe oferowane na rynku np. przez JTAG Technologies, pozwala na automatyczne generowanie testów na podstawie listy połączeń z programów do projektowania schematów i PCB.

Ponadto producenci układów scalonych z mechanizmem B-S dostarczają opis funkcjonalny ich działania w tzw. języku BSDL. Opis ten również jest bazą dla generowania testów. Kolejnym elementem są modele dostarczane przez dostawcę technologii lub tworzone we własnym zakresie.

Generowane automatycznie lub półautomatycznie testy pozwalają skontrolować połączenia i działanie funkcjonalne poszczególnych bloków urządzenia. Kolejną zaletą prezentowanej technologii jest możliwość programowania w układzie mikrokontrolerów, pamięci Flash, PLD, FPGA.

Ten ostatni aspekt to nic innego niż powszechnie stosowane programowanie w układzie docelowym via JTAG. JTAG będąc pierwotnie tylko standardem protokołu i złącza TAP w technologii Boundary-Scan stał się jej synonimem.

Pojęcie JTAG jest też często używane w aspekcie debugowania mikrokontrolerów. Jedno jest jednak pewne, jeśli w aplikacjach jest używany JTAG w jakimkolwiek rozumieniu, to technologia Boundary-Scan jest na wyciągnięcie ręki.

Warto może rozważyć krok do przodu, krok w przyszłość i wdrożyć Boundary-Scan. Jak wygląda diagnostyka uszkodzeń? Przy informacji zaimportowanej z innych programów do projektowania schematów i PCB, opisu BSDL oprogramowanie użytkowe wykryty błąd automatycznie umiejscawia z dokładnością do wadliwego połączenia między punktami, wadliwego układu scalonego.

Podawane jest więc konkretne miejsce uszkodzenia żadna inna technika testowania nie robi tego z większą dokładnością. Tak szczegółowa diagnostyka połączona z raportowaniem błędów pozwala na produkcji na obsługę technologii Boundary-Scan przez personel średniego szczebla technicznego.

Wdrożenie Boundary-Scan

Oczywiście do wdrożenia potrzebny jest komputer z oprogramowaniem Boundary-Scan. Konieczny jest też kontroler jako układ pośredniczący między komputerem, a układem aplikacyjnym.

Taki kontroler, dla przyspieszenia operacji testowania, zazwyczaj obsługuje równolegle kilka łańcuchów Boundary-Scan. Można więc jednocześnie testować kilka pakietów lub kilka niezależnych bloków na jednym pakiecie. W zależności od potrzeb można dodatkowo stosować kontroler we-wy tzn. układ sprzęgający sygnały na złączach pakietu z komputerem.

Dostępne są przy tym różne typy kontrolerów o różnej szybkości i liczby kanałów oraz różne pakiety oprogramowania dedykowane dla projektowania lub produkcji i dla obsługi odpowiedniego zestawu planowanych operacji. Spektrum cenowe jest bardzo zróżnicowane w zależności od potrzeb i typów urządzeń.

Start dzięki specjalnym ofertom nie musi wcale być tak bolesny dla kieszeni jak się obawiamy. Ponadto Boundary-Scan to nie test szyty na miarę jednej aplikacji, to technologia testowania na etapie projektowania i produkcji wdrażana do firmy na wszystkie obecne i przyszłe projekty.

W tym kontekście to technologia relatywnie tania, gdyż inwestycja rozkłada się na lata. Boundary-Scan ma też sens dla relatywnie małych producentów, gdyż wolumen produkcji nie decyduje o jej użyteczności.

Pierwsze wdrożenie Boundary-Scan może nic nie kosztować. Darmowe narzędzie ewaluacyjne jest dostępne w Internecie. A w końcu, to co innego ma sens dla układów z dużą gęstością wyprowadzeń np. BGA do których nie możemy się niczym dobrać?

Kogo powinno zainteresować Boundary-Scan?

Technologia Boundary-Scan jest interesująca dla projektantów zaawansowanych urządzeń elektronicznych budowanych na bazie nowoczesnych mikrokontrolerów (np. ARM), procesorów DSP, programowanych struktur logicznych PLD i FPGA, układów o dużej gęstości wyprowadzeń (m.in. w obudowach BGA), druków wielowarstwowych i to zarówno na etapie projektowania, uruchamiania jak i produkcji finalnej.

Pozwala ona ze wspomaganiem komputerowym automatycznie projektować i przeprowadzać testy pakietów zawierających nawet tylko kilka układów scalonych kompatybilnych z IEEE1149.1. Technologia Boundary- Scan jeśli nie jest jedynym sposobem na przetestowanie układu, to co najmniej znacząco zwiększa pokrycie testami.

Daje gwarancje na wysoką jakość i niezawodność produkowanych urządzeń. Technologia Boundary-Scan jest interesująca dla producentów kontraktowych. Jej wdrożenie pozwala na przyjmowanie zleceń na produkcję urządzeń, które wymagają testowania Boundary-Scan. Poszerza ofertę wykonywanych usług.

Tadeusz Górnicki

WG Electronics

www.unisystem.pl