W tym celu w latach 90. ubiegłego wieku wprowadzono piętrowe struktury półprzewodnikowe - PiP. Układ taki składa się z dwóch struktur typu flip-chip ułożonych jedna nad drugą, połączonych za pomocą wire bondingu z podłożem i umieszczone w tej samej obudowie (tab. 1). Układy takie pozwalają na lepsze upakowanie powierzchni płytek PCB oraz zwiększenie prędkości przesyłu danych pomiędzy układem logicznym a pamięcią. Główną wadą, która spowodowała ograniczone stosowanie tych układów, był brak możliwości oddzielnego testowania struktur. W ten sposób wprowadzono inne rozwiązanie - układy PoP (rys. 1).

Taki układ składa się z dwóch lub więcej układów typu BGA położonych jeden na drugim. Zaletą takiego rozwiązania jest zwiększona w porównaniu do układów PiP szybkość działania przy zmniejszonym zapotrzebowaniu na energię, możliwość stosowania pamięci od różnych dostawców, o innych parametrach: prędkości, pojemności itp., zdolność do wstępnego testowania oddzielnie układu logicznego i pamięci, niską temperaturę połączenia.

Stosowanie tego typu układów może być obarczone defektami montażowymi typowymi dla układów BGA, tzw. head in pillow, voids oraz szczególnym defektem występującym tylko dla układów PoP warpage (odkształcanie). Przyczynia się on do zdeformowania pakietu PoP, co może prowadzić do braku kontaktu w połączeniach lutowniczych dla poszczególnych wyprowadzeń elementu. Spowodowany jest różnymi współczynnikami rozszerzalności cieplnej (CTE) struktury półprzewodnikowej i płytki drukowanej (laminatu) układu lub PCB.

Wraz ze wzrostem prędkości przepływu danych pojawiła się potrzeba zwiększenia ilości pamięci obsługiwanej przez procesor. Tradycyjne układy w technologii PoP (układy typu PSvfBGA PoP), które zawierają na środku układu zalaną strukturę przewodnikową z mikropołączeniami drutowymi lub strukturę typu flip-chip, pozwalają jedynie na stosowanie układów pamięci, które mają małą liczbę wyprowadzeń i duży raster - najczęściej 0,65 mm. Ograniczenia te związane są z grubością i rozmiarem samej struktury. Wielkość struktury ogranicza liczbę możliwych wyprowadzeń, a jej wysokość wpływa na raster wyprowadzeń - kulek. Im wyższa jest struktura, tym kulka musi być większa, żeby zapewnić kontakt elektryczny i mechaniczny pomiędzy układami w stosie, tym samym raster układu musi być większy, żeby zminimalizować ryzyko powstania zwarć.

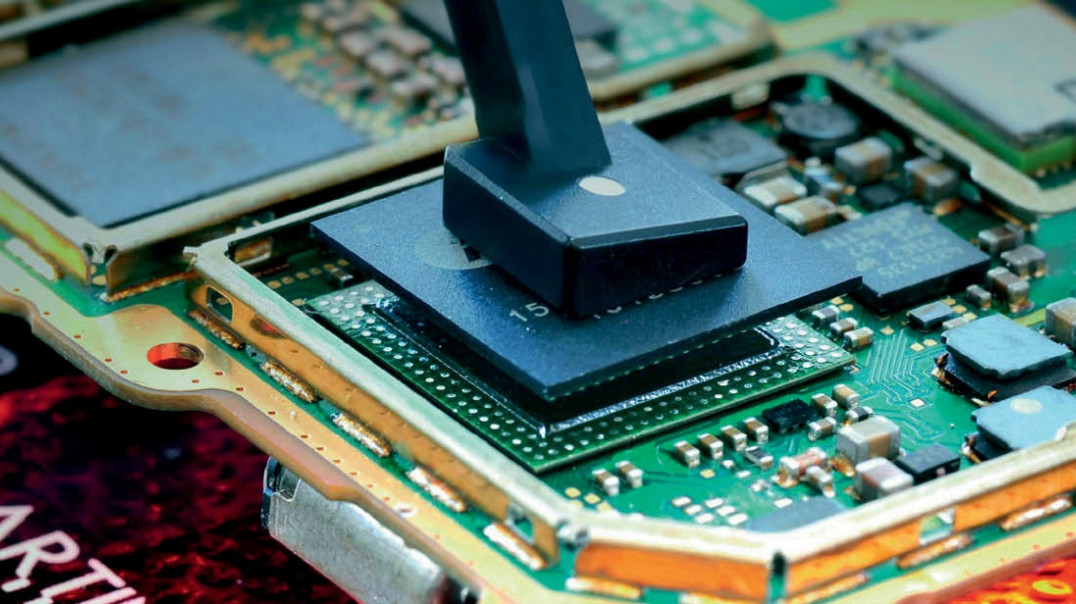

Następnym krokiem było stworzenie układu, który zwiększałby możliwości technologii PoP w zakresie poprawy wydajności. W ten sposób powstał układ TMV PoP - Th rough Mold Via Package on Package (rys. 2) stworzony przez firmę Amkor Technology. Strukturę półprzewodnikową typu flip- -chip całkowicie zalano na obszarze całego układu, pozostawiając w obudowie jedynie otwory częściowo wypełnione spoiwem (rys. 3) w celu lepszego połączenia ich z układem pamięci. Wyeliminowano w ten sposób również zależność rastra wyprowadzeń od odległości pomiędzy układami w stosie - możliwość montowania pamięci o dużej skali upakowania, nawet CSP (Chip Scale Package).

Poprawiona budowa układu pozwala na zwiększenie o około 30% wymiarów struktury półprzewodnikowej przy tej samej wielkości obudowy w porównaniu do poprzedniej generacji układów PoP. Dzięki temu możliwe jest stosowanie bardziej zaawansowanych układów typu flip-chip, co bezpośrednio wpływa na wzrost wydajności modułów. Układy TMV PoP pozwalają na umieszczanie wewnątrz obudowy: wielopoziomowych struktur, z wykorzystaniem technologii TSV i mikropołączeń drutowych (wire bonding) oraz wbudowanych elementów biernych (passive integration).

Poza wymienionymi korzyściami układy TMV PoP poprawiają możliwości montażowe modułów PoP poprzez redukcję defektu związanego z niekorzystnym odkształceniem (defekt warpage). Przeprowadzone przez firmę Amkor testy odkształcenia modułów: TMV PoP - pamięć oraz PoP - pamięć, potwierdziły doskonałą zgodność układów TMV PoP z układami pamięci. To wszystko powoduje, że technologia TMV PoP jest ciekawą alternatywą dla powszechnie stosowanych układów PoP.

Obecne moduły typu PoP mają ciągle ograniczoną liczbę wejść i wyjść (32-64). Rozwiązaniem, które zwiększa ich liczbę, jest stworzony przez firmę Invensas układ BVA PoP - Bond Via Array Package on Package (rys. 4). Innowacją w tym rozwiązaniu są połączenia BVA - wyprowadzenia w postaci drucików od strony zewnętrznej dolnego układu, które łączą dolny układ z górnym. Technologia połączeń w postaci drucików (wire bonding) oferuje dużą gęstość wyprowadzeń uzależnioną jedynie od rastra i średnicy drucika. Im cieńszy drucik tym mniejszy możliwy raster wyprowadzeń. Dla układu o wymiarach 14×14 mm i grubości 1,2 mm możliwe jest wyprowadzenie do pamięci 1440 sygnałów wejścia/wyjścia przy rastrze 0,2 mm i średnicy drutu około 50 μm.

Wyprowadzenia tych układów wykonane są w postaci miedzianych drucików. Formowane są w opatentowanym procesie przy użyciu typowych maszyn do tworzenia połączeń drutowych. Parametrem, który należy ściśle kontrolować, jest położenie każdego drucika oraz jego wysokość. Deklarowana przez producenta dokładność pozycjonowania wynosi ±15 μm (3σ). Druciki umieszczane są na płytce wokół układu flip-chip a następnie zalewane w taki sposób, że część z nich wystaje ponad powierzchnię obudowy (rys. 5). Końcowa długość wyprowadzeń wynosi 120 ±10 μm.

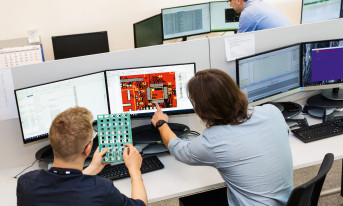

Firma Semicon w ramach Programu Operacyjnego Innowacyjna Gospodarka zrealizowała w 2013-2014 r. projekt o nazwie "Innowacyjne technologie zaawansowanego montażu powierzchniowego (SMT) płytek drukowanych". Projekt ten, dofinansowany ze środków UE, miał na celu opracowanie technologii montażu układów PoP i TMV. W projekcie korzystano z możliwości badawczych i doświadczenia Instytutu Telei Radiotechnicznego (ITR) w Warszawie.

Przeprowadzone badania pokazały, że technologia ta niesie ze sobą wiele zagrożeń, które należy ściśle kontrolować. Najważniejszymi z nich są pustki w połączeniach lutowniczych, defekt head in pillow, zimne luty, zwarcia pomiędzy sąsiednimi wyprowadzeniami oraz defekt odkształcenia warpage. Te defekty wpływają w sposób istotny na jakość i niezawodność połączeń lutowanych. W celu minimalizacji tych zagrożeń powinno się ściśle kontrolować prawidłowość nadruku pasty na płytkę PCB, czas zanurzenia oraz głębokość zanurzenia układu pamięci, prawidłowość montażu podzespołów na paście lutowniczej, parametry lutowania oraz strukturę połączeń lutowanych. Równie ważny jest odpowiedni projekt płytki, w tym przede wszystkim pól lutowniczych, które mogą być definiowane soldermaską (NSMD) lub nie (SMD) oraz projekt szablonu, który powinien zapewnić dostarczenie odpowiedniej ilości pasty lutowniczej na pady płytki PCB.

Pasty i topniki używane do montażu pamięci w modułach PoP lub TMV PoP charakteryzują się niską lepkością, która ma zapewnić dobre zwilżenie wyprowadzeń sferycznych. Niska lepkość może być powodem obniżonej adhezji elementów łączonych, a tym samym wymagane jest odpowiednie ustawienie linii montażowej, by wyeliminować mogące wystąpić wstrząsy i drgania, które mogą skutkować mikroprzesunięciami układów pamięci szczególnie w przypadku modułów PoP.

Minimalizacja zagrożeń musi być więc kompromisem pomiędzy stosowanymi materiałami na elementy PoP i TMV PoP oraz stosowanymi materiałami i parametrami w procesie montażu.

Semicon prowadzi dalsze prace w tym zakresie, zbierając doświadczenia technologiczne w trakcie prowadzonych usług produkcyjnych, montażu płytek i układów PoP.

Piotr Ciszewski

Semicon