Przepływ prądu w urządzeniach elektronicznych generuje pole elektromagnetyczne. Gdy wiele urządzeń pracuje we wspólnym środowisku, wówczas oddziaływują one na siebie poprzez pole elektromagnetyczne, a to może wpływać na ich parametry lub nawet powodować ich uszkodzenia. W celu zmniejszenia ryzyka występowania problemów związanych z kompatybilnością elektromagnetyczną, normy EMC narzucają limity ograniczające poziomy emisji EM wytwarzanych przez urządzenia, które muszą być brane pod uwagę w procesie projektowania.

Zjawiska powodujące problemy, takie jak rezonanse, sprzężenia i wycieki pola, mają jednak skomplikowaną naturę i są trudne do przewidzenia. Dlatego tradycyjne podejście do projektowania uwzględniającego EMC pociąga za sobą konieczność pomiarów.

Testy EMC są wykonywane jednak dopiero na późnym etapie procesu projektowania, już po wykonaniu prototypu. Jego budowa to znaczne koszty w procesie rozwoju produktu. Obejmują one niezbędny czas wykonania, nakład pracy i koszty materiałowe. Dlatego walka z problemami EMC na późnym etapie projektowania wymaga znacznych nakładów. Zlokalizowanie źródła w złożonym systemie elektronicznym, jest bardzo trudne i czasem wszystko, co konstruktor może zrobić, to tylko zwalczać objawy.

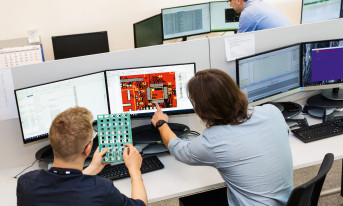

Dzięki elektromagnetycznym symulacjom komputerowym parametry urządzenia pod kątem EMC mogą być sprawdzane na wczesnym etapie cyklu projektowego. W szczególności wyniki mogą wpływać na projekt urządzenia, umożliwiając wirtualne testowanie wielu możliwych konfiguracji - na przykład różniących się ustawieniem płytki lub położeniem elementu - stosunkowo szybko i tanio.

Urządzeniem, które posłużyło za przykład w artykule jest bezprzewodowy router Cisco. Zawiera on szereg komponentów, które mogą być analizowane pod kątem kompatybilności elektromagnetycznej i które do pełnej analizy wymagają zastosowania różnorodnych metod symulacyjnych.

Zasady projektowania PCB i symulacja elektromagnetyczna

Proste i szeroko stosowane podejście pozwalające uniknąć ewentualnych problemów EMC to przestrzeganie ustalonych zasad projektowania, tzw. "rule-checking", na etapie tworzenia układu ścieżek płytki z układem na PCB. Zasady te oparte są na wieloletnich doświadczeniach zebranych przez ekspertów EMC pracujących w tej dziedzinie. Ich zadaniem jest zapobieganie projektowaniu płytek, które emitują zbyt dużo energii lub wprowadzają zbyt wiele zakłóceń do sygnałów. Oto kilka przykładów takich zasad:

- Critical Net Near Edge of Reference Plane - limit określający w jakiej odległości linie sygnałowe mogą być prowadzone od brzegu płytki lub pola "masy". Ścieżki znajdujące się blisko krawędzi mogą powodować większe emisje promieniowane lub sprzęgać się z innymi elementami.

- Critical Differential Net Length Matching and Spacing - zasada, która zapewnia, że pary linii przewodzących sygnały w modzie różnicowym mają podobną długość. Zbyt duża różnica między ścieżkami powoduje powstawanie zakłóceń typu "common-mode", a to z kolei prowadzi do problemów z EMC i "signal integrity" (SI).

- Critical Net Near I/O Net - sygnały o dużych szybkościach/częstotliwościach mogą sprzęgać się z obwodami wejściowymi i wyjściowymi, takimi jak np. interfejs USB. Ponieważ tego typu obwody wychodzą poza płytkę PCB i często biegną wzdłuż długich kabli, wprowadzają znaczne ryzyko wtórnego promieniowania.

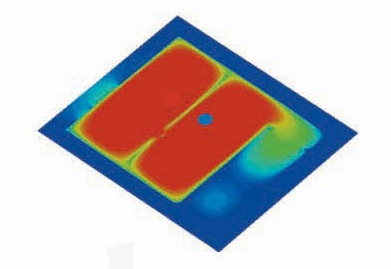

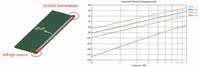

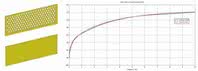

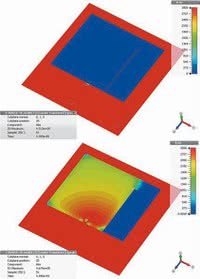

W celu zademonstrowania jak ważne jest właściwa lokalizacja linii, linia mikropaskowa długości 5 cm została zamodelowana na krawędzi płytki wykonanej na podłożu FR4 o przenikalności względnej ε=4,2, jak pokazano na rys. 1. Została on obciążona z jednej strony rezystorem 50 Ω i pobudzona szerokopasmowym źródłem o napięciu 1 V z drugiej. Pozycja linii została sparametryzowana: off set 0 mm odpowiada linii umieszczonej na krawędzi płytki, podczas gdy offset 9 mm - linii umieszczonej w jej środku.

Symulacja została przeprowadzona przy użyciu solver'a typu "Time Domain Finite Integration Technique" (FIT) dostępnego w pakiecie CST Microwave Studio. Rejestrowane było pole elektryczne o polaryzacji poziomej w odległości 3 m przy użyciu wirtualnej sondy pola. Z wykresu po prawej stronie na rysunku 1, wyraźnie widać, jak promieniowane pole zależy od częstotliwości i pozycji mikropaska. Przemieszczenie linii od środka do brzegu płytki zwiększa promieniowane pole elektryczne o ponad 30 dB, co stanowi duży wzrost emisji.

Gdy potencjalny problem zostanie zidentyfikowany, inżynier musi zdecydować, czy jest to na tyle poważne, aby uzasadnić przeprojektowanie druku. Użyteczną metodą sprawdzającą jest elektromagnetyczna symulacja pełnofalowa 3D. Projekt płytki może zostać zaimportowany przez narzędzie symulacyjne w celu zbadania pola generowane podczas pracy urządzenia. Jeśli pozycja elementu lub linii może być parametryzowana, symulacja ze zmiennym parametrem (parameter sweep) może być wykorzystana w celu zbadania, czy korzyści wynikające na przykład z oddalenia ścieżki od krawędzi płyty uzasadniają dodatkowe prace projektowe.

Zaprojektowanie złożonej wielowarstwowej płytki pod szybki układ tak, aby spełnić rygorystycznie wszystkie zasady projektowania jest bardzo trudne. Dla wielu układów, złamanie "złotych zasad" nie zawsze prowadzi jednak do problemów z kompatybilnością elektromagnetyczną, ponieważ dla różnych rodzajów urządzeń inne zestawy reguł są bardziej istotne. Na przykład w przypadku elektroniki sterującej do napędów elektrycznych nie występują te same problemy dot. kompatybilności elektromagnetycznej, co w urządzeniu wysokiej częstotliwości.

Dobrym sposobem stosowania reguł projektowania jest wydzielenie pewnych szczególnie ważnych części obwodu drukowanego, takich jak układy I/O, linie szybkiej transmisji danych i sygnały zegara. Następnie można te obszary zbadać narzędziem do sprawdzania reguł projektowania CST BoardCheck. Program sprawdza projekt płytki w oparciu o zestaw reguł projektowania i podświetla wszystkie miejsca, w których są one naruszone.

W rzeczywistym urządzeniu płytka PCB znajduje się w określonym otoczeniu elektromagnetycznym. Środowisko wokół płytki, na które składają się inne elementy, przewody i sama obudowa, mogą powodować dalsze problemy z EMC. Wiele urządzeń pracuje w przedziale częstotliwości pojedynczych gigaherców.

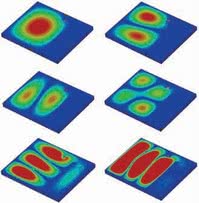

Na tych częstotliwościach, długość fali może być porównywalna z długością przewodów i rozmiarami obudowy. W obecności fal mogą więc one powodować rezonanse. Ze względu na ich charakter symulacja jest bardzo czasochłonna gdy stosuje się metody działające w dziedzinie czasu - układy rezonansowe o wysokiej dobroci Q bardzo długo "dzwonią". Do tego rodzaju problemów lepiej pasują metody symulacyjne działające w dziedzinie częstotliwości. Jako pierwszy krok w badaniu właściwości EMC obudowy routera, zbudowano bardzo prosty model, zasilany pojedynczym portem.

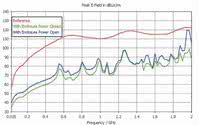

Szerokopasmowa symulacja w dziedzinie częstotliwości pokazuje występowanie wielu modów rezonansowych (rys. 2), z których każdy może przyczynić się do emisji elektromagnetycznej z urządzenia. Jeżeli istnieje zakłócający element promieniujący na częstotliwości rezonansowej, często warto przenieść go w inne miejsce na płytce. Jak pokazano na rysunku 3, przemieszczenie źródła z rogu obudowy do krawędzi powoduje zupełnie inny rozkład rezonansów.

Rozmieszczenie elementów

Często głównym źródłem problemów EMC na płytkach PCB ze względu na ich wielkość i budowę są radiatory. Zazwyczaj są one montowane w torach szybkich sygnałów, a to oznacza, że mogą się one sprzęgać ze ścieżkami w których płyną prądy o dużych częstotliwościach, a więc mogą być źródłem promieniowania wtórnego.

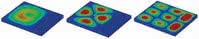

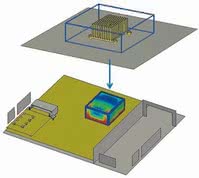

Zamiast używać prostego źródła napięcia, można użyć realistycznego modelu radiatora (rys. 4) i zbadać, jakie wytwarza on pole. Możemy też umieścić model radiatora w pełnym modelu routera, ale wtedy siatka (dzieląca analizowaną strukturę na elementarne komórki) rozciągnie się na cały obszar symulacji, co wydłuży czas obliczeń.

W przypadku modeli zawierających dużo szczegółów - na przykład układ scalony lub wielowarstwowa płytka - efektywniej jest zamodelować element i obudowę oddzielnie za pomocą metody hybrydowej dwoma różnymi solver'ami bazującymi na różnych algorytmach.

Wówczas model z dużą liczbą szczegółów jest symulowany za pomocą metody FIT w dziedzinie czasu, która nadaje się do elementów, a sonda pola bliskiego rejestruje pole wokół niego. To źródło jest następnie importowane do modelu obudowy routera (rys. 5), i wykorzystywane do symulacji solver'em liczącym metodą Macierzy Linii Przesyłowych (Transmission Line Matrix TLM), która doskonale nadaje się do analizy obudów.

Na etapie modelu szczegółowego, można próbować pewnych rozwiązań poprawiających własności EMC, takich jak dodanie punktów uziemiających lub zmiana liczby żeber radiatora. Wymiary modelu mogą być również parametryzowane. Zastosowana w CST Studio Suite metoda analizy złożonych struktur "System Assembly and Modelling" (SAM) może przenosić zmiany wartości parametru elementu i wynikające z tego zmiany rozkładu pola bliskiego z poziomu elementu do poziomu nadrzędnej symulacji kompletnego urządzenia.

W tym przypadku metoda ta została wykorzystana w celu obliczenia interakcji pomiędzy radiatorem i elementami zlokalizowanymi w lewym dolnym rogu routera. Metoda SAM pozwala wykonać automatycznie serię symulacji przez określenie zadań oraz wykorzystanie sond pola i portów do przesyłania danych pomiędzy różnymi etapami symulacji.

Projekt obudowy

Pole EM może wyciekać przez łączenia obudowy, otwory wentylacyjne i panel czołowy. Tego typu mechaniczne szczegóły są zwykle bardzo małe, co sprawia, że ich symulacja jest czasochłonna z powodu konieczności używania gęstej siatki.

W tym wypadku symulację można przyspieszyć poprzez zastosowanie zastępczych modeli kompaktowych w metodzie TLM. Skutecznie zastępują one drobne struktury równoważną reprezentacją elektromagnetyczną w postaci źródła pola, które oddziałuje z polem generowanym przez pozostałą część struktury.

Rys. 7. Wyciek na krawędzi połączenia obudowy (po lewej) i wyciek przez panel wentylacyjny (po prawej) dla częstotliwości 1,3 GHz

Rysunek 6 przedstawia porównanie szczegółowego i uproszczonego modelu panelu wentylacyjnego z otworami sześciokątnymi o krawędzi bocznej długości 1,74 i głębokości 1 mm. Model uproszczony wykazuje takie samo zachowanie jak model szczegółowy - wyniki natężenia pola są bardzo podobne w całym zakresie częstotliwości.

Modele kompaktowe nie tylko liczą się szybciej - tu na przykład czas symulacji został zmniejszony o połowę - ale także wymagają mniej szczegółowej siatki. To prowadzi do jeszcze większych oszczędności czasowych dla obiektów o dużych rozmiarach w stosunku do długości fali.

Wyniki symulacji dla całego urządzenia pokazano na rysunkach 7 i 8. Modele kompaktowe były wykorzystywane do otworów wentylacyjnych na lewej i prawej stronie urządzenia i na szwach, gdzie łączą się panele obudowy.

Przy częstotliwości 1,3 GHz, występuje pewna nieszczelność i wyciek pola przez obudowę. Jest on jednak wiele rzędów wielkości mniejszy niż pole wytwarzane przez nieosłoniętą płytkę.

Natomiast przy częstotliwości około 1,95 GHz, jest ostry wzrost pola E wokół routera i emisja promieniowania jest prawie tak duża, jak w przypadku gdyby obudowa w ogóle nie była obecna. Odpowiedzialny za to jest wyciek przez otwór gniazda zasilania. Bez otworu, jest różnica 20 dBµV/m w poziomie emisji.

Podatność (susceptibility)

Oprócz utrzymanie niskiej emisji, konstruktor urządzenia ma także zapewnić, żeby pola zewnętrzne nie zakłócały pracy urządzenia. Jedną z częstych przyczyn problemów z zakłóceniami w urządzeniach jest okablowanie. Długi przewód działa jak antena dla pól zewnętrznych wprowadzając zaburzenia do urządzenia.

Jednak tradycyjne metody symulacji 3D-EM nie są skuteczne w przypadku modelowania kabli, które mogą mieć długość kilku metrów, średnicę kilku milimetrów i złożoną strukturę wewnętrzną. Dla nich bardzo skuteczna jest symulacja hybrydowa.

Symulacja kabla może być jednokierunkowa lub dwukierunkowa, zależnie od tego, jakie sprzężenia są brane pod uwagę. W symulacji jednokierunkowej, solver oblicza tylko pola generowane przez prądy płynące w kablu lub prądy indukowane w kablu przez pola zewnętrzne.

Przy symulacji dwukierunkowej przewód jest symulowany razem z modelem urządzenia. Oznacza to, że więcej efektów jest branych pod uwagę. Np. pole promieniowane przez kabel może indukować prądy w obudowie urządzenia, a pole wtórne promieniowane przez obudowę może oddziaływać jeszcze raz na kabel. Symulacja dwukierunkowa daje fizycznie bardziej dokładne wyniki ale nie jest oferowana przez wszystkie narzędzia do symulacji kabli dostępne na rynku.

Opisywany router bezprzewodowy zawiera port USB, przez co trzeba zbadać, jak kabel USB może wprowadzać energię zewnętrznego pola EM do urządzenia. Kable USB są kablami hybrydowymi z jednym przewodem zasilania 5 V, jednym przewodem uziemienia i zestawem przewodów sygnałowych w skrętce. Ponieważ kabel jest trudnym obiektem do modelowania 3D stosuje się hybrydowy model, definiując trasę kabla i przekrój poprzeczny w module CST Cable Studio.

Wszystkie właściwości kabla można odpowiednio odwzorować, w tym stopień skręcenia skrętki, grubość i przenikalność materiału izolacji oraz konstrukcję zastosowanego ekranu. W tym przypadku użyto ekranu w postaci plecionki, ale dostępne są różne modele ekranowania o własnościach zależnych od częstotliwości. Jest również możliwość zasymulowania dowolnego ekranu na bazie zaimportowanych wyników pomiarów impedancji falowej rzeczywistego kabla.

Po zdefiniowaniu kabla USB wchodzącego do chassis routera składającego się z długiego odcinka kabla ekranowanego poza obudową i krótkiego odcinka kabla ekranowanego wewnątrz tak, jak przedstawiono na rysunku 9, przeprowadzono dwie dwukierunkowe symulacje, zmieniając jakość połączenia pomiędzy ekranem kabla i chassis.

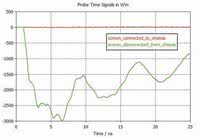

W jednej symulacji przejście pomiędzy osłoną i chassis ma niską rezystancję reprezentującą dobre połączenie, podczas gdy w drugiej, występuje między nimi wysoka rezystancja. Do pobudzenia struktury wykorzystywana jest promieniowana z zewnątrz, szerokopasmowa fala płaska, symulująca opromieniowanie struktury przez silny zewnętrzny impuls elektromagnetyczny (EMP). Do monitorowania pól wewnątrz obudowy ponownie wykorzystywane są wirtualne sondy pola.

Jak pokazano na rysunkach 10 i 11, połączenie między ekranem kabla i chassis ma istotny wpływ na podatność urządzenia na zewnętrzne promieniowanie. Dla kabla z dobrze podłączonym ekranem, zmierzona wartość szczytowa natężenia pola E jest w okolicy 15 V/m. Gdy jednak ekran został odłączony, natężenie pola E osiągnęło prawie 3000 V/m.

Z przeprowadzonych symulacji, możemy wnioskować, że połączenie ekranu kabla do chassis jest krytyczne z punktu widzenia podatności. Podczas projektowania należy zapewnić aby było ono dobrze skonstruowane oraz żeby nie podlegało degradacji w okresie eksploatacji urządzenia na np. na skutek obciążeń mechanicznych lub procesów starzenia materiału, ponieważ drastycznie zwiększa to podatność na oddziaływanie zewnętrznego pola EM.

Podsumowanie

Korzystając z narzędzi do symulacji elektromagnetycznej, projektant może badać szeroką gamę własności EMC urządzenia na długo przed wykonaniem prototypu i jego pomiarami w laboratorium. Poczynając od zautomatyzowanego sprawdzenia zasad projektowania (rule-checking) na wczesnym etapie projektowania układu ścieżek PCB aż po symulację kompletnego urządzenia analiza elektromagnetyczna staje się równouprawnioną metodą projektowania na każdym etapie procesu powstawania produktu.

Komponenty mogą być testowane metodą symulacji nie tylko osobno, ale również w złożonym układzie. Metoda "System Assembly & Modeling" (SAM) pozwala stosować różne techniki obliczeniowe do symulacji różnych części systemu. Dodatkowe wyspecjalizowane, hybrydowe metody modelowania płytek PCB, kabli i drobnych konstrukcji pozwalają symulować te skomplikowane elementy w połączeniu z resztą urządzenia.

dr Andreas Barchanski

opracowanie Jarosław Kwiatkowski

CST Computer Simulation Technology

www.cst.com