O ile o układach TSV i wersjach ze spiętrzonymi strukturami napisano już wiele, o tyle konstrukcjom PoP poświęca się mniej uwagi. Niemniej jest to obecnie jeden z najszybciej rozwijających się sposobów takiego spiętrzania, który dzięki wyjątkowej łatwości testowania zmontowanych płytek drukowanych jest chętnie stosowany przez producentów OEM. Większość typowych układów PoP zawiera jeden duży główny i złożony układ cyfrowy, będący centrum tworzonej aplikacji, który stanowi też mechaniczną bazę konstrukcyjną.

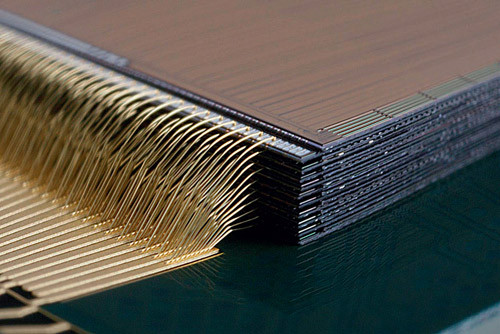

Na nim umieszczane są różnego rodzaju pamięci, a więc standardowe układy katalogowe, o ustalonym rozkładzie wyprowadzeń i tym samym niedające wielkiej dowolności rozmieszczania (rys. 1). Zatem jednym z głównych zadań projektowania jest skoordynowanie połączeń pomiędzy układem dolnym a górnymi. Staje się to dla projektanta znaczącym wyzwaniem, ma bowiem często do czynienia z układami rozmaitych producentów, a zatem o różnie rozmieszczonych wyprowadzeniach.

Bliskość struktur półprzewodnikowych w jednej obudowie sprzyja korzystaniu z szybkich połączeń szerokopasmowych i tym bardziej zmniejsza zapotrzebowanie na powierzchnię na płytce drukowanej. Spiętrzane pakiety układów scalonych zapewniają większą gęstość funkcyjną przy niezmienionej masie, ale wymagają gruntownego starania w zakresie organizacji. Planowanie układu spiętrzanych pakietów jest krytyczne w procesie opracowywania i ma znaczny wpływ na skomplikowanie i koszt gotowego produktu.

Planowanie układów o wielu podłożach

Rys. 2. Symulacje rozkładu elementów składowych wchodzących w skład PoP generowane przez program OrbitIO

Kluczem do powodzenia w tworzeniu układów PoP jest planowanie wtedy, gdy możliwości dokonywania zmian są największe. Dolny bazowy układ umieszczony w obudowie BGA powinien mieć tak rozmieszczone sygnały, aby te na obrzeżach obudowy (pad ring) były przeznaczone prawie wyłącznie do podłączenia układu górnego.

Celem jest takie rozmieszczenie pad ringu wejść-wyjść, które będzie zgodne z potrzebami łączenia obwodów logicznych rdzenia, zapewni możliwie najbardziej opłacalny sposób rozmieszczenia elementów w pakiecie, czyli najmniejszą liczbę warstw i przelotek oraz najmniejszą długość połączeń pomiędzy płytką drukowaną i wszystkimi układami w stosie.

Taki rodzaj skoordynowanego planowania projektu chipu, pakietu wieloskładnikowego, a w niektórych przypadkach również płytki drukowanej, jest wymagający i może być frustrujący - zwłaszcza przy metodach konwencjonalnych, które zostały opracowane do projektowania kolejnego, z użyciem programów narzędziowych i baz danych oddzielnych dla chipów i pakietów. Zagadnienie komplikuje się dodatkowo, gdy górny układ wykorzystuje połączenia drutowe (wirebonding), wymagające zapewnienia pól kontaktowych dla drutu.

Niestety podstawową trudnością w upowszechnianiu się układów spiętrzonych jest obecnie brak programów narzędziowych do planowania i realizacji takich konstrukcji. Poza zwykłym rozdzieleniem sygnałów konieczne jest kontrolowanie opóźnienia, odbicia i sprzężenia. Uwagi wymaga wykonanie planu zasilania pakietu układów scalonych, zwłaszcza gdy korzysta on z kilku różnych napięć zasilających, oraz rozmieszczanie kondensatorów odprzęgających na poszczególnych płaszczyznach spiętrzonej struktury.

Oprogramowanie powinno pomagać także we wprowadzaniu i ocenianiu sposobów łączenia w kontekście całego systemu, pod kątem możliwości wystąpienia pasożytniczych zakłóceń w sieci sygnałowej. Powinno też wykrywać nieciągłe ścieżki powrotne, rezonanse w płaszczyźnie zasilania i zasady odsprzęgania. To samo dotyczy wsparcia decyzji projektanta dla podziału na płaszczyzny zasilania.

Pierwsze produkty

Jednym z produktów narzędziowych EDA nowej generacji wspomagających projektowanie układów PoP jest OrbitIO Planner firmy Sigrity. Stosuje on zunifikowany model danych chip-pakiet-płytka i automatycznie rozsyła wprowadzane zmiany do sąsiednich obszarów, zapewniając natychmiastowe sprzężenie zwrotne, wpływające na cały system.

Pozwala to na optymalizację pad ringu i połączeń pakiet-pakiet z punktu widzenia parametrów, kosztów i produkowalności jeszcze przed szczegółową realizacją PoP. Na rysunku 2 pokazano kilka symulacji ułożenia wykonanych za jego pomocą. (KKP).