Rys. 1. W procesie opracowanym przez firmę SuVolta głęboko zubożony kanał uzyskuje się, wprowadzając niedomieszkowany obszar (zaznaczony na biało)

By temu zapobiec, w laboratoriach na całym świecie prowadzone są prace nad rozwiązaniami, które pozwolą ominąć przeszkody wynikające z praw fizyki. Część z tych innowacji jest dopiero w fazie rozwoju oraz badań, ale niektóre z opracowanych technologii już teraz znajdują zastosowanie w produktach dostępnych na rynku.

Jednym ze sposobów na zmniejszenie strat mocy przy jednoczesnym uzyskaniu mniejszych rozmiarów oraz większej gęstości upakowania elementów układów scalonych jest zmniejszenie wartości napięcia zasilania. Niektórzy producenci posiadają w swojej ofercie produkty, w wypadku których redukcja wartości napięcia zasilania z 1,5 V do 1,35 V pozwoliła ograniczyć zużycie energii nawet o 67%.

Aby układy logiczne mogły pracować przy jeszcze niższych poziomach napięć, przykładowo poniżej 1 V, powinien jednak nastąpić znaczący postęp w zakresie technologii produkcji układów półprzewodnikowych. Większość czołowych producentów elektroniki pracuje nad udoskonaleniem tych procesów wytwórczych, jednak ze względu na liczne trudności wciąż nie udaje się uzyskać w pełni satysfakcjonujących rezultatów.

Wynika to przede wszystkim stąd, że na etapie wytwarzania struktur półprzewodnikowych o dużej skali integracji ujawniają się zjawiska wcześniej niewystępujące. Przykładem są znaczące różnice między wartościami napięć progowych przełączania tranzystorów oraz natężeń prądów upływu w stanie wyłączenia, które występują między komponentami wytwarzanymi w obrębie różnych płytek półprzewodnikowych w ramach tego samego procesu produkcyjnego.

W celu ograniczenia strat mocy najlepiej w związku z tym byłoby, gdyby każdy układ był zasilany napięciem dostosowanym do jego parametrów. Brak możliwości realizacji tego założenia skłania producentów elektroniki do poszukiwania metod alternatywnych.

Sposoby Intela i SuVolty

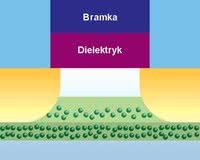

Przykładem jest Intel. Firma przez blisko dekadę pracowała nad budową tranzystorów z kanałem całkowicie zubożonym w technologii 3D FinFET (tri-gate). Główna zmiana konstrukcyjna w nich zastosowana polega na otoczeniu kanału tranzystora z trzech stron przez bramkę. Producent zapewnia, że struktura ta pozwala, unikając przedstawionych rozbieżności między parametrami poszczególnych komponentów, zmniejszyć napięcie zasilania do 0,7 V.

Oprócz tego tranzystory te cechuje charakterystyka przełączania o stromym nachyleniu, dzięki czemu wyłączają się szybciej. Charakteryzuje je również mniejszy prąd upływu oraz niższa wartość napięcia progowego w porównaniu z produktami konkurencyjnymi. Firma wciąż udoskonala tę technologię. W planach jest przede wszystkim dalsza redukcja wartości napięcia zasilania, docelowo do wartości poniżej 0,7 V.

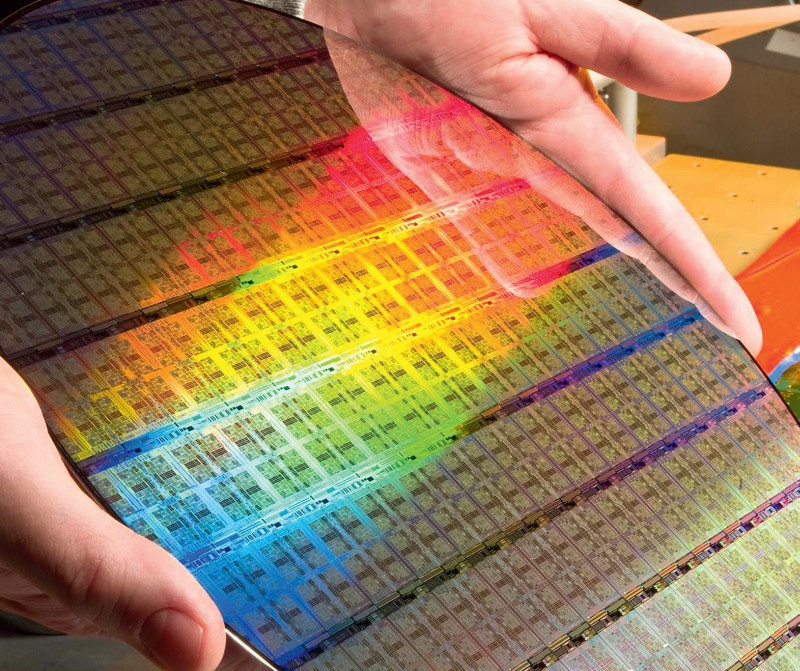

Niektórzy producenci próbują naśladować rozwiązanie wprowadzone przez firmę Intel. Ponieważ jednak opracowanie tej technologii zajęło wiele czasu oraz wymagało dużych nakładów finansowych, część z nich poszukuje też alternatywnych sposobów. Przykładem jest firma SuVolta. Wynalazła ona proces technologiczny, w którym powstają ultraniskonapięciowe układy CMOS.

Zamiast trójwymiarowej struktury producent ten uzyskuje głęboko zubożony kanał, wprowadzając w nim obszar niedomieszkowany. Unikając dzięki temu fluktuacji koncentracji domieszek, udaje się zredukować napięcie zasilania do wartości 0,6 V.

Układy w tej technologii produkować będzie Fujitsu Semiconductor już prawdopodobnie pod koniec tego roku. SuVolta w planach ma też sprzedaż licencji na wytwarzanie komponentów tego typu kolejnym firmom.

Spiętrzone struktury i przekaźniki optyczne

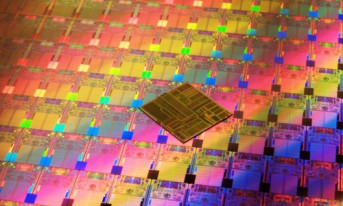

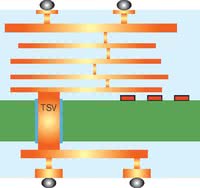

Ograniczenie strat mocy można też uzyskać, redukując liczbę, długość oraz rezystancję ścieżek sygnałowych łączących komponenty urządzenia. Możliwość taką zapewnia zastosowanie technologii pionowego spiętrzania struktur półprzewodnikowych, przykładowo opartej na metodzie TSV (Through Silicon Vias).

Producenci, którzy decydują się na wdrożenie w swoich produktach tego rozwiązania, zapewniają, że nie tylko pozwala ono zredukować straty mocy, ale również zapewnia większą szybkość transmisji sygnałów, a tym samym zwiększa wydajność obliczeniową. Ponadto dzięki zmniejszeniu rozmiaru komponentów wykonanych w tej technologii uzyskuje się też oszczędność miejsca na płytce drukowanej.

Implementacja technologii TSV jest jednak wciąż kosztowna oraz pod wieloma względami pozostaje wyzwaniem. Trudność sprawia przede wszystkim projekt takiego układu. Należy bowiem odpowiednio skojarzyć połączenia poszczególnych bloków oraz zapewnić integralność sygnałową. Alternatywą dla tradycyjnych ścieżek sygnałowych są też łącza optyczne tworzone z użyciem przekaźników optycznych.

Komponenty takie, zrealizowane z wykorzystaniem konwencjonalnych elementów optycznych, są już m.in. stosowane w superkomputerach firmy IBM. W przyszłości natomiast układy scalone będą prawdopodobnie wyposażane w specjalizowane mikrooptyczne przekaźniki. Elementy takie w technologii SiGe wykonuje już m.in. firma Kotura. Zawierają one wszystkie typowe komponenty układów optycznych, w tym soczewki, filtry oraz modulatory.

Nowe materiały

Szansą na zmniejszenie strat mocy w układach scalonych jest również użycie do ich budowy wcześniej niestosowanych materiałów. Przykładem są ferroelektryki, które wykorzystano do budowy pamięci ferroelektrycznych (FRAM). W porównaniu z innymi rodzajami pamięci nieulotnej, zwłaszcza pamięci Flash, pamięci FRAM charakteryzuje mniejszy pobór energii w czasie odczytu oraz zapisu danych.

Ponadto cechuje je duża liczba cykli zapis/odczyt oraz duża szybkość zapisu danych. Materiałem, który może zrewolucjonizować produkcję układów scalonych, może stać się również InGaAs (arsenek indowo-galowy). Przykładowo firma Intel zamierza zastosować ten materiał do budowy tranzystorów w technologii tri-gate.

Dzięki temu zdaniem tego producenta możliwe stanie się zmniejszenie napięcia zasilania do nawet 0,5 V. W dłuższej perspektywie czasowej również materiały, których nazwy dotychczas wymieniane były głównie w kontekście literatury fantastycznonaukowej, mogą wpłynąć na technologię produkcji układów scalonych.

Świadczą o tym bowiem wyniki badań prowadzonych na razie głównie w ośrodkach naukowych oraz na uczelniach. Chodzi przede wszystkim o materiały na bazie węgla, a w szczególności o tzw. nanorurki węglowe oraz grafen.

Nanorurki i grafen zrewolucjonizują elektronikę

Rys. 2. Zmniejszenie strat mocy umożliwia też technologia pionowego spiętrzania struktur półprzewodnikowych, przykładowo oparta na metodzie TSV (Through Silicon Vias)

Te pierwsze, o strukturze w formie pustych grafitowych walców o średnicy kilku nanometrów, mają liczne właściwości interesujące pod względem ich wykorzystania do konstrukcji układów scalonych. Nanorurki są lekkie, ekstremalnie wytrzymałe mechanicznie (są kilkadziesiąt razy bardziej wytrzymałe na rozciąganie niż stal) oraz charakteryzuje je bardzo duża przewodność cieplna.

Ponadto ciepło generowane w wyniku przepływu prądu przez nanorurki stanowi jedynie ułamek ilości ciepła wydzielanego przykładowo w miedzi. Wszystko to sprawia, że coraz bardziej prawdopodobne jest, że w przyszłości to głównie z nanorurek będą wykonywane połączenia w obrębie układów scalonych o bardzo małym poborze mocy.

Naukowcy podkreślają ponadto, że wciąż właściwości tego materiału nie są do końca zbadane. Podobnie jest w przypadku grafenu, który jest formą grafitu. Występuje on w postaci pojedynczej warstwy atomów węgla i charakteryzuje się bardzo dobrym przewodnictwem cieplnym oraz elektrycznym.

Naukowcy zbadali przykładowo, że ruchliwość elektronów w grafenie, także w temperaturze pokojowej, ponad sto razy przewyższa ruchliwość tych cząstek w krzemie. Znaczenie tego materiału dla rozwoju nie tylko elektroniki zostało potwierdzone w 2010 roku, gdy odkrywcom grafenu przyznano Nagrodę Nobla z fizyki.

Dlatego nad wykorzystaniem grafenu, nanorurek oraz innych materiałów na bazie węgla w produkcji układów scalonych pracują już również czołowi producenci elektroniki. Wśród nich jest m.in. IBM. Inżynierom z tej firmy udało się już nawet zbudować tranzystor na bazie tego materiału.

Podsumowanie

Jeszcze innym sposobem na redukcję strat mocy w układach cyfrowych jest dynamiczne zarządzenie poborem mocy. Realizuje się to, wyposażając mikrokontrolery oraz inne układy cyfrowe, zwłaszcza typu SoC, w jednostki umożliwiające regulację ich parametrów pracy. Chodzi przede wszystkim o napięcie zasilania oraz częstotliwość taktowania, od których bezpośrednio zależy pobór prądu w stanie aktywnym.

To ostatnie ogranicza się, dopasowując wartość napięcia zasilania oraz częstotliwość pracy do aktualnych wymogów pod względem mocy obliczeniowej. Zwykle parametry te są regulowane oddzielnie dla poszczególnych bloków funkcjonalnych urządzenia w zależności od ich obciążenia. Jeżeli taki obwód nie jest w danej chwili niezbędny lub w ogóle nie jest używany, zwykle zostaje wyłączony.

Projektowanie układów scalonych pod kątem ograniczenia strat mocy jest złożonym zagadnieniem. Wymaga od konstruktorów szerszego spojrzenia na to zagadnienie, a poza tym dla osiągnięcia jak najlepszych wyników powinni oni posiadać rozległą wiedzę na temat różnych możliwości osiągnięcia tego celu.

Wymaga to śledzenia nowinek technologicznych oraz koncepcji rozwijanych w laboratoriach oraz ośrodkach naukowych. Dodatkowym utrudnieniem jest to, że czasem ich możliwości nie są prezentowane pod kątem ich wykorzystania w konstrukcji układów elektronicznych. Wymaga to od projektantów dodatkowej pracy w zakresie przeniesienia nowych rozwiązań na ten grunt.

Monika Jaworowska