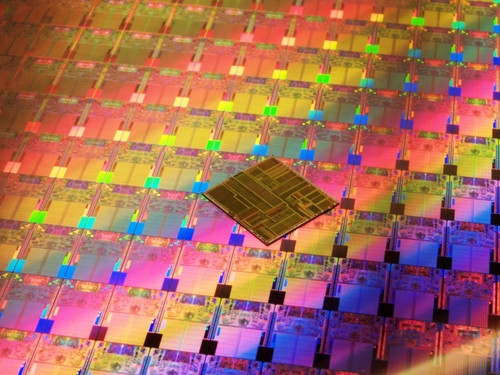

Oszczędności wewnątrz układów scalonych

Pobieraną przez cyfrowe układy scalone moc ze źródła zasilania można podzielić na dwie grupy statyczną oraz dynamiczną, która towarzyszy zmianie stanów logicznych. W znakomitej większości przypadków moc statyczna jest znacznie mniejsza od dynamicznej, dlatego większość zagadnień związanych z redukcją mocy skupia się na minimalizacji drugiego składnika.

W celu zmniejszenia poboru mocy dynamicznej stosowane jest skalowanie wielkości tranzystorów zawartych na strukturze półprzewodnikowej, za pomocą modeli matematycznych wiążących pobieraną moc z szerokością bramki tranzystora. Dokonywane zmiany nie dotyczą całości układu, ale poszczególnych komponentów, w zależności od miejsca i pełnionego zadania.

To dlatego, że redukcja rozmiarów tranzystora skutkuje zwiększeniem opóźnień w przesyłaniu sygnałów. Z tego powodu ze ścieżek o krytycznym znaczeniu dla szybkości systemu usuwa się elementy najbardziej oszczędne po względem pobieranej mocy. Inną metodą jest budowanie alternatywnych oszczędniejszych, ale wolniejszych dróg przepływu sygnału, które wybierane są w zależności od aktualnych wymagań systemu i wykonywanych zadań.

Innymi znanymi metodami jest zmniejszanie częstotliwości taktowania jak również obniżenie napięcia zasilającego. W układach synchronicznych można tak zmodyfikować konstrukcję, aby zegar działał z połową częstotliwości i synchronizował zdarzenia używając zarówno zbocza narastającego, jak i opadającego. Taki układ może działać przy mniejszym napięciu zasilającym, a redukcja pobieranej mocy, będąca iloczynem stopnia zmniejszenia częstotliwości zegara i napięcia zasilania, w tym wypadku rośnie w tempie wykładniczym.

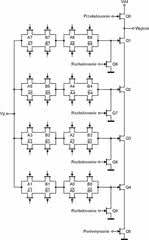

Na pobór mocy w układach scalonych ma także wpływ rozmieszczenie tranzystorów w strukturze. Dlatego dąży się do takiego ich rozplanowania, aby jak najbardziej zminimalizować liczbę przełączeń. Jedną z głównych zasad jest ułożenie tranzystorów bliżej obwodów wyjściowych obwodu, jeśli mają być przełączane w kolejności. Ma to zapobiegać efektowi domina, w którym aktywność jednego tranzystora ma niekorzystny wpływ na inne. Realizacja takiego założenia dla komparatora została przedstawiona na rys. 1.

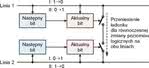

Propozycje oszczędzania energii wiążą się też z redukcją aktywności przełączania elementów logicznych, na przykład przerzutników. W tych elementach moc tracona jest podczas zmiany stanów wewnętrznych i wyjść oraz w wyniku oddziaływania sygnału taktującego. Oszczędność poboru mocy daje wstrzymanie sygnału taktującego, gdy stan wejść nie wywoła zmiany stanu wyjść. Istnieją dwie wersje realizacji tego pomysłu.

W pierwszej wersji oba wyjścia przerzutnika zawierają własne obwody bramkujące zegar zrealizowane z wykorzystaniem komparatora sprawdzającego aktualny i poprzedni stan wejść. Jeśli sygnały są takie same, dodatkowe elementy logiczne wstrzymują sygnał taktujący. Druga wersja różni się od pierwszej tym, że wyjścia zawierają tak samo zbudowany, jak w pierwszym przypadku, ale wspólny obwód bramkujący. Inny rodzaj oszczędnego przerzutnika wykrywa sytuację, gdy zmiana stanu wejść nie wywoła zmiany stanu wyjść i wstrzymuje zbędne przełączanie wewnętrzne.

Trzeci typ przerzutnika jest wrażliwy zarówno na taktujące zbocza narastające, jak i opadające, dlatego też może działać z dwukrotnie mniejszą częstotliwością przebiegu zegarowego.

Ciekawym pomysłem jest zarządzanie napięciem zasilania różnych komponentów w zależności od stopy błędu generowanej przez nie w obliczeniach. Jeśli przekroczony zostaje próg niedokładności, napięcie zasilania danego komponentu jest zwiększane o jeden stopień, aż do osiągnięcia żądanego poziomu. Wymagana jest w tym przypadku obecność dodatkowych elementów wykrywających i korygujących błędy. Najczęściej są to przerzutniki pracujące z obniżoną częstotliwością sygnału taktującego, porównujące sygnały ze swoich wyjść z wyjściami przerzutnika w obwodzie głównym.

Oszczędności mocy przy transmisji sygnałów

Rys.3. Powtórne wykorzystanie ładunku statycznego, nagromadzonego na jednej linii, jest realizowane poprzez zwarcie ścieżek pomiędzy transmisją jednego bitu i drugiego

Popularnym sposobem oszczędzania energii jest zmniejszenie częstotliwości przełączania sygnałów na magistrali cyfrowej łączącej poszczególne bloki poprzez tzw. schematy kodujące. Wybierając odpowiedni sposób reprezentacji (kodowania) danych cyfrowych, można osiągnąć taki stan, że na magistrali przy każdym takcie zegara zmienia się tylko jeden bit. Który to będzie bit - zależy od aktualnego słowa na magistrali i słowa, które będzie transmitowane.

Straty mocy mogą być również wynikiem istnienia przesłuchów między ścieżkami. Można je wyeliminować poprzez ekranowanie połączeń za pomocą dodatkowej ścieżki o stałym potencjale umieszczoną pomiędzy dwiema ścieżkami sygnałowymi. Zapobiega to przesłuchom w przypadku równoczesnej zmiany poziomu logicznego w dwóch sąsiadujących ścieżkach danych. Stosować można również kodowanie zapobiegające równoczesnym zmianom poziomów logicznych na sąsiednich ścieżkach.

Zamiast tradycyjnych napięć ±5V lub ±12V reprezentujących stany logiczne, na potrzeby transmisji można stosować mniejsze wartości. Sygnał wyjściowy jest wówczas dzielony na dwa sygnały o przeciwnej polaryzacji, ograniczone żądanym zakresem napięć. Odbiornik traktuje różnicę napięć pomiędzy dwoma przesyłanymi sygnałami jako aktualny stan logiczny. Należy zaznaczyć, że ten sposób jest odporny na wspomniany powyżej rodzaj przesłuchu.

Kolejnym sposobem ograniczania energii podczas transmisji sygnałów cyfrowych jest mechanizm segmentacji, za pomocą, którego dzieli się magistralę na szereg segmentów połączonych ogniwami, co umożliwia regulację ruchu między sąsiednimi częściami (rys. 2). Ogniwa są aktywowane niezależnie od siebie, zapewniając wyłączenie nieużywanych części magistrali. W idealnym przypadku elementy komunikujące się ze sobą często powinny leżeć przy tych samych segmentach.

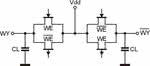

Oprócz zabiegów, których celem jest zmniejszenie aktywności układu i napięcia zasilania można wykorzystać istniejące ładunki statyczne w celu wyeliminowania konieczności tworzenia nowych. Są one przenoszone ze ścieżki, która przetransmitowała bit o wysokim poziomie napięcia, do ścieżki o niskim stanie logicznym, która taki bit będzie transmitować. Odbywa się to poprzez wstępne zwarcie obu ścieżek. Realizacja tego sposobu uwidoczniona jest na rys. 3. Podobną zasadę oszczędzania ładunku statycznego można zastosować do zbudowania bardziej złożonych obwodów, co przedstawiono w rys. 4.

Oszczędności w układach pamięci

Rys.4. Ładunki statyczne są gromadzone w kondensatorach przy wyjściach obwodu, a sygnały wejściowe determinują stan sygnałów wyjściowych poprzez załączanie i wyłączanie przełączników tranzystorowych

Efektywnym sposobem minimalizacji rozpraszanej energii w przypadku układów pamięci jest aktywowanie tylko tych fragmentów obwodów, które są potrzebne w danym momencie. Oszczędność uzyskuje się poprzez partycjonowanie pamięci na szereg komponentów o niezależnym od siebie dostępie. Drugim rozwiązaniem jest redukcja liczby operacji na pamięci. Uzyskuje się to poprzez dołożenie jednostki buforującej (cache), obsługującej najczęściej występujące odwołania.

W celu jeszcze lepszej poprawy współczynnika wykorzystania energii w pamięci pomocniczej można przechowywać instrukcje w takim porządku, w jakim są wykonywane, a nie, w jakim zostały skompilowane. Powoduje to ogólne zmniejszenie liczby odwołań do pamięci. Stosuje się także metody przewidywania miejsca wystąpienia danej instrukcji. Ma to na celu ograniczenie przeszukiwania struktury bufora lub pamięci. Odwołania pojawiające się najczęściej mogą również zostać dołączone do cyklicznej kolejki.

Zmiany dynamiczne podczas pracy

Do obsługi obwodu decydującego o napięciu zasilania dla poszczególnych bloków funkcjonalnych można wykorzystać przerwania. Bazujący na nich algorytm decyzyjny powinien mierzyć czas zajętości procesora podczas przerwania i na tej podstawie oceniać możliwą zajętość wynikającą z kolejnego przerwania. Prędkość taktowania procesora i poziom napięcia są następnie optymalizowane w zależności od wyników tych oszacowań. Najprostszym sposobem sprawdzenia, czy możliwe są zmiany napięcia zasilającego, jest sprawdzanie, jak długo procesor jest bezczynny.

Jeśli założony próg został osiągnięty następuje redukcja napięcia zasilania i częstotliwości taktowania. W przypadku, gdy jednostka jest zajęta dłużej, napięcie zasilania i częstotliwość taktowania są zwiększane. Ulepszona wersja tego algorytmu sprawdza zajętość jednostki w zadanych oknach czasowych. Czas bezczynności jest uśredniany i względem tego podejmowana jest decyzja co do obniżenia, podwyższenia lub pozostawienia bez zmian bieżących wartości napięć i częstotliwości.

Szybkość taktowania jednostki centralnej i napięcie zasilania mogą być różnie przydzielane do różnych zadań, w zależności od czasu wykonania każdego z nich. Monitorowana może być częstość zdarzeń z użyciem sprzętowego licznika wykonania, a wyniki przypisywane do poszczególnych procesów. Algorytmy heurystyczne dostosowują następnie taktowanie do każdego z procesów, bazując na ich poprzednich wynikach z licznika. W tym celu konieczne jest skonstruowanie tablicy z kombinacją częstości zdarzeń, podzieloną względem dziedziny częstotliwości.

Usprawnienie tego algorytmu polega na podziale obciążeń na epizody interaktywne i epizody bez aktywności ze strony użytkownika. Dla każdego z nich inaczej przeprowadzane są metody liczenia wykonań. Dla epizodów interaktywnych taktowanie jest dostosowywane w zależności od obciążenia oraz wymaganego progu szybkości reakcji na zadania dla danego użytkownika lub innych systemów, z którymi omawiane urządzenie współpracuje.

Możliwe jest również podzielenie każdego realizowanego przez procesor zadania na odcinki czasowe o stałej długości. Algorytm obsługi tego zadania przydziela wówczas okna czasowe o zmniejszonej szerokości pozwalającej na wykonanie zadania w preferowanym przedziale czasu. Ten przedział jest tworzony poprzez odjęcie najgorszego czasu wykonania i czasu, który upłynął w zależności od aktualnego okna. Rozwinięciem tego rozwiązania jest algorytm wybierający szybkość taktowania w każdym cyklu wykonywania zadania, bazując na prawdopodobieństwie rozmieszczenia obciążenia mierzonego w poprzednich cyklach.

W jednej z wersji tego rozwiązania zakłada się, że pobierana przez układ energia jest proporcjonalna do kwadratu napięcia zasilającego, w drugiej, że jest zależna od kwadratu częstotliwości taktowania. Alternatywny algorytm wykorzystuje fakt, że procedury programowe zawierają wiele dróg wykonawczych różniących się poborem energii. Algorytm określa najgorszy przypadek i uśrednia cykle dla różnych ścieżek. Następnie wstawia instrukcje zmieniające częstotliwość taktowania jednostki centralnej na początku wykonywania każdej ze ścieżek. Jeszcze innym rozwiązaniem jest wstawienie do programu punktów pomiarowych.

Jeśli licznik czasu między poszczególnymi punktami przekroczy ustalone progi, zmienia się częstotliwość taktowania jednostki.

Oszczędności przy oczekiwaniu na dostęp do pamięci

Gdy odwołania do pamięci dominują w ogólnym czasie wykonywania instrukcji, możliwe jest okresowe spowalnianie procesora w oczekiwaniu na dane. Fakt odwołania do pamięci jest wykrywany i obliczana jest liczba pominięć bufora. Następnie zwiększany jest stan jednego z trzech liczników analizujących liczbę pominięć. Funkcja opóźniająca wyraża użycie pamięci w kodzie instrukcji jako ważoną sumę tych trzech liczników. Trzeci licznik, zwiększany przy każdym pominięciu bufora, ma największą wagę. Dla stałych przedziałów czasu algorytm heurystyczny porównuje wyniki, czyli prowadzi do obliczenia w odniesieniu do górnego i dolnego progu.

Jeśli wykorzystanie pamięci jest większe od górnego progu, zmniejszana jest częstotliwość i napięcie zasilania. Wartości te są zwiększane w przypadku wyniku leżącego poniżej dolnego progu. Inne rozwiązanie polega na wykrywaniu wartości licznika programu, podczas których występują częste opóźnienia z powodu operacji na pamięci. Jeśli takie miejsce zostanie wykryte, jednostka wprowadza czasowy stan, w którym zlicza liczbę cykli zwłoki. W przypadku przekroczenia progu początkowa wartość licznika programu zostaje oznaczona jako gorąca.

Następnym razem, gdy licznik programu osiągnie tę wartość, automatycznie zostanie zmniejszona częstotliwość taktowania i napięcie zasilania jednostki. Kolejny sposób to obliczanie czasu pracy jednostki z wykorzystaniem jej liczby instrukcji, średniej wartości z cykli wykonania każdej instrukcji i częstotliwości taktowania. Czas wykonania programu poza jednostką jest funkcją liczby instrukcji na pamięci, średniej z cykli ich wykonania i częstotliwości taktowania pamięci. Używane są tu sprzętowe liczniki pominięcia bufora pamięci. Alternatywnym do przedstawionych jest algorytm bazujących na czasie wykorzystania jednostki, a nie pamięci.

Mierzone jest tu tempo wykonania instrukcji w celu określenia obciążenia.

Niezależnie taktowane obszary

Zamiast zmieniać taktowanie dla całego układu, można wprowadzić architekturę z niezależnie taktowanymi obwodami funkcjonalnymi. Systemy takie nazywane są lokalnie synchronicznymi, a globalnie asynchronicznymi. Jedyny problem, który ogranicza możliwość takiego dzielenia układu na mniejsze fragmenty, to kłopoty z zapewnieniem odpowiedniej komunikacji między modułami.

Architektura adaptacyjna

Kolejnym sposobem na ograniczenie energii jest buforowanie adaptacyjne. Bufor ten przechowuje w sobie najczęściej wykorzystywane dane, co umożliwia wyłączenie napięcia zasilającego dla pewnego obszaru komórek pamięci. Decyzja o załączeniu zasilania następuje przy wykorzystaniu obwodów sprzętowych monitorujących liczbę pominięć bufora, czyli przypadków, gdy program odwoła się bezpośrednio do pamięci z pominięciem danych podręcznych. Po osiągnięciu założonego progu pominięć aktywowane są wyłączone wcześniej podzespoły. Niektóre rodzaje komórek pamięci wymagają ciągłego zasilania w celu utrzymania informacji, dlatego też dla nich stosuje się inne rozwiązanie.

Na podstawie danych technicznych układu pamięci wybierane są napięcia zasilania dla stanu aktywnego, podtrzymującego zawartość i nieaktywnego. Algorytm sterujący zapobiegania przesyłaniu danych do pamięci w sytuacji, gdy komórka jest w stanie podtrzymania. Zapobiega to przekłamaniom. Jeśli zawartość komórki pamięci musi być zmieniona następuje to tylko wtedy, gdy napięcie jest odpowiednie do zapisu (rys. 5).

Podsumowanie

Zarządzanie poborem mocy przez układy elektroniczne obejmuje coraz więcej zagadnień zarówno po stronie sprzętu jak i oprogramowania. Komplikacja algorytmów zapewniających minimalne zużycie energii już dzisiaj jest duża i zapewne w przyszłości będzie jeszcze większa. To dlatego, że oprócz istnienia przykładowych rozwiązań przedstawianych w tym artykule, nadal istnieje potrzeba prowadzenia dalszych prac. Minimalizacja poboru mocy w elektronice łączy w jedną całość różnorodne dokonania z zakresu fizyki, elektrotechniki, logiki, architektury systemów i informatyki.

Jest bardzo prawdopodobne, że w przyszłości takie interdyscyplinarne prace doprowadzą do pokonania większości limitów, wydających się dzisiaj niepokonalnymi barierami fizycznymi.

Damian Krzesimowski