Minimalizacja poboru mocy to proces znajdowania kompromisu pomiędzy tym, ile energii pobiera układ mikrokontrolera a tym, jaką zapewnia wydajność przetwarzania. W wielu aplikacjach konieczne jest jednoczesne zapewnienie dużej wydajności i niskiego poboru mocy, co prowadzi do sprzeczności i konieczności szukania kompromisu.

Pierwszym i naturalnym rozwiązaniem jest wykorzystanie dostępnych trybów oszczędnościowych, po to, aby mikrokontroler spędzał jak najwięcej czasu w uśpieniu, a w krótkich okresach wybudzenia zapewniał dużą wydajność przetwarzania. Tę regułę znają wszyscy, ale w praktyce sumaryczne zużycie energii zależy w dużej mierze od tego, jak dobrze projektant jest w stanie poradzić sobie z efektywnym wykorzystaniem trybów oszczędnościowych oraz skróceniem czasu działania aplikacji, gdy korzysta ona z pełnej wydajności.

Przy dobrze przemyślanym projekcie można też korzystać ze spowalniania zegarów taktujących, bramkowania zegara dla nieużywanych układów peryferyjnych oraz wielu różnych trybów usypiania działania mikrokontrolera. Te techniki także są dzisiaj znane, niemniej, aby przynosiły one duży zysk energetyczny trzeba też pamiętać o drobnych szczegółach, jak na przykład o tym, że po wyjściu z trybu uśpienia trzeba rekonfigurować ustawienia układów peryferyjnych i zegarów i inicjować działanie wielu obwodów wewnętrznych mikrokontrolera i proces ten zabiera czas, a w konsekwencji także energię ze źródła zasilania.

Dynamiczne skalowanie napięcia i DMA

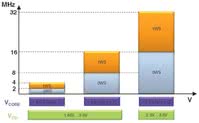

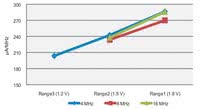

Rys. 2. Zmiana napięcia zasilania rdzenia pozwala sterować wydajnością przetwarzania w szerokim zakresie

Pobór mocy przez działający mikrokontroler jest proporcjonalny do wartości napięcia zasilającego i częstotliwości taktowania. Im mniejsze napięcie zasilania oraz niższa częstotliwość taktowania, tym mniejsze zużycie energii. Ustalenie, jaka kombinacja napięcia i częstotliwości spełnia wymagania aplikacji, co do uzyskania niezbędnej wydajności nie jest proste.

Ponadto aby możliwe było dynamiczne skalowanie napięcia zasilania podczas pracy, musi to umożliwiać architektura sprzętowa, a dokładnie stabilizator o programowalnym napięciu. W przypadku układów z serii STM32L projektant ma do dyspozycji trzy napięcia: 1,2, 1,5 i 1,8 V (rys. 1). Różnica w poborze mocy pomiędzy skrajnymi napięciami zasilania sięga 30% (rys. 2), co przekonuje, że warto z korzystać z tej możliwości.

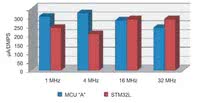

Rys. 3. Wydajność przetwarzania w μA/DMIPS lepiej oddaje różnice pomiędzy mikrokontrolerami różnych producentów

Wydajność przetwarzania najczęściej jest określana w danych technicznych przez producentów jako współczynnik μA/MHz, który nie daje pełnego obrazu. Lepiej mówić o liczbie instrukcji wykonywanych w czasie jednej sekundy przy danej częstotliwości zegara, bo w ten sposób unika się niedokładności związanej np. z cyklami oczekiwania na dostęp do pamięci, które pojawiają się przy dużej częstotliwości taktowania.

Gdy rozważa się wybór mikrokontrolera do aplikacji można zauważyć, że w pierwszym przybliżeniu układ STM32L zapewniający 296 μA/MHz może wydawać się gorszy od innego procesora, zapewniającego wg danych jego producenta, jedynie 180 μA/MHz. Obraz ten się zmienia, gdy przyjrzymy się nie megahercom, ale wydajności w μA/DMIPS, która jest wartością oczyszczoną z wpływu architektury ALU na wynik.

Wówczas okazuje się, że w zależności od częstotliwości zegara raz jeden układ wypada lepiej raz drugi (rys. 3). Znając zależność μA/DMIPS dla różnych częstotliwości zegarowych można posługując się skalowaniem napięcia zmniejszać dodatkowo zużycie energii dla taktowania niższego niż maksymalne i wybierać optymalne rozwiązania.

Duże możliwości oszczędzania kryją się także w układzie DMA, który pozwala transmitować dane w czasie, gdy procesor jest uśpiony i wybudzać go tylko, gdy zajdzie potrzeba przetworzenia zabranego kompletu. DMA odciąża też CPU i zmniejsza zapotrzebowanie na pracę z pełną wydajnością.

Pamiętaj o energii koniecznej do wybudzenia CPU

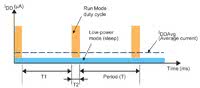

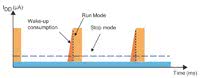

Rys. 5. W praktyce szacowanie sumarycznego poboru prądu musi uwzględniać energię traconą na wybudzenie CPU (wake-up)

Aplikacje o niskim poborze mocy najczęściej bazują na okresowym wybudzaniu CPU po to, aby przetworzył szybko dane i ponownie przeszedł w tryb uśpienia. Stąd szacunki całkowitego poboru mocy muszą bazować na obliczeniach czasów dla poszczególnych trybów i poborów prądu dla poszczególnych okresów. Muszą także uwzględniać okresy przejściowe związane z usypianiem działania i wybudzaniem. Pomijanie okresów przejściowych jest częstym błędem podczas szacowania poboru mocy, stąd tym razem zagadnieniu temu poświęcone zostanie nieco więcej miejsca.

Założenie, że mikrokontroler pobiera bardzo mały prąd w stanie bezczynności i dość duży podczas normalnej pracy może prowadzić do wniosku, że wykres poboru prądu w funkcji czasu wygląda jak na rysunku 4. Tymczasem w rzeczywistości prąd jest pobierany tak, jak pokazuje to rysunek 5. Te dodatkowe zużycie wiąże się z energią niezbędną do wybudzenia procesora ze stanu uśpienia (wake-up energy), a więc na uruchomienie stabilizatora LDO, oscylatora dostarczającego sygnał zegarowy, wyzerowanie rejestrów i szereg innych procesów wewnętrznych, które trwają do momentu, gdy CPU rozpocznie realizację pierwszej instrukcji kodu. Stąd programowanie czasów uśpienia, wybór trybu ograniczonego poboru mocy w jakim wówczas będzie znajdował się procesor i jak często i na jak długo będzie wybudzany, ma duże znaczenie dla sumarycznego poboru mocy i rzadko jest przez projektantów dobrze rozumiany.

Im częściej mikrokontroler jest wybudzany, tym ta energia bardziej wpływa na bilans energetyczny, zatem logiczne byłoby jak najrzadziej korzystać z aktywności. Rzadko jest to możliwe, dlatego w aplikacjach, które muszą często komunikować się z otoczeniem głębokie usypianie CPU (standby) może być niewskazane i lepszy jest tryb stop.

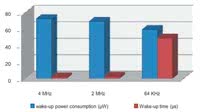

Szybkie wychodzenie ze stanu uśpienia zależy od dostępności zegara z krótkim czasem rozruchu. Na rysunku 6 pokazano zestawienie mocy zużywanej na wybudzenie CPU w zależności od szybkości taktowania. Wynika z tego, że gdy aplikacja korzysta z częstego wybudzania, wówczas szybki zegar nie zawsze zapewnia niskie zużycie energii. Lepiej więc wówczas na czas wybudzenia wykorzystać zegar wolniejszy, a dopiero potem przełączyć się na pełną szybkość. Analizy pokazują, że gdy MCU jest wybudzany często (współczynnik wypełnienia Run/standby przekracza kilka procent), korzystanie z trybów głębokiego uśpienia jest nieefektywne energetycznie.

Układy peryferyjne i obwody poza CPU

Poza zapewnieniem efektywnej pracy samego procesora warto zwrócić uwagę także na otoczenie. W czasie uśpienia warto wyłączyć pamięć nieulotną, wewnętrzny stabilizator napięcia wprowadzić w tryb niskiego poboru mocy (LP). To samo dotyczy wszystkich nieużywanych układów peryferyjnych. Ich uruchomienie wiąże się z oczekiwaniem na gotowość i jest źródłem strat mocy, stąd należy zawsze pamiętać, że przy częstym wybudzaniu potencjalne korzyści z wyłączenia obwodów muszą zostać sprawdzone za pomocą pomiarów.

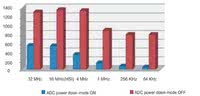

W przypadku przetworników A/C warto skorzystać z opcji automatycznego wyłączania i wyłączania, zwłaszcza gdy MCU pracuje z niską częstotliwością zegara. Bo wówczas czas wykonania pojedynczego rozkazu może być dłuższy od czasu konwersji i programowe sterowanie działaniem staje się nieefektywne. Na rysunku 7 pokazano prąd pobierany podczas konwersji danych dla różnych zegarów i wersji z automatycznym wyłączaniem. Jak widać praktycznie zawsze zapewnia to oszczędności.

Robert Magdziak