Dlaczego technologia PoP?

Rys. 1. Pierwsza generacja obudów układów 3D - struktury półprzewodnikowe (po lewej: położone bezpośrednio na sobie, po prawej: połączone dodatkowo pośredniczącymi strukturami krzemowymi)

Najbardziej krytycznym elementem w celu utrzymania wzrostu szybkości urządzeń elektronicznych jest połączenie procesora i pamięci. Im dłuższe połączenia, tym czas cyklu odczyt-zapis tej pary elementów rośnie, co oznacza, że znacznie dłużej trwa przesłanie danych do procesora niż czas potrzebny do ich użycia.

Istnieje zatem zapotrzebowanie na rozwiązania, które adresowane są dla "wąskiego gardła" transmisyjnego, jakim jest takie połączenie szybkich elementów przetwarzających dane, aby zagwarantować możliwość realizacji dużej liczby sygnałów o wysokiej przepustowości przy niskim poborze energii i emisji zaburzeń elektromagnetycznych.

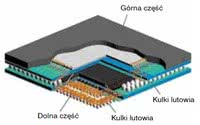

Technologia PoP polega na "piętrowym" montażu jednego lub kilku układów pamięciowych w obudowach BGA (Ball Grid Array) na położonym niżej układzie procesora także wykonanym jako BGA (rys. 2). Produkowane dzisiaj układy mikroprocesorów i wydajnych mikrokontrolerów mają często ponad 500 wyprowadzeń, rozłożonych w rastrach rzędu 0,4-0,5 mm i przy średnicy kulek lutowia rzędu 0,3-0,35 mm.

Tak zwiększona gęstość upakowania poprawia szybkość działania tych układów, odporność na zaburzenia elektromagnetyczne, pozwala również na wcześniejsze i osobne przetestowanie każdego z elementów struktury PoP. Jest to szczególnie ważne dla układów logicznych, ponieważ potrzebują one często dużo bardziej skomplikowanej metodologii ich testowania.

Zalety stosowania układów montowanych w technologii PoP są następujące:

- zwiększona szybkość działania układów przy zmniejszonym zapotrzebowaniu na energię,

- możliwość stosowania pamięci od różnych dostawców,

- możliwość wstępnego testowania oddzielnie układu procesora i pamięci,

- możliwość stosowania pamięci o różnych parametrach (prędkość, pojemność, organizacja),

- niska temperatura połączenia (co najmniej taka jak w połączeniach wielostrukturowych półprzewodników).

Defekty w montażu układów PoP

W konwencjonalnej obudowie podzespołu elektronicznego (SO, QFP, PLCC) wyprowadzenia elementu są na zewnątrz układu, a tym samym defekty montażu można w łatwy sposób wykryć, stosując jedynie kontrolę optyczną. Inaczej jest w przypadku elementów BGA oraz układów PoP, gdzie wyprowadzenia (kulki) są pod układami. Do kontroli połączeń wykorzystuje się wtedy inspekcję rentgenowską oraz zgłady metalograficzne.

Poniżej przedstawiono listę typowych defektów montażu układów typu PoP, które muszą być wykrywane podczas produkcji:

Poniżej przedstawiono listę typowych defektów montażu układów typu PoP, które muszą być wykrywane podczas produkcji:

- Mostki - czyli zwarcia pomiędzy sąsiednimi kulkami układu. Zazwyczaj występują w narożach układów. Najczęstsze przyczyny to zbyt duża ilość nałożonej pasty, źle zaprojektowany szablon lub migracja lutowia spowodowana uszkodzeniem soldermaski na płytce.

- Zimne luty - powstają najczęściej na skutek niejednorodnej zwilżalności lutowia.

- Brak kulek lub ich zniekształcenia powierzchniowe - jest to zwykle skutek błędu producenta/dostawcy lub efekt migracji lutowia spowodowany uszkodzeniem soldermaski na płytce.

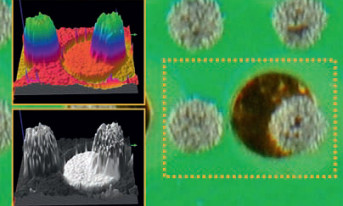

- Defekt "głowa na poduszce" (head in pillow) - powstaje, gdy użyte lutowie niewystarczająco zwilża powierzchnię pola lutowniczego na płytce drukowanej lub nie jest w stanie odpowiednio zwilżyć kulek układu. Zazwyczaj główną przyczyną jest tutaj różny stan pokryć lutowniczych, a w szczególności ich utlenienie. Takie połączenie zapewnia wystarczający kontakt elektryczny, ale niestety nie ma pożądanej wytrzymałości mechanicznej. Ze względu na brak wystarczającej siły połączenia pomiędzy kulkami a płytką drukowaną elementy PoP mogą przestać działać już przy niewielkim narażeniu mechanicznym i termicznym.

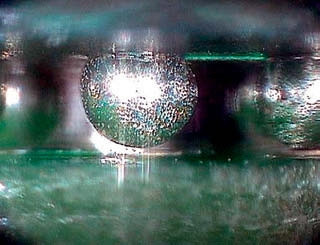

- Pustki (voids) - defekty te polegają na utknięciu w obszarze przetapianych kulek lotnej frakcji topników występujących w strefie lutowania. Efekt ten może prowadzić do istotnego obniżenia wytrzymałości mechanicznej połączeń. Dopuszczalna objętość pustek w obszarze kulki, w zależności od określonej klasy według normy IPC, zawiera się w przedziale 4-25%.

- Wewnętrzna delaminacja układu (popcorning) - przyczyną delaminacji układu jest zgromadzona wilgoć w materiale obudowy, która w procesie lutowania zaczyna nagle odparowywać. W efekcie powstają pęknięcia płytki, obudowy układu, jego rozhermetyzowanie i w końcu zniszczenie. Narzuca to istotne wymagania na odpowiednie pakowanie i przechowywanie elementów oraz ich wstępne wygrzewanie.

- Dodatkowe kulki lutu - pojawiają się najczęściej na skutek niepoprawnego procesu nadruku pasty przez szablon lub niewłaściwych parametrów zanurzania wyprowadzeń w paście lutowniczej.

Defekt odkształcenia

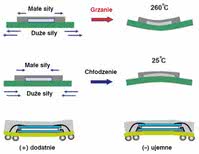

Szczególne miejsce wśród błędów w montażu zajmuje defekt odkształcenia (warpage), który jest zjawiskiem ściśle związanym z lutowaniem modułów PoP, a nie problemem wspólnym dla technologii SMT. Przyczynia się on do zdeformowania pakietu PoP, co może prowadzić do braku w połączeniach lutowniczych dla poszczególnych wyprowadzeń elementu. Efekt ten jest silniejszy w przypadku połączeń procesor- pamięć niż dla połączeń procesor- płytka PCB. Spowodowany jest różnymi współczynnikami rozszerzalności cieplnej (CTE) struktury półprzewodnikowej i płytki drukowanej (laminatu) układu lub PCB.

W procesie lutowania, podczas ogrzewania układu, na skutek różnicy we współczynnikach CTE struktury półprzewodnikowej i laminatu, podłoże układu (rys. 3) zazwyczaj odkształca się krawędziami do góry (dodatnie odkształcenie). Przy ochładzaniu elementu jest odwrotnie - krawędziami do dołu (ujemne odkształcenie). Kierunek odkształcenia i jego wartość ściśle zależą od wielkości struktury oraz wzajemnej różnicy współczynników CTE materiałów tworzących układ. Przy już niewielkim odkształceniu elementu może dojść do sytuacji, w której jedna lub część kulek nie utworzą połączenia z płytką PCB. To uniemożliwia poprawne funkcjonowanie układu, a tym samym działanie całego urządzenia.

Unikanie błędów

Odpowiedni projekt płytki, w tym przede wszystkim pól lutowniczych oraz szablonu, minimalizuje ryzyko powstania błędów otwartych połączeń (open solder joint), poprzez dostarczenie odpowiedniej ilości pasty lutowniczej na pady płytki PCB lub dolnego układu (procesora) w strukturze PoP. Jednakże, w większości przypadków do połączenia procesor-pamięć, zamiast pasty używany jest topnik, który nie pozwala na wypełnienie ewentualnych przerw w połączeniach w wyniku efektu odkształcenia. Minimalizacja odkształceń musi być więc kompromisem pomiędzy stosowanymi materiałami na elementy PoP kontrolą temperatury i czasu w procesie lutowania elementów.

Odkształcenie układu PoP ma decydujące znaczenie dla jakości montażu. W procesie jednoetapowego montażu (in line), gdzie zarówno górny, jak i dolny układ BGA jest montowany na płytce w tym samym cyklu, odkształcenie dla obu układów powinno być na jednakowym poziomie i w tę samą stronę (dodatnie lub ujemne). W procesie dwuetapowym (pre-stacking), odkształcenia poszczególnych obudów są krytyczne w czasie ich oddzielnego lutowania w specjalnym uchwycie, natomiast zachowanie modułu PoP jest ważne dopiero podczas montażu modułu do płytki PCB.

Rozwiązania specjalizowane

Na rynku pojawiły się już układy, które dzięki swojej budowie zmniejszają efekt odkształcenia. W ten sposób powstał układ TMV PoP - Thru Mold Via Package on Package stworzony przez firmę Amkor Technology (rys. 4).

Strukturę półprzewodnikową typu flip-chip całkowicie zalano na obszarze całego układu, pozostawiając w obudowie jedynie otwory częściowo wypełnione spoiwem w celu lepszego połączenia ich z układem pamięci. Wyeliminowano w ten sposób również zależność rastra wyprowadzeń od odległości pomiędzy układami w stosie i zapewniono możliwość montowania pamięci o dużej skali upakowania, nawet CSP (Chip Scale Package).

Poprawiona budowa układu pozwala na zwiększenie o około 30% wymiarów struktury półprzewodnikowej, przy tej samej wielkości obudowy, w porównaniu do poprzedniej generacji układów PoP. Dzięki temu możliwe jest stosowanie bardziej zawansowanych układów typu flip-chip, co bezpośrednio wpływa na wzrost wydajności modułów. Układy TMV PoP pozwalają na umieszczanie wewnątrz obudowy wielopoziomowych struktur, z wykorzystaniem technologii TSV i mikropołączeń drutowych (wire bonding) oraz wbudowanych elementów biernych (passive integration).

Przeprowadzone przez firmę Amkor testy odkształcenia modułów: TMV PoP - pamięć oraz PoP - pamięć, potwierdziły doskonałą zgodność układów TMV PoP z układami pamięci. W trakcie procesu ogrzewania zmierzone maksymalne odkształcenie wyniosło 28,8 μm, przy odkształceniu 179,8 μm dla układów PoP starszej generacji (z odkrytą strukturą), a w trakcie ochładzania, 11 μm dla modułu z TMV PoP, przy 170 μm dla układów PoP starszej generacji. To wszystko powoduje, że technologia TMV PoP jest ciekawą alternatywą dla powszechnie stosowanych układów z odkrytą strukturą.

Dotychczas technologia PoP zarezerwowana była dla dużych firm produkujących zaawansowane urządzenia elektroniczne. Związane jest to przede wszystkim z wysokimi kosztami wprowadzenia nowej technologii na rynek, zaawansowaną technologią produkcji oraz posiadaniem nowoczesnego parku maszynowego.

Firma Semicon we współpracy z Instytutem Tele- i Radiotechnicznym (ITR) w Warszawie w ramach Programu Operacyjnego Innowacyjna Gospodarka - działanie 4.1, pt. "Innowacyjne technologie zaawansowanego montażu powierzchniowego (SMT) płytek drukowanych" dofinansowanego ze środków UE prowadzi prace nad omawianą technologią PoP. Zainteresowanych prosimy o kontakt. Dysponujemy unikalną w Polsce linią montażową wyposażoną między innymi we flukser do układów PoP, pomiar siły nacisku ssawki, zmieniacz do 20 tacek, specjalny dyspenser pasty/kleju - IPAG oraz możliwość montażu i zadruku ciężkich do 10 kg i długich do 800 mm płytek PCB.

Piotr Ciszewski

Semicon

www.semicon.com.pl