Wersje sprzętowe algorytmów mogą być zrealizowane w ogólności na trzy sposoby. Po pierwsze do kodowania lub dekodowania może być wykorzystywany główny procesor urządzenia. Rozwiązanie to wymaga bardzo wydajnej centralnej jednostki obliczeniowej i zazwyczaj jest nieosiągalne w niewielkich urządzeniach przenośnych. Drugą możliwością jest wykorzystanie dodatkowego procesora sygnałowego, który może służyć jako pewnego rodzaju koprocesor dla tych danych, które wymagają przetwarzania strumieniowego. Takie podejście do tematu pozwala wygodnie dysponować zużyciem mocy i wybudzać układ DSP ze stanu uśpienia tylko na czas przetwarzania sygnału wideo. Dodatkowy procesor sygnałowy zabezpiecza też system operacyjny urządzenia przed „zawieszeniem” związanym ze zbytnim przeciążeniem obliczeniowym CPU.

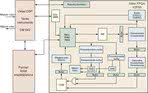

Rys. 1. Schemat blokowy fragmentu urządzenia wykorzystującego procesor sygnałowy i układ FPGA do obsługi kompresji H.264

Układ FPGA może zostać także zastosowany jako koprocesor dla procesora sygnałowego, który to w danym urządzeniu służy nie tylko przetwarzaniu sygnałów wideo H.264, ale także i innych strumieni danych. Duża elastyczność konfiguracji FPGA pozwala na zaimplementowanie tylko wybranych fragmentów algorytmu AVC, a nawet zwielokrotnienie niektórych bloków w celu przyspieszenia przetwarzania danych. Koncepcja ta została zilustrowana na rys. 1. Oczywiście, rozwiązanie to nie musi być optymalne pod względem kosztu, rozmiarów PCB, a czasami nawet wydajności. Wszystko zależy od tego, jakie są priorytety i ograniczenia, do których muszą się dostosować projektanci urządzenia.

Co w FPGA?

Fot. 1. Płytka deweloperska firmy Xilinx polecana również jako narzędzie do rozwoju projektów urządzeń multimedialnych wykorzystujących algorytm H.264

Na algorytmy kodowania i dekodowania H.264 składa się wiele nowych metod przetwarzania danych i zabiegów, które mają na celu polepszenie jakości obrazu lub zmniejszenie wielkości plików wynikowych. Metody te mogą być w bardzo wydajny sposób implementowane właśnie wewnątrz FPGA. Przykładem może być kompensacja ruchu typu „Quarter Pixel”, która polega na tym, że wykrywane są przemieszczenia o jedną czwartą piksela, zamiast o połowę piksela, tak jak to było we wcześniej stosowanych algorytmach. Tego typu interpolacja wymaga większej ilości obliczeń i warto ją zapisać w postaci odpowiedniego bloku FPGA. Innym zabiegiem charakterystycznym dla AVC jest przeszukiwanie obrazu w celu znalezienia przemieszczających się bloków różnej wielkości. O ile w klasycznych algorytmach kompresji wykorzystywano jedynie bloki o wymiarach 16 na 16 pikseli, to nowy algorytm pozwala na kompresje z uwzględnieniem bloków prostokątnych o bokach 16, 8 i 4 piksele. Wprowadzenie wyszukiwania bloków różnej wielkości jako odrębnych grup komórek FPGA umożliwia znaczne zrównoleglenie obliczeń, a więc i ich przyspieszenie.

Opisane powyżej elementy algorytmu AVC to tylko niektóre z wielu, jakie mogą być z powodzeniem zaimplementowane w układach programowalnych. Na potwierdzenie tej teorii wystarczy podać przykłady prawdziwych realizacji H.264, jakie pojawiły się niebawem po ustanowieniu nowego standardu. Pierwszym z nich było zaprezentowane w kwietniu 2005 roku urządzenie wykorzystujące do kompresji AVC układ Stratix II firmy Altera. Pięć miesięcy później firma Xilinx przedstawiła własną implementację kodera H.264 w postaci FPGA. Tym razem stworzono kod w języku VHDL i Verilog, który mógł być wgrany do układów z rodziny Virtex lub Spartan. Rozwiązanie to przewyższało projekt Altery, gdyż była to pierwsza implementacja algorytmu AVC w całości, a nie tylko w części wykonana w postaci programu układu FPGA.