Technika 3D

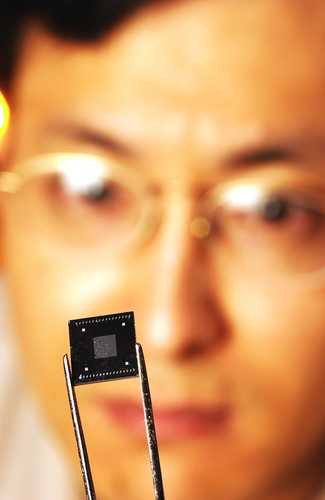

Wielu producentów zajęło się poszukiwaniem metod gęstszego montażu trójwymiarowego. Nad technologiami trójwymiarowego montażu pracują takie firmy jak Amkor, IBM, IMEC, Intel, Quimonda, Samsung, Texas Instruments, Ziptronix i inne. Przewiduje się, że w kolejnych latach nastąpi koegzystencja różnych technik montażu 2D i 3D, w zależności od wymaganej gęstości upakowania. Początkowo montaż 3D zostanie zastosowany do pakowania pamięci, a następnie dojdą scalone układy logiczne i wreszcie układy sterujące w formie układów scalonych ASIC, czy SoC.

Procesy spiętrzania struktur półprzewodnikowych wykorzystujące połączenia wewnętrzne między strukturami (TSV) będą prawdopodobnie w pełni stosowane początkowo w produkcji pamięci. W Samsung Electronics wykonano już piętrowy pakiet pamięci DRAM, z zastosowaniem technologii TSV. W celu uniknięcia spowodowanego przez warstwę redystrybucyjną pogorszenia parametrów został on zamknięty w aluminiowych wkładkach. Pakiet powstały w procesie tworzenia płytki składa się z czterech 512-megabitowych chipów DRAM DDR2, tworzących 2Gb pamięci o dużej gęstości. Chipy DRAM zostały połączone metodą TSV, tworząc 4-gigabajtową kość pamięci DIMM.

Technika TSV polega na wycinaniu laserem mikrometrowych pionowych otworów w krzemie, które łączą obwody pamięciowe miedzianym wypełnieniem. Dodatkowa zmniejszana jest grubości płytki półprzewodnika, co pozwala unikać odkształcania struktury w niskoprofilowej obudowie.

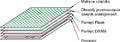

Nie tylko mikroelektronika przechodzi w trzeci wymiar. Również technologia płytek drukowanych zaczyna być trójwymiarowa. Urządzenie Miptek firmy Panasonic umożliwia tworzenie płytek drukowanych 3D na wtryskowo formowanym podłożu z użyciem precyzyjnego modelowania laserowego. Pozwala to tworzyć dowolne urządzenia, wymagające elastyczności i miniaturyzacji przy kształtowaniu właściwości optycznych, elektrycznych i termicznych.

Wszelkiego rodzaju pakietowanie struktur w stosy trójwymiarowe wymaga odpowiedniej techniki wzajemnego łączenia. Przykładowo technologia DBI (Direct-Bond-Interconnect)firmy Ziptronix pozwala na łączenie struktur ze sobą i całych pakietów do PCB i umożliwia stosowanie połączeń o szerokości 2μm z dokładnością 1μm przy rastrze węższym od 10μm.

Eliminacja wire-bonding?

Mimo, że liczni eksperci pakietowania chipów uważają, że spiętrzanie metodą TSV może wyeliminować wire-bonding, warto pamiętać, że nie zapewnia ono połączeń najkrótszych. Wymaga wyprowadzeń, mieszczących się na brzegach struktur półprzewodnikowych. Ogranicza więc liczbę połączeń do długości brzegów, podzielonej przez raster maszyny łączącej. Podobnie jest w przypadku połączeń drutowych. Pomiędzy łączonymi drucikiem spiętrzanymi układami konieczne są odstępy, a druciki również zajmują miejsce. Dlatego przez cały czas wire-bonding jest ważnym narzędziem technologicznym i wiodące firmy półprzewodnikowe nadal rozwijają tę szeroko stosowaną technikę, która w praktyce jest tańsza niż TSV. Obecnie Samsung za pomocą połączeń drutowych pakuje 16 struktur NAND w moduł MCP (Multichip Package), uzyskując pamięć o pojemności 16GB.

Chcąc pokonać ograniczenia wynikające z wypukłości powstających przy połączeniach drutowych firma Tessera zaprezentowała mikrokontaktowy CSP (Chip-Scale Package)o zredukowanym rastrze do układów matryc obszarowych o dużej gęstości upakowania. W pakiecie zastosowano niklowane i złocone wypukłości miedziane, umożliwiające montaż SMT tych CSP na płytce. Pola mikrokontaktowe do tych wypukłości mogły zostać zredukowane do średnicy tylko 0,2mm, podczas gdy przy montażu w BGA wynosi ona 0,3mm przy rozmieszczeniu co 0,5mm (rys. 2).

Osiągnięcia firm

W firmie Elpida Memory opracowano moduł MCP o największej w świecie gęstości upakowania. Połączono w nim 20 struktur spiętrzonych w pakiet o wysokości 1,4mm. Dla osiągnięcia wymaganej grubości poszczególne struktury zostały sprowadzone do grubości 30μm, a do operowania nimi opracowano specjalne wyposażenie. Struktury te są niskopętlowo łączone drucikiem 40μm. Opracowano także metodę mechanicznie bezpiecznego wstrzykiwania tworzywa w przestrzenie międzystrukturowe.

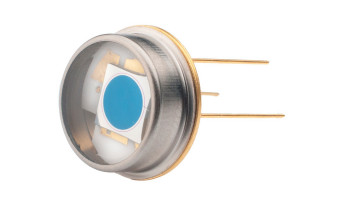

W miejsce połączeń drutowych coraz częściej wprowadza się technologię flip-chip. W tym przypadku struktura po odwróceniu jest montowana do podłoża lub do płytki drukowanej techniką BGA lub za pomocą innych wypukłych kontaktów. Eliminuje to nie tylko druciki łączące, ale także zwiększa szybkość działania i redukuje ograniczenia gabarytowe.

Firma Freescale Semiconductor pchnęła technologię flip-chip jeszcze o krok dalej (rys. 3). W jej rozwiązaniu górny układ w stosie może być pamięcią, procesorem, modułem Bluetooth, albo moduł aparatu fotograficznego. Według firmy taka metoda zapewnia najlepszą kombinację pożądanych atrybutów pakietu pozwalając stworzyć np. pełny układ GSM EDGE w jednym układzie.

Technologia spiętrzania struktur MicroPilr firmy Tessera pozwala na połączenia układ-układ do 0,1mm i układ-płytka do 0,3mm (rys. 4). Wysokość kolumn dochodzi do 0,18mm, a ich średnica może się zmniejszać od 0,375 nawet do 0,04mm. Dla porównania można przytoczyć średnicę kulek lutowia, mierzących zwykle od 0,35 do 0,5mm.

Nowe materiały

Producenci układów scalonych wiedzieli od dawna, że zmniejszanie rozmiarów struktur wywoła kłopoty z łączącymi je aluminiowymi i miedzianymi drucikami, które równocześnie zwiększają także opóźnienia. W układach trójwymiarowych o dużej gęstości montażu do wykonywania połączeń coraz częściej wykorzystywane jest złoto, pozwalające uzyskać korzystny kształt łuków, liniowość i stabilność. Przyszłościowym materiałem połączeń w układach trójwymiarowych mogą też stać się nanorurki węglowe. Przewodzą one większe prądy o gęstości nawet 107A/cm2. W Fujitsu opracowano takie połączenia dla układów 32nm (rys. 5).

Kierunki na przyszłość

Drogi ewolucji montażu 3D układów scalonych będą zależały od szeregu czynników. Od szybkości, z jaką producenci będą wprowadzali nowe metody montażu, od wyboru sposobów odprowadzania rosnącej ilości wydzielanego w układach ciepła, od rodzaju i kompatybilności wyposażenia produkcyjnego oraz narzędzi. Eksperci uważają, że może to przebiegać w kilku fazach. Najprawdopodobniej rozwój obejmie warstwowe montowanie płytek pamięci Flash z TSV i pastą przewodzącą ciepło. Rozwiązania te zostaną zapewne potem zastąpione łączeniem układów scalonych metodą powierzchnia-powierzchnia, z wypukłościami o rastrze 5μm. W końcu rozwinie się metoda SoS (System-On-Silicon), w ramach której pamięci, układy graficzne i inne układy scalone będą w sposób odwrócony łączone z chipem mikroprocesora.

Krzysztof Pochwalski