Układ ten jest następcą STGAP1S i został wyprodukowany przy użyciu opatentowanej technologii BCD6 firmy ST. Ma podwójne piny wejściowe, które pozwalają sterowanie dowolną polaryzacją sygnału cyfrowego i zapewnia sprzętową blokadę zapobiegającą przewodzeniu skrośnemu tranzystorów mostka w przypadku awarii. Wejścia sterownika są kompatybilne z poziomami logicznymi CMOS/TTL 3,3 V, co umożliwia łatwe połączenie z mikrokontrolerem. Wyrównane opóźnienia propagacji sygnałów pomiędzy sterownikiem dolnej sekcji układu mostka oraz górną (wysokonapięciową) zapewniają precyzję sterowania i umożliwiają działanie przy dużej częstotliwości kluczowania. Odporność na stany przejściowe w trybie wspólnym (CMTI) wynosi ±100 V/ns w całym zakresie temperatur od –40 do 125°C.

STGAP2HS jest dostępny w dwóch różnych wersjach. Jedna ma oddzielne piny wyjściowe, które umożliwiają niezależny dobór czasów włączania i wyłączania za pomocą oddzielnych rezystorów bramkowych. Drugi ma pojedynczy pin wyjściowy oraz wbudowany ogranicznik Millera, który zapobiega powstawaniu na bramce tranzystora niebezpiecznych przerzutów napięcia podczas szybkiej komutacji.

Efekt Millera odpowiedzialny jest za zakłócanie procesu przełączania tranzystora na skutek istnienia pasożytniczej pojemności bramka-dren CGC. Na skutek jej obecności szybki wzrost napięcia wyjściowego (na drenie) przenosi się na wejście (tj. bramkę), wywołując wzrost napięcia prowadzący do niekontrolowanego (fałszywego) załączenia tranzystora, a nawet prowadzący do przebicia warstwy izolacyjnej chroniącej bramkę MOSFET-a. Efekt Millera spowalnia też proces komutacji, gdyż ma charakter działania podobny w skutkach do układu ujemnego sprzężenia zwrotnego. Walka z nim wymusza minimalizację wartości impedancji w obwodzie bramki oraz stosowanie driverów zawierających potrójne obwody sterujące, a więc z oddzielną ścieżką włączania i wyłączania tranzystora (sink/ source). Rozwiązaniem problemu jest także dodanie do sterownika obwodu o nazwie Miller-Clamp realizującego dodatkowe chwilowe zwarcie bramki w odpowiednim momencie dla uniknięcia negatywnego wpływu pojemności pasożytniczych tranzystora.

Obie wersje sterownika współpracują z N-kanałowymi tranzystorami MOSFET zarówno z tymi dolnymi, a więc ze źródłem dołączonym do masy (low-side), jak i z górnymi, gdzie dren dołączony jest do plusa zasilania (high-side). Wprawdzie w przypadku dolnych tranzystorów mostka często nie ma potrzeby izolacji galwanicznej, niemniej ważne jest zachowanie symetrii i zgodności czasów propagacji sygnału, dlatego raczej unika się rozwiązań kombinowanych z górą izolowaną a dołem nie.

Oprócz ochrony przed przegrzaniem, STGAP2HS ma też zintegrowane zabezpieczenie UVLO działające zarówno w sekcji dolnej, jak i w kanale wysokonapięciowym. Zwiększa to niezawodność działania układu mocy, zapobiegając działaniu w warunkach przeciążenia lub sytuacjach potencjalnie niebezpiecznych. Opóźnienie propagacji sygnału między wejściem a wyjściem jest mniejsze niż 75 ns. Umożliwia to dokładne sterowanie modulacją szerokości impulsu (PWM), a dostępny tryb czuwania (standby) pomaga projektantom zmniejszyć zużycie energii przez cały system, gdy stopień mocy nie działa. Producent gwarantuje też niewielki procentowy rozrzut czasu propagacji, co oznacza, że nawet przy dużych szybkościach sygnału zegarowego PWM nie ma problemu z niekontrolowanym "wyjściem" poza czas martwy i tolerancje czasowe zapobiegające przepływowi prądu skrośnego przez tranzystory mocy, np. na skutek błędu w oprogramowaniu mikrokontrolera. Jest to poważny problem we wszystkich układach mostkowych. Zawierają one typowo 4 tranzystory mocy, z których dwa dołączone są źródłami do masy, tworząc dolną gałąź mostka, a pozostałe dwa mają dreny dołączone do dodatniej szyny zasilającej (górna część mostka). Zakłócenia w komutacji polegające na tym, że górny i dolny tranzystor w gałęzi zostaną załączone, prowadzą do katastroficznego uszkodzenia tych przełączników.

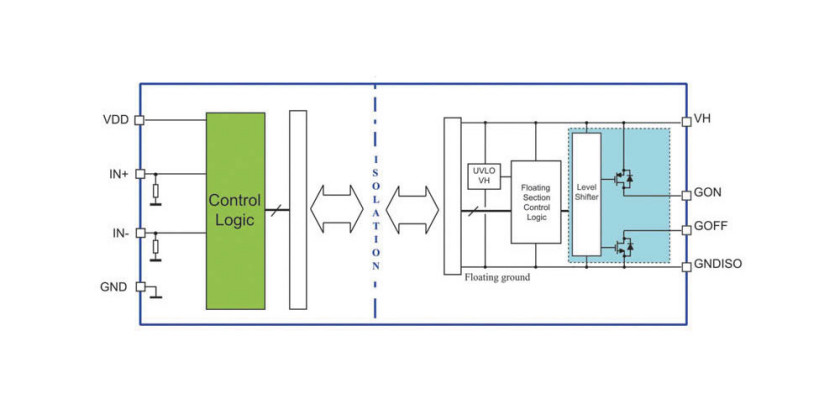

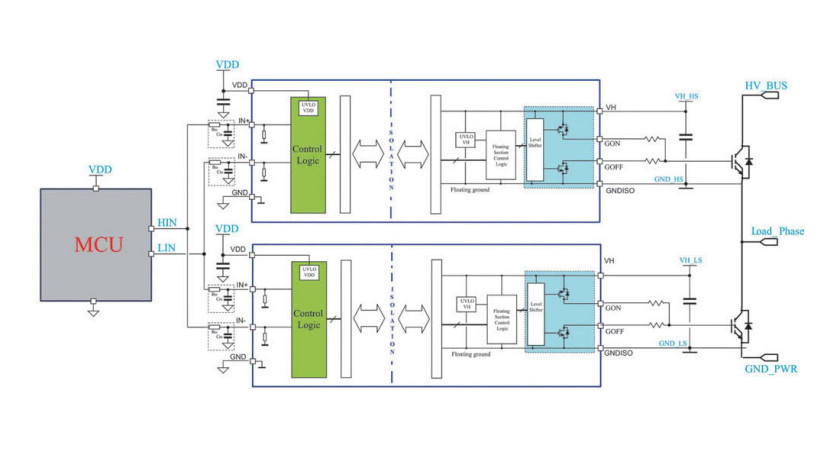

Na rysunku 1 pokazano schemat wewnętrzny układu STGAP2HS z zaznaczonymi jego głównymi blokami wewnętrznymi, a na rysunku 2 pokazano przykładową aplikację.

Charakterystyka układu STGAP2HS

|

ST Microelectronics

www.st.com