Sukces produktu jest uzależniony nie tylko od funkcjonalności i jakości wykonania, ale także coraz częściej od szybkości wprowadzenia na rynek i zaproponowania własnych rozwiązań, zanim zrobi to konkurencja. Nietrudno zauważyć, że o innowacyjności można mówić tylko do momentu, aż ktoś inny nie wykorzysta zbliżonego rozwiązania.

Niniejszy artykuł ma stanowić przegląd metod i strategii doboru elementów elektronicznych do własnych produktów, aby zapewnić ich nowoczesność i wysoką funkcjonalność w sposób możliwie szybki oraz bezproblemowy. Należy zauważyć, że zawsze podstawę dla sprawnej pracy stanowi odpowiednio wykwalifikowany zespół projektantów, jednakże często wybór konkretnych rozwiązań lub podzespołów pochodzących od konkretnego producenta może zdecydować o szybszym bądź późniejszym zakończeniu projektu.

Rozeznanie rynkowe

Rys. 1. Prezentacja przygotowana przez firmę Atmel dla tego zestawu ewaluacyjnego EVK1105 na YouTube

Rosnące wymagania konsumentów sprawiają, że producenci muszą oferować coraz większą funkcjonalność swoich wyrobów i poprawiać ich parametry. Spełnienie obu tych warunków staje się możliwe dzięki ciągłemu postępowi i poszerzaniu oferty podzespołów elektronicznych. Konkurencja na rynku półprzewodników sprawia, że do oferty wprowadzane są coraz nowsze generacje układów realizujących coraz bardziej złożone zadania.

Z tego względu znajomość oferty rynkowej, przynajmniej w ogólnym stopniu, jest niezbędna dla utrzymania konkurencyjności własnych produktów. Bieżące śledzenie oferty handlowej producentów półprzewodników pozwoli uniknąć stosowania przestarzałych rozwiązań i często uprościć budowę samego urządzenia. Pozwoli to dostrzec nowe możliwości i wykorzystać je w swoich produktach. Jest to także wiedza przydatna podczas prowadzenia rozmów z klientami, którzy chcą wiedzieć, jakie technologie można wykorzystać do realizacji zleconego projektu.

Niezbędna bywa także ogólna znajomość najpopularniejszych rozwiązań wykorzystywanych przez producentów (protokołów, interfejsów, standardów), gdyż daje to możliwość dokładniejszego oszacowania czasu potrzebnego na ich zaimplementowanie we własnym produkcie. O wyborze konkretnego rozwiązania nie zawsze musi decydować cena, dostępność oraz funkcjonalność, gdyż czasami warto uwzględniać również prostotę i szybkość implementacji konkretnych rozwiązań, a także dostęp do wsparcia świadczonego przez producenta i dystrybutora.

Na wsparcie takie, oprócz kontaktu z wykwalifikowanymi inżynierami, składa się ponadto dostęp do czytelnej dokumentacji oraz udostępniane oprogramowanie: przykładowe kody źródłowe, biblioteki, narzędzia konfiguracyjne. Podstawowym źródłem informacji o nowościach są strony producentów, jednakże przeglądanie wszystkich witryn internetowych może być czasochłonne i nużące. Dobrą alternatywę stanowią pisma branżowe oraz newslettery, w których zamieszczone są wyselekcjonowane informacje, często w skróconej formie.

Pozwalają one śledzić w sposób bieżący ofertę rynkową i zwrócić szczególną uwagę tylko na najbardziej interesujące podzespoły. Warto wspomnieć, że na popularnym serwisie YouTube dostępne są filmy promujące nowe układy wprowadzane na rynek. Przykładowo, wpisując w wyszukiwarkę EVK1105, można obejrzeć prezentację przygotowaną przez firmę Atmel dla tego zestawu ewaluacyjnego (rys. 1).

Pozwala ona zapoznać się z jego podstawowymi właściwościami oraz zobaczyć w działaniu mikrokontroler z rdzeniem AVR32 - w tym przypadku podczas dekodowania strumienia MP3 oraz obsługi przycisków dotykowych. Podobnie można odnaleźć prezentację zestawu NGW100 i zobaczyć uruchomiony na nim system Linux, obsługiwany za pomocą standardowego terminalu.

Przykładami innych firm wykorzystujących serwis YouTube do promocji własnych produktów są:

- Xilinx (np. "Spartan-6 FPGA Industrial Ethernet Kit"),

- Microchip (np. "32-bit PIC Microcontrollers ESC Boston 2010"),

- Analog Devices (np. "ADXL001: Analog Devices' New MEMS Vibration and Shock Sensor").

Warto zapoznać się z udostępnianym w ten sposób materiałem, gdyż dzięki temu można lepiej ocenić, czy dane rozwiązanie będzie odpowiednie dla potrzeb projektowanego urządzenia.

Literatura i dane techniczne

Rys. 2. Aplikacja Core Generator umożliwia wygenerowanie najpopularniejszych modułów (bloków funkcyjnych)

Punktem wyjścia do implementacji nowinek technicznych we własnych produktach jest szeroko pojęta literatura. Podstawę stanowią dokumenty producenta dotyczące danego układu (datasheet). Zawierają one najczęściej charakterystykę elementu, którego dotyczą, jego parametry elektryczne oraz czasowe, opis zastosowanych protokołów komunikacyjnych, sposób działania poszczególnych modułów czy przeznaczenie rejestrów.

Szczególną uwagę warto zwrócić na schemat aplikacyjny, który przedstawia sposób połączenia z elementami zewnętrznymi. Postępowanie zgodne z sugestiami producenta i radami, jakie często znajdują się w tego typu dokumentach (w tym zalecanym sposobem projektowania obwodu drukowanego), znacząco zwiększa szansę na sprawne uruchomienie układu. Warto ponadto zwrócić uwagę na noty aplikacyjne poruszające kwestie związane z praktycznym wykorzystaniem wybranego elementu.

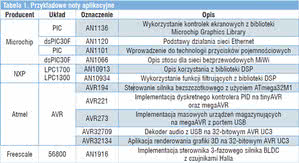

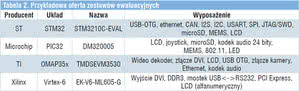

W dokumentach tego typu opisuje się najczęściej spotykane problemy i proponowane ich rozwiązania. Przykładowe noty aplikacyjne pochodzące od różnych producentów przedstawiono w tabeli 1. Warte uwagi są pisma branżowe przeznaczone dla konstruktorów sprzętu elektronicznego. Zawarte w nich projekty bazują również na nowych układach, co pozwala zapoznać się z ich typowymi aplikacjami, możliwościami, ograniczeniami i metodami konfiguracji czy programowania.

Stanowi to dobry punkt wyjścia do projektowania własnych rozwiązań. Szeroka znajomość podzespołów i ich typowych aplikacji umożliwia lepsze dobieranie podzespołów na potrzeby własnego projektu. Osobną kwestię stanowią standardy, czyli dokumenty opisujące dane rozwiązanie podające np. parametry elektryczne, prędkości transmisji, metody kodowania sygnałów, wymiary złączy, parametry czasowe, wbudowane rejestry czy stosowane komendy.

Część standardów jest dostępna w Internecie bezpłatnie, ale często trzeba za nie zapłacić. Wygodnym sposobem pozyskiwania standardów jest ich zakup przez Internet, co pozwala skorzystać z niego po uiszczeniu należności bez straty czasu na dostarczenie dokumentu przez pocztę lub kuriera.

Listing 1int main(void){

|

Zestawy ewaluacyjne

Rys. 3. Przykład aplikacji dla mikrokontrolerów AVR pozwalającej graficznie określić działanie funkcji takich jak: ochrona pamięci, źródło taktowania rdzenia, włączenie bądź wyłączenie interfejsów debugujących

Większość producentów opracowuje zestawy ewaluacyjne dla oferowanych przez siebie półprzewodników (mikrokontrolerów, czujników, układów programowalnych). Ponadto na rynku dostępne są rozwiązania pochodzące od niezależnych firm zapewniające odmienną funkcjonalność, niekiedy są one również tańsze od produktów "oryginalnych". Opracowując urządzenie bazujące na nowych rozwiązaniach, nieznanych jeszcze zespołowi konstruktorów, warto rozważyć zakup zestawu ewaluacyjnego.

Oprócz kluczowego elementu (mikrokontrolera, układu programowalnego, czujnika) na płytce znajdują się zazwyczaj dodatkowe komponenty umożliwiające zbadanie zachowania tego kluczowego podzespołu w podstawowych aplikacjach. Największą zaletą tego typu rozwiązań jest uniknięcie projektowania i wykonywania płytki drukowanej. Znacznie przyspiesza to moment, w którym zespół zapozna się z działaniem nowego układu lub modułu.

Za przygotowanie stabilnej platformy sprzętowej odpowiedzialny jest producent, co zwalnia zespół z konieczności czasochłonnego uruchamiania prototypu, wyszukiwania pomyłek i nanoszenia poprawek. Dopiero po nabraniu pierwszych doświadczeń i dokładnym określeniu, co jest niezbędne do prawidłowej pracy urządzenia, warto w sposób świadomy zaprojektować PCB. Nie bez znaczenia jest również przykładowe oprogramowanie, które często jest dołączane do zestawu.

Umożliwia ono zapoznanie się z funkcjami układu i pokazuje, w jaki sposób należy opracowywać własny kod, aby optymalnie wykorzystać dany układ. W ten sposób można szybko sprawdzić własne pomysły, modyfikując tylko program bez konieczności tworzenia go od zera. Zestawy ewaluacyjne mogą dostarczyć odpowiedzi na pytanie, czy wybrane rozwiązanie spełni pokładane w nim oczekiwania i czy pozwoli zrealizować urządzenia zgodne z wymogami.

Dobry przykład stanowią zestawy dla układów programowalnych współpracujące z zaawansowanymi układami peryferyjnymi (port DVI, kontroler SATA czy pamięć DDR2). Samodzielne zaprojektowanie obwodu drukowanego współpracującego z takimi komponentami nie jest sprawą prostą ze względu na wysokie częstotliwości przesyłanych sygnałów. Sprawia to, że ułożenie ścieżek i dobór elementów terminujących znacząco wpływa na poprawność działania układu.

Dysponując zestawem ewaluacyjnym, można skupić się na rozwoju oprogramowania, gdyż jest pewność, że warstwa sprzętowa funkcjonuje poprawnie. Znacznie łatwiej jest uruchomić urządzenie, dysponując poprawnie działającym, zweryfikowanym oprogramowaniem.

Ceny niektórych zestawów ewaluacyjnych, zwłaszcza zawierających zaawansowane podzespoły, nie należą do niskich. W sytuacji, gdy zakup takiego zestawu nie jest możliwy, warto poszukać na stronie producenta dokumentacji i zapoznać się z zastosowanymi rozwiązaniami sprzętowymi, aby wyeliminować możliwe dużo potencjalnych błędów z własnych rozwiązań. Schematy oraz oprogramowanie dostarczają cennych wskazówek, jak należy przygotować własne urządzenie, aby ograniczyć ryzyko niepowodzenia.

Materiały udostępniane dla zestawów ewaluacyjnych mogą obejmować inne rodzaje plików niż kod źródłowy. Dla układów programowalnych mogą to być pliki definiujące przypisanie wewnętrznych sygnałów logicznych do fizycznych wyprowadzeń. Są one szczególnie pomocne, gdy wykorzystywany moduł jest złożony i skomplikowany (np. kontroler DDR2). Pracując z danym zestawem ewaluacyjnym lub projektując własne urządzenie na jego podstawie, unika się potrzeby definiowania kilkudziesięciu wyprowadzeń w oparciu o dokumentację, ogranicza ryzyko błędu i w efekcie oszczędza sporo czasu.

Zestawy ewaluacyjne są wygodne zwłaszcza w sytuacji, gdy wybrane przez projektantów podzespoły są dostępne jedynie w obudowach BGA i podobnych. Montaż prototypu i wykonanie PCB jest w takiej sytuacji bardzo trudne. W związku z tym pierwsze testy i sprawdzenie możliwości wybranych komponentów wygodniej jest wykonać w oparciu o zestaw ewaluacyjny niż samodzielnie zaprojektowany sprzęt. W tabeli 2 przedstawiono kilka wybranych zestawów ewaluacyjnych.

Oprogramowanie

Producenci podzespołów elektronicznych są świadomi wyścigu z czasem, który jest udziałem ich klientów, dlatego udostępniają przykładowe oprogramowanie, biblioteki i aplikacje narzędziowe. Ma to na celu przyspieszenie pracy konstruktorów i tym samym uatrakcyjnienie oferowanych komponentów. Pierwszą grupę bibliotek dostarczanych przez producentów stanowią biblioteki obsługujące układy peryferyjne. Przykład może stanowić biblioteka STM32F10x_StdPeriph_Lib opracowana przez STMicroelectronics przeznaczona dla mikrokontrolerów z rodziny STM32.

Pozwala ona tworzyć oprogramowanie bez konieczności bezpośredniego operowania na rejestrach mikrokontrolera, co znacznie upraszcza pracę. Projektanci tracą mniej czasu na drobiazgowe analizowanie dokumentacji i określenia, które bity należy ustawić w poszczególnych rejestrach, aby zrealizować założony efekt. W konsekwencji takiego podejścia znacząco zwiększa się przejrzystość programu, co ułatwia nanoszenie ewentualnych zmian oraz przyspiesza wyszukiwanie błędów w kodzie.

Biorąc pod uwagę złożoność 32-bitowej architektury, podejście takie stanowi alternatywę wartą rozważenia. Ceną takiego uproszczenia pracy jest zwiększenie zajętości pamięci oraz mniejsza prędkość pracy mikrokontrolera na skutek wykonywania nadmiarowego kodu. Niemniej w układach wyposażonych w duże ilości pamięci oraz wymagających szybkiego napisania oprogramowania takie podejście staje się opłacalne.

Na listingu 1 pokazano przykładowy fragment programu dla układów STM32 napisany w oparciu o wspomnianą bibliotekę, odpowiedzialny za obsługę portu UART. Jego działanie powinno być zrozumiałe dla każdego, kto ma ogólne pojęcie o porcie szeregowym (np. na podstawie pracy z innymi rodzinami układów) oraz zna język angielski. Znajomość architektury rodziny STM32 nie jest w tym przypadku niezbędna. Warto zauważyć, że działanie programu nie będzie tak czytelne i oczywiste, gdy projektanci będą operowali bezpośrednio na rejestrach.

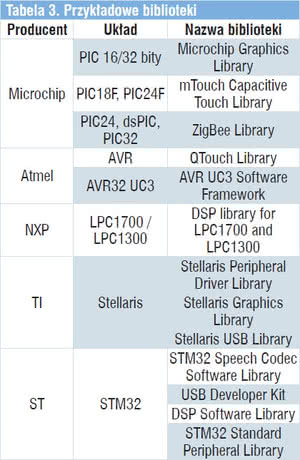

Drugim rodzajem bibliotek są biblioteki realizujące określone funkcje bądź zadania, kilka przykładów przedstawiono w tabeli 3. Można zauważyć, że oferta w tym względzie jest bardzo szeroka i wiele rzeczy daje się zrealizować, bazując na gotowych i sprawdzonych przez producentów bibliotekach. W ten sposób można uniknąć analizowania i opracowywania bardziej złożonych protokołów komunikacji (np. Ethernet czy USB) oraz algorytmów (filtracja cyfrowa, FFT) i skupić się na stronie funkcjonalnej urządzenia i testowaniu jego pracy.

Niekiedy nie istnieje uzasadniona potrzeba opracowywania własnych bibliotek, gdyż te dostarczone przez producenta są mocno zoptymalizowane i w pełni wykorzystują możliwości danego sprzętu, na jakim są uruchamiane. Dobrym przykładem jest złącze USB, którego obsługa nie należy do trywialnych, natomiast dzięki oprogramowaniu dostarczonemu przez producentów większości mikrokontrolerów taka się właśnie staje. Innym przykładem oprogramowania wymagającego tylko minimalnych zmian są bootloadery.

W przypadku kodu udostępnionego np. przez firmę Microchip wystarczy wybrać port I/O mikrokontrolera służący do aktywowania bootloadera po resecie, aby móc aktualizować oprogramowanie przez złącze USB. Dużym ułatwieniem są w tym przypadku gotowe aplikacje, odpowiedzialne za przesyłanie kodu wynikowego do pamięci Flash oraz wersje źródłowe ułatwiające opracowanie własnych programów. Warto wspomnieć również o dostarczaniu gotowych plików wykorzystywanych przez linker, dzięki czemu obecność bootloadera jest praktycznie niezauważalna.

Osobny rodzaj wsparcia ze strony producentów stanowią kreatory umożliwiające konfigurowanie wybranych układów peryferyjnych bądź generujące kod źródłowy. Ułatwiają one i przyspieszają przygotowanie wybranych układów do pracy. Najlepszym przykładem aplikacji tego typu jest Core Generator dołączony do pakietu ISE Design Suite firmy Xilinx przeznaczonego do projektowania logiki układów FPGA. Aplikacja Core Generator (rys. 2) umożliwia wygenerowanie najpopularniejszych modułów (bloków funkcyjnych) w oparciu o informacje wprowadzone do kreatora.

W ten sposób można przygotować dwuportową pamięć RAM, kontroler pamięci DDR2, dekoder 802.16e CTC, filtr cyfrowy, moduł analizy FFT. Powstały moduł jest opisany w wybranym języku opisu sprzętu (Verilog lub VHDL), zależnie od ustawionej opcji. W przypadku mikrokontrolerów aplikacje dostarczane przez producentów pozwalają graficznie określić działanie niektórych funkcji, takich jak: ochrona pamięci, źródło taktowania rdzenia, włączenie bądź wyłączenie interfejsów debugujących. Na rysunku 3 przedstawiono przykładową aplikację tego typu przeznaczoną dla mikrokontrolerów AVR.

Innym przykładem narzędzia ułatwiającego pracę konstruktorom jest program Digital Filter Design przeznaczony dla układów dsPIC produkowanych przez firmę Microchip. Umożliwia ono projektowanie, analizę i implementację filtrów cyfrowych za pomocą graficznego interfejsu użytkownika. Środowisko przeprowadza niezbędne obliczenia matematyczne i automatycznie generuje kod źródłowy oraz potrzebne współczynniki filtrów. Dodatkowo istnieje możliwość wyświetlenia charakterystyk zaprojektowanego filtru (m.in. amplitudy, fazy, opóźnienia grupowego, odpowiedzi impulsowej).

Narzędzia

Rys. 5. Przykładowa sesja debugowania mikrokontrolera z rodziny STM32 w środowisku Raisonance (Ride 7 + Rlink)

Duże ułatwienie podczas pisania oprogramowania stanowią narzędzia, zapewniające "wgląd" w funkcjonowanie zastosowanego układu (np. mikrokontrolera, FPGA, podzespołów analogowych), tzn. pozwalające na bieżąco monitorować stan, w jakim się on znajduje. Najbardziej podstawowym przyrządem jest oscyloskop, który umożliwia obserwację przebiegów napięcia w wybranych punktach urządzenia. Rozsądne minimum stanowi oscyloskop wyposażony w dwa kanały, jednakże warto zainwestować w sprzęt wyposażony w cztery kanały.

Za pomocą oscyloskopu można zweryfikować, czy przebiegi występujące w urządzeniu mają wymagane parametry (częstotliwość, amplituda) oraz dokonać wstępnej analizy przesyłanych sygnałów i określić, czy odpowiadają one oczekiwaniom. Przykładem może być obsługa kodeków AC97, które komunikują się poprzez interfejs szeregowy.

Wykorzystując oscyloskop czterokanałowy do obserwacji sygnału zegarowego, linii nadawczej, odbiorczej oraz sygnału synchronizacji, można określić m.in., czy kodek wytwarza sygnał zegarowy, czy przesyła dane synchronicznie do impulsów wystawianych na wejściu Sync lub na podstawie obserwacji zbocza sygnału zegarowego i linii danych odczytać zawartość niektórych rejestrów. Jest to pomocne podczas określania, czy nie powstały błędy sprzętowe, montażowe lub czy nie popełniono błędu w oprogramowaniu.

Bardziej złożone oscyloskopy mają zaawansowane funkcje wyzwalania (np. sygnałami I2C, SPI, CAN, HDTV), analizy jittera, mocy oraz standardów takich jak Ethernet, USB, HDMI, SATA, DVI czy PCI-Express. Oscyloskopy zawierają mocno ograniczoną liczbę kanałów i nie umożliwiają pełnej analizy układów wykorzystujących wiele linii sygnałowych, np. w dyskach twardych czy wyświetlaczach. W sytuacji, gdy są to układy cyfrowe, znacznie lepiej pod tym względem sprawdza się analizator stanów logicznych.

Może on mieć nawet parędziesiąt kanałów wejściowych, pozwalając tym samym obserwować stan magistral adresowych, danych, sterujących. Na tej podstawie łatwo jest określić, czy przesyłane sygnały są zgodne z oczekiwaniami. Analizator stanów logicznych bywa przydatny również podczas pracy z układami programowalnymi, gdyż zapewnia podgląd sygnałów przesyłanych pomiędzy układem programowalnym a układami zewnętrznymi.

Ponadto możliwe jest wyprowadzenie wewnętrznych sygnałów FPGA na fizyczne porty i ich obejrzenie. Na tej podstawie łatwiej wyszukać nieprawidłowości w funkcjonowaniu zaprojektowanej logiki i szybciej usunąć błędy. Takie podejście może okazać się pomocne choćby podczas projektowania modułu konwertującego standard RS232 na postać równoległą, która jest łatwiejsza do wykorzystania w układach programowalnych.

Doprowadzając wejścia i wyjścia takiego modułu do fizycznych wyprowadzeń układu FPGA, można za pomocą analizatora obejrzeć wszystkie te sygnały. Pozwoli to łatwo sprawdzić, czy odpowiedź układu na doprowadzony sygnał RS232 jest poprawna, tzn. czy bajt przesłany w postaci szeregowej jest zamieniany na postać równoległą. W sytuacji, gdy w układach FPGA wykorzystywane są automaty, można łatwo sprawdzić w jakim stanie się one obecnie znajdują.

Wystarczy wtedy wystawiać na wybrane porty I/O słowo wyjściowe niepowtarzalne dla każdego ze stanów, aby określić, jak pracuje zaprojektowany automat i gdzie się ewentualnie "zatrzaskuje". Można ponadto wykryć zabronione przejścia i szybciej ustalić, co je powoduje. Łączenie modułów w większe struktury bez uprzedniego sprawdzenia ich poprawności sprawi, że w razie błędu znacznie trudniej będzie określić, który z kilku modułów odpowiada za niepoprawną pracę całego układu.

Mając jednak pewność, że właściwie przetestowano niektóre komponenty, można z dużą dozą prawdopodobieństwa określić, że błąd znajduje się w jednym z nieprzetestowanych modułów. Zawęża to obszar poszukiwań i przyspiesza proces debugowania. Producenci układów programowalnych mają świadomość trudności związanych z projektowaniem logiki dla złożonych struktur FPGA i problemów, jakie stwarza wyszukiwanie błędów.

Pewnym rodzajem wsparcia są symulacje czasowe obrazujące przebiegi wybranych sygnałów w układzie programowalnym. Umożliwiają one stwierdzenie, czy kod napisany w języku HDL jest wolny od błędów logicznych. Oprócz symulacji możliwe jest uzyskanie wglądu w wewnętrzną strukturę FPGA i zapoznanie się z przesyłanymi w niej sygnałami oraz stanami poszczególnych komponentów (np. automatów). Możliwość taką daje np. ChipScope Pro opracowany przez Xilinksa.

Narzędzie to jest częścią środowiska projektowego ISE Design Suite (dostępne w 30-dniowej wersji ewaluacyjnej). Użytkowanie ChipScope jest proste i sprowadza się do wygenerowania dwóch modułów (ILA oraz ICON) za pomocą narzędzia Core Generator. Blok ILA (Integrated Logic Analyzer) jest konfigurowalnym elementem, dla którego można zdefiniować liczbę portów służących do monitorowania magistral i/lub pojedynczych linii.

Każdy z portów ma niezależnie konfigurowalną szerokość bitową. Po wygenerowaniu bloku ILA doprowadza się do niego sygnały, które mają zostać zaprezentowane na ekranie komputera. Dane na portach są pobierane w takt sygnału zegarowego doprowadzonego do wejścia wyzwalanie bloku ILA. Moduł ICON (Integrated Controller) odpowiada za wymianę danych pomiędzy komputerem oraz ILA, z tego względu do użytkowania narzędzia ChipScope niezbędny jest interfejs JTAG: Platform Cable USB I/II, Parallel Cable IV lub ByteTools Catapult EJ-1 Ethernet-to-JTAG Cable.

Narzędzie ChipScope jest zasadniczo analizatorem stanów logicznych umieszczanym wewnątrz struktury FPGA, więc sygnały oglądane na ekranie reprezentują rzeczywiste sygnały doprowadzone do modułu ILA. Po przeprowadzeniu syntezy projektu i konfiguracji układu programowalnego uruchomia się aplikację z pakietu ISE Design Suite. Pozwala ona określić warunki rozpoczęcia rejestracji (poziomy logiczne na wybranych liniach) oraz przeprowadzać pojedynczą lub ciągłą rejestrację.

Po zgromadzeniu całego rekordu danych na ekranie komputera rysowane są przebiegi czasowe lub wyświetlany jest listing, zależnie od wyboru użytkownika. Warto zauważyć, że zarówno pojedynczym sygnałom, jak i magistralom można nadawać dowolne nazwy, co znacząco podnosi czytelność prezentowanych wyników. Na rysunku 4 pokazano okno aplikacji podczas pracy. Warto dodać, że ChipScope Pro wspiera następujące rodziny układów: Virtex-6, Virtex-5, Virtex-4, Spartan-6 i Spartan 3.

Rekord danych jest umieszczany w pamięci Block RAM, stąd jego rozmiar (liczba zapamiętywanych słów wejściowych) jest zależny od dostępności pamięci, na co wpływ ma wybór konkretnego układu programowalnego, stopień wykorzystania pamięci przez zaimplementowaną logikę oraz liczba monitorowanych linii sygnałowych. Warto zauważyć, że również inni producenci oferują podobne narzędzia zapewniające "wgląd" w działanie FPGA: SignalTap II czy CLAM przeznaczone dla produktów firm, odpowiednio, Altera oraz Actel.

Debugowanie staje się jeszcze łatwiejsze w sytuacji, gdy urządzenie jest oparte na nowoczesnym mikrokontrolerze zawierającym wbudowany interfejs debugujący. Umożliwia on podglądania stanu zmiennych, rejestrów oraz śledzenie programu w trybie krokowym. Duże ułatwienie stanowią pułapki programowe, gdyż dzięki nim procesor pracuje w czasie rzeczywistym i udostępnia obsługę wszystkich układów peryferyjnych.

Dopiero po wystąpieniu ściśle określonego warunku wykonanie programu zostaje wstrzymane, a stan procesora jest przekazywany do komputera. W ten sposób łatwiej jest znaleźć błąd, zwłaszcza gdy jest on związany z układami peryferyjnymi, np. transmisją szeregową, gdyż możliwa jest praca w trybie rzeczywistym. Standardowy scenariusz korzystania z narzędzi debugujących obejmuje sprawdzanie danych odbieranych i wysyłanych do układów peryferyjnych i śledzenie wykonania programu.

Na tej podstawie można stwierdzić, czy oprogramowanie prawidłowo przetwarza informacje, czy poszczególne fragmenty kodu są wykonywane oraz gdzie program ulega zawieszeniu. Przykładem skutecznego wykorzystania debuggera może być problem z wyświetlaniem daty w jednym z projektów realizowanych przez autora. Sprawdzając kolejno przekazywanie wartości z zewnętrznego zegara RTC na wyświetlacz, można było ustalić, że nieprawidłowe dane pojawiają się już podczas zapisu na LCD, w argumencie funkcji wyświetlającej datę.

Kolejnym krokiem było sprawdzenie zawartości klasy odpowiedzialnej za pobieranie danych. W jej wnętrzu również znajdowała się nieprawidłowa wartość, więc sprawdzono wartość odczytywaną z magistrali I2C. Po stwierdzeniu, że tutaj również występują nieprawidłowości, ustalono, że błąd tkwi w odczycie z układu zegara.

Po weryfikacji poleceń przesyłanych przez magistralę stwierdzono, że winę za ten stan rzeczy ponosi pomyłka przy adresowaniu wewnętrznego rejestru układu RTC. Bez możliwości wglądu w działanie programu i dokładnego śledzenia jego wykonania znalezienie błędu byłoby znacznie bardziej czasochłonne. Przykładową sesję debugowania mikrokontrolera z rodziny STM32 w środowisku Raisonance (Ride 7 + Rlink) przedstawiono na rysunku 5.

Projektowanie na wyższym poziomie abstrakcji

Rys. 6. Efekt obsługi graficznego wyświetlacza - wyświetlono na nim fragment okładki magazynu "Elektronik"

Niekiedy rozwiązania, jakie mają zostać zastosowane w urządzeniu, są zbyt czasochłonne w implementacji lub zbyt złożone, aby mógł to zrobić dany zespół projektantów. W takiej sytuacji pozostaje wykorzystanie zintegrowanych modułów lub układów scalonych realizujących pożądaną funkcję: obsługę sieci Ethernet, Wi-Fi, GSM, GPRS, łącza USB czy dekodowanie strumienia MP3. Rozwiązania tego typu obsługują wybrany standard i udostępniają uproszczony interfejs od strony wejścia.

Przykładem może być sprzętowy dekoder strumienia MP3 - VS1011. Pobiera on cyfrowy strumień danych, dekoduje go i wystawia na wyjściu sygnał analogowy, dzięki czemu nie trzeba samodzielnie implementować dekodera, a projekt może zostać zakończony znacznie szybciej. Podobne ułatwienie w realizacji komunikacji z komputerem przez łącze USB można osiągnąć, stosując jeden z wielu scalonych konwerterów USB-RS232.

Komunikacja staje się wtedy znacznie prostsza i możliwa do zrealizowania nawet przez mniej doświadczony zespół. Warto zauważyć, że ubocznym efektem takiego działania jest uniknięcie problemów z pozyskaniem numeru VID i pisaniem sterowników. Konstruktorzy unikają zagłębiania się w szczegóły obsługi standardu USB i korzystają z przyjaznego interfejsu szeregowego bądź równoległego. Podobnie implementacja komunikacji sieciowej może być ułatwiona dzięki modułom Wi-Fi czy Ethernet, które od strony mikrokontrolera udostępniają standardowy port szeregowy.

Zwalnia to projektantów z konieczności implementowania warstwy fizycznej i pisania stosu TCP/IP. W tym przypadku oszczędność czasu także jest znacząca, a projekt może zostać doprowadzony do końca nawet przez mniej doświadczonych konstruktorów. Również komunikacja radiowa z wykorzystaniem Bluetooth czy ZigBee jest znacznie łatwiejsza do zrealizowania, gdy wykorzystywane są gotowe moduły odpowiedzialne za zestawienie połączenia i transmisję danych.

Wyświetlacze graficzneGraficzny, kolorowy wyświetlacz pozwala unowocześnić wygląd oferowanego produktu i nadać mu nowy, innowacyjny charakter. Na rynku dostępna jest szeroka oferta tych elementów - począwszy od zwykłych matryc TFT bez wbudowanego kontrolera po zintegrowane rozwiązania mające własny sterownik dodany przez producenta. Przykładowe wyświetlacze wyszczególniono w tabeli 4. Wybór konkretnego modelu jest uwarunkowany przede wszystkim ceną oraz wymaganym stopniem złożoności obsługi i dostępną mocą obliczeniową. Najłatwiejsze w obsłudze są wyświetlacze zawierające zintegrowany kontroler, a tym samym prosty interfejs komunikacyjny. Odpowiada on za odbieranie poleceń z mikrokontrolera lub układu programowalnego, pamiętanie stanu poszczególnych pikseli oraz odświeżanie obrazu. Dzięki temu obraz może być generowany również przez wolniejsze układy, gdyż obraz nie musi być odświeżany parędziesiąt razy na sekundę. Sterowanie sprowadza się w takiej sytuacji do wskazania adresu kolumny i wiersza, pod który ma być zapisana informacja o kolorze piksela. Mimo prostoty interfejsu wybrany do testów wyświetlacz zapewnia możliwość wyświetlenia 256 kolorów w rozdzielczości 320×240 pikseli. Otrzymywany obraz sprawia, że docelowe urządzenie będzie miało czytelniejszy interfejs użytkownika oraz atrakcyjniejszy wygląd. Na rysunku 6 zaprezentowany efekt obsługi graficznego wyświetlacza - wyświetlono na nim fragment okładki magazynu "Elektronik". Obsługa rezystancyjnego panelu dotykowego również nie należy do skomplikowanych. Można ją zrealizować w oparciu o scalone kontrolery lub wykorzystując porty mikrokontrolera współdzielone z przetwornikiem ADC. Problem ten został poruszony np. w nocie aplikacyjnej 4-Wire and 8-Wire Resistive Touch-Screen Controller (SLAA384 opublikowanej przez Texas Instruments). W ten sposób może powstać estetyczny i łatwy w obsłudze interfejs użytkownika bez nadmiernego skomplikowania projektu. |

Podsumowanie

Opracowanie urządzenia nowoczesnego, cechującego się dużą funkcjonalnością, innowacyjnością i wyróżniającego się na rynku nie jest sprawą tanią ani prostą. O sukcesie decyduje m.in. dobre rozeznanie w ofercie podzespołów, doświadczony zespół projektantów, czas na przeprowadzenie niezbędnych testów oraz dobór poszczególnych komponentów. W sytuacji, gdy koszt nie jest krytycznym czynnikiem, można stosować układy scalone lub moduły, które realizują samodzielnie zadaną funkcję.

Tym samym najtrudniejsze problemy zostają rozwiązane przez producentów tych elementów i umożliwiają szybsze wprowadzenie produktu na rynek. Warto również przed zakupem konkretnych podzespołów zapoznać się z udostępnionymi materiałami, aby wybrać rozwiązanie możliwie najłatwiejsze w implementacji i mające bogatą dokumentację. Warto zwrócić uwagę na prezentacje producentów, które pozwolą zapoznać się z możliwościami wybranych rozwiązań.

Korzystając z ogólnie dostępnych forów internetowych można sprawdzić opinie innych osób o danym układzie, ustalić, jaką cieszą się popularnością oraz czy ich praca jest stabilna i wolna od nieprawidłowości. Dobrym pomysłem jest zakup zestawów ewaluacyjnych przed zastosowaniem wybranych podzespołów, aby przeprowadzić wstępne testy i ocenić, czy wybrane rozwiązanie będzie adekwatne do potrzeb.

Jakub Borzdyński