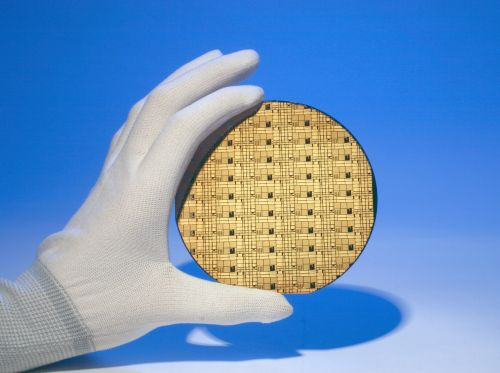

Większą gęstość upakowania elementów uzyskuje się poprzez zmniejszanie rozmiarów tranzystora. Jeszcze kilka lat temu powszechnie stosowano procesy technologiczne CMOS z tranzystorami o długości kanału 350nm. Obecnie do celów komercyjnych dostępne są procesy o długości kanału 65nm, a procesy o długości kanału 40nm są w fazie testów. Niebawem i ta granica zostanie przekroczona.Starsze procesy są jednak dalej używane wszędzie tam, gdzie liczy się koszt, a wymagana moc przetwarzania nie jest aż tak duża.

Zasadniczym problemem pozostaje redukcja mocy traconej w układzie scalonym. Całkowity pobór mocy układu scalonego CMOS może być przedstawiony jako suma dwóch głównych składników:

- statycznego poboru mocy, który jest spowodowany przez prądy upływu płynące w stanie ustalonym;

- dynamicznego pobór mocy, który występuje w momencie przełączania tranzystorów.

Pobór mocy układu scalonego może być rozpatrywany na prostym przykładzie inwertera CMOS.

Statyczny pobór mocy

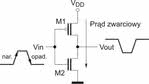

Rys.2. Inwerter CMOS zrealizowany w technice VTCMOS wraz z przykładowymi wartościami napięć sterujących

Obydwa typy tranzystorów używanych w układach logicznych (NMOS iPMOS) charakteryzują się skończonymi prądami upływu. Ponieważ w układzie scalonym występują nawet miliony tranzystorów statyczny pobór mocy nie może być zaniedbany, w szczególności ze względu na prądy podprogowe.

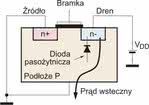

Rozważmy tranzystor NMOS pokazany na rys. 1. Pomiędzy podłożem (domieszkowany p), a drenem (domieszkowanym n+) powstaje zaporowo spolaryzowana pasożytnicza dioda. Powstanie diody jest w strukturze MOS nieuniknione, tak jak i nieunikniony jest również prąd upływu, który zwiększa się wraz ze wzrostem temperatury.

Drugim składnikiem statycznego poboru mocy jest prąd podprogowy, powstający na skutek dyfuzji nośników pomiędzy obszarami drenu i źródła w stanie słabej inwersji (ang. weak inversion) tranzystora. Prąd podprogowy odgrywa znaczącą rolę w momencie, gdy napięcie pomiędzy bramką a źródłem tranzystora jest nieznacznie mniejsze lub równe napięciu progowemu Vt. Ponieważ zmniejszając rozmiary tranzystora obniża się również napięcie progowe Vt,problem prądów podprogowych i związany z nimi poborem mocy coraz bardziej zyskuje na znaczeniu.

W celu minimalizacji prądów podprogowych często stosowana jest technika, która ma na celu zmianę wartości napięcia progowego tranzystora. Określana jest ona jako VTCMOS - ang. variable threshold CMOS. U podstaw tej metody leży odseparowanie źródła tranzystora od podłoża i podanie na nie innego napięcia niż to, które występuje na źródle. Technikę VTCMOS pokazano na rys. 2.

Podłoża tranzystorów PMOS i NMOS są odseparowane i sterowane napięciem z bloku kontroli napięcia podłoża. Jak wiadomo, napięcie progowe tranzystora Vtjest również funkcją napięcia pomiędzy źródłem a podłożem Vsb. W konwencjonalnej technice, podłoże tranzystora NMOS podłączane jest do masy, a podłoże tranzystora PMOS do napięcia zasilania. Dzięki temu napięcie Vsbdla obu tranzystorów jest zerowe. Warstwa zubożona w pobliżu drenu i źródła zapewnia, że z obszaru drenu i źródła do podłoża płyną jedynie prądy upływu.Przy pomocy techniki VTCMOS obszar zubożony jest powiększany, a w związku z tym prądy upływu zmniejszane. Podczas aktywnej pracy układu,wszystko działa tak, jak w technice konwencjonalnej. Podłoża tranzystorów NMOS podłączane są do masy, a podłoża tranzystorów PMOS do napięcia Vdd. Kiedy układ jestw stanie nieaktywnym, tj. np. uśpienia lub obniżonego poboru mocy -tak jak pokazano na rys. 2, napięcia podawane na podłoża tranzystorów ulegają zmianie. Na podłoże tranzystora NMOS podawane jest napięcie -Vdd, a na podłoże PMOS podawane jest 2*Vdd. Dzięki temu napięcie progowe tranzystora NMOS zwiększa się, a tranzystora PMOS zmniejsza do wartości osiąganych w starych technologiach o napięciu zasilania równym 5V. Niewątpliwą wadą tej metody jest konieczność wytworzenia napięć 2*Vdd oraz -Vdd w strukturze scalonej.

Dynamiczny pobór mocy

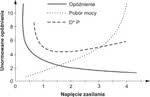

Rys.4. Unormowany czas propagacji i uśredniony dynamiczny pobór mocy inwertera CMOS w funkcji napięcia zasilania

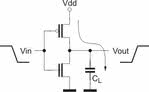

Zacznijmy od ładowania pojemności wyjściowej. Na rys. 3 pokazano inwerter CMOS obciążony pojemnością CL. W czasie ładowania pojemności wyjściowej napięcie na wyjściu inwertera zmienia wartość z zera do wartości napięcia zasilania Vdd, a część energii z zasilania tracona jest w tranzystorze PMOS w postaci ciepła. W czasie rozładowywania pojemności, energia z zasilania nie jest pobierana, a część zgromadzonej wcześniej w kondensatorze energii tracona jest wpostaci ciepła w tranzystorze NMOS. Ładowanie i rozładowywanie pojemności wyjściowej to źródło największych strat energii w układach CMOS. Straty mocy związane z przeładowywaniem pojemności wyjściowej można opisać wzorem:

P=CL*V2dd*Fclk*a

gdzie CL jest całkowitą pojemnością obciążającą, Vdd napięciem zasilania, Fclk częstotliwością pracy układu, a współczynnik „a”jest efektywną liczbą zmian wartości napięcia na węźle wyjściowym przypadającą na jeden takt zegara.

Analizując powyższe równanie można znaleźć sposoby na redukcję mocy dynamicznej. Jak widać, moc jest pobierana zawsze przy zmianie stanu wyjść. Można więc obniżyć częstotliwość pracy Fclk,ale jest to sprzeczne z wymaganą dużą mocą przetwarzania układu scalonego.

Redukcja napięcia zasilania

Zmniejszenie napięcia zasilania spowoduje zmniejszenie dynamicznego poboru mocy. Niestety, jeśli obniżymy tylko i wyłącznie napięcie zasilania, bez odpowiedniego przeskalowania długości kanału tranzystora, czy grubości dielektryka nastąpi wydłużenie czasu propagacji. Aby znaleźć kompromis między małą mocą, a akceptowalnym opóźnieniem przyjrzyjmy się iloczynowi poboru mocy i opóźnienia w zależności od napięcia zasilania pokazanemu na rys. 4. Im mniejszy iloczyn mocy i opóźnienia tym lepiej, gdyż równocześnie opóźnienie i pobór mocy są małe.

Dokładniejsza analiza opóźnienia wnoszonego przez inwerter, prowadzi do wniosku, że ujemne skutki zmniejszania napięcia zasilania, można zminimalizować poprzez odpowiednie zmniejszenie napięcia progowego. Niestety, ograniczenie napięcia progowego prowadzi do zmalenia marginesu szumów i skutkuje przewodzeniem w zakresie podprogowym, co może prowadzić do zwiększenia statycznego poboru mocy, który jak wspomniano, jest obecnie dużym problemem.

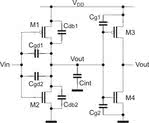

Pojemność obciążenia, czyli rozmiar tranzystora

Inną metodą zmniejszania dynamicznego poboru mocy związanego z przeładowywaniem pojemności obciążającej jest zmniejszenie tej pojemności. Im jest ona mniejsza tym korzystniej wpływa korzystnie nie tylko na pobór mocy podczas każdego przełączania, ale również na maksymalną szybkość pracy układu. Spójrzmy na rys. 5, na którym pokazano pojemność obciążenia i jej składniki w węźle wyjściowym Vout invertera, do którego dołączono następny inwerter.Pojemność Cgd to pojemność bramka-dren tranzystora (2*Cox*W), Cg to pojemność bramki (Cox*W*L), Cdb jest pojemnością między drenem a źródłem, a pojemność Cintreprezentuje pojemność połączeń. Z rysunku 5 wynika jasno, że pojemność w węźle Voutpierwszego inwertera jest sumą pojemności Cg tranzystorów M3 i M4, pojemności Cdb tranzystorów M1 i M2,oraz pojemności połączeń. Ale to nie wszystko. Są jeszcze pojemności Cgdtranzystorów, które przenoszą się na wejście i wyjście inwertera zwiększając pojemność w węźle Vout.W naszym przypadku, wszystkie cztery tranzystory poprzez swoje pojemności Cgdzwiększą jeszcze dodatkowo pojemność widzianą w węźle Vout pierwszego inwertera.

W nowych technologiach, w których rozmiary tranzystora są mniejsze, uzyskuje się zmniejszenie wartości pojemności obciążenia,dzięki ograniczeniu wszystkich wyszczególnionych na rys. 5pojemności tranzystora. Pojemności połączeń mogą być zminimalizowane tylko poprzez odpowiednie prowadzenie połączeń pomiędzy bramkami.

Zwarciowy pobór mocy

Zgodnie z powyższą dyskusją moc tracona na przełączanie wynika tylko i wyłącznie z poboru energii potrzebnego do naładowania i rozładowania pojemności obciążającej i jest niezależna od czasu narastania i opadania sygnału wejściowego. Jednak w rzeczywistości, czasy opadania i narastania nie są nieskończenie krótkie, co sprawia, że przez pewien okres w momencie przełączania obydwa tranzystory inwertera przewodzą równocześnie tworząc w ten sposób bezpośrednie połączenie między zasilaniem a masą. Prąd, który wtedy płynie odpowiada za zwarciowe straty mocy i nie ma wpływu na procesy ładowania i rozładowywania pojemności w układzie. Zjawisko to pokazano schematycznie na rys. 6.Kiedy napięcie wejściowe jest niższe od napięcia progowego Vt, tylko tranzystor PMOS przewodzi, a tranzystor NMOS jest wyłączony. W momencie, gdy narastające zbocze sygnału wejściowego osiągnie wartość Vt, również i tranzystor NMOS zacznie przewodzić. Prąd zwarciowy Izwpopłynie pomiędzy zasilaniem a masą. Dalsze zwiększanie napięcia wejściowego do wartości Vdd -Vt spowoduje zatkanie tranzystora PMOS i zakończy przepływ prądu zwarciowego. Takie samo zjawisko występuje przy opadającym zboczu sygnału wejściowego. Zwarciowy pobór mocy zależy od czasu narastania i opadania sygnału. Dla bardzo krótkich czasów narastania może być nawet zaniedbany.

Podsumowanie

Całkowity prąd pobierany przez układy CMOS jest sumą prądów dynamicznych i statycznych. Sumaryczny prąd statyczny, który płynie wstanie ustalonym składa się z prądu podprogowego zatkanego tranzystora i prądu wstecznego, czyli prądu upływu spolaryzowanych zaporowo drenów tranzystorów. Prądy dynamiczne wynikają z procesu przeładowywania pojemności obciążającej oraz ze skończonych czasów narastania i opadania sygnału wyjściowego.

Na podstawie literatury można w przybliżeniu oszacować, że dynamiczny pobór mocy to 90% całkowitego zużycia energii, a pozostałe 10%to pobór statyczny. Widać więc, że prąd statyczny ma już znaczący udział w całkowitym poborze prądu. W mniej więcej w takiej samej proporcji układają się składowe prądu dynamicznego: 90% to prąd przeładowywania pojemności, a 10% prąd zwarciowy.

Statyczny pobór mocy może być zredukowany poprzez zastosowanie techniki VTCMOS. Niestety kosztem dodatkowych układów sterujących napięciem zasilania podłoża układu scalonego. Technika ta jest stosowana w urządzeniach przenośnych, dzięki czemu mogą pozostawać w trybie uśpienia przez wiele godzin.

Dynamiczny pobór mocy w układach CMOS redukuje się zmniejszając napięcie zasilania oraz zmniejszając rozmiary tranzystora. Niestety, niższe napięcia zasilania oraz napięcia progowe przyczyniają się do wzrostu prądów statycznych. Jest to o tyle ważne, że w stosowanych obecnie niskonapięciowych technologiach statyczne straty mocy zaczynają być porównywalne ze stratami dynamicznymi.

Dariusz Pieńkowski