Powyższa konstatacja sprawia, że tak naprawdę za prędkość działania aplikacji odpowiedzialnych jedynie 10%÷20% kodu źródłowego programu. W związku z tym, optymalizacja względnie niedużej części całego opisu filtru cyfrowego może pozwolić na znaczące przyspieszenie pracy układu przetwarzania sygnałów.

Cechy szczególne nowoczesnych DSP

Aby optymalnie zaimplementować filtr cyfrowy w układzie DSP, konieczna jest znajomość nowoczesnych technik, jakie stosowane są w obecnie produkowanych procesorach sygnałowych. To dzięki nim możliwe jest wykonywanie operacji typowych dla zaawansowanego przetwarzania danych strumieniowych.

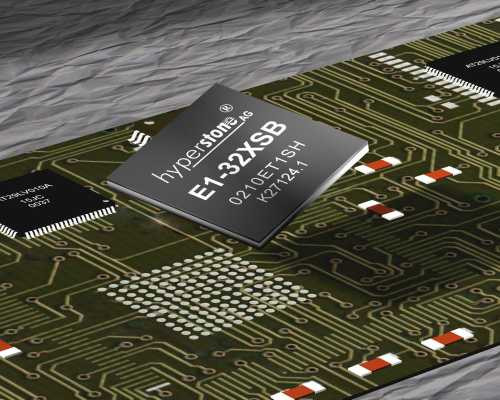

Jednym z najbardziej znanych udogodnień są operacje typu MAC (Multiply and Accumulate). Wywoływane są jako pojedyncze instrukcje procesora i polegają na następującym po sobie przemnożeniu dwóch wartości i dodaniu wyniku do wartości zapisanej w rejestrze sumowania. Przykładem może być poniższy kod, zapisany w instrukcjach języka asembler dla procesora sygnałowego z rodziny C5000 firmy Texas Instruments o architekturze C55x (rys. 1).