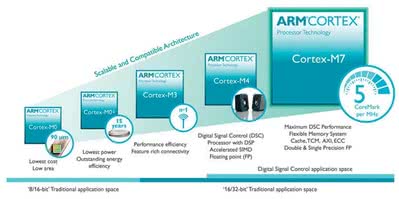

Mikrokontrolery STM32F7 dzięki swojej budowie i możliwościom rdzenia Cortex-M7 stanowią wydajnościowy pomost pomiędzy mikrokontrolerami i mikroprocesorami. Rdzeń zaimplementowany przez STMicroelectronics może być taktowany z częstotliwością do 200 MHz, co przy średniej wydajności 2,14 DMIPS/MHz daje wynik 428 DMIPS, w przypadku programów zoptymalizowanych pod względem wydajności nawet 3,23 DMIPS/MHz (5 CoreMark/MHz).

Od strony technicznej Cortex-M7 to rozbudowana wersja rdzenia Cortex-M4, przystosowana do współpracy z szybką pamięcią SRAM TCM (dla danych i instrukcji programu), wyposażoną w pamięci cache dla danych i instrukcji, a także zaawansowany 6-poziomowy mechanizm przetwarzania potokowego z predykcją oraz sprzętowym wsparciem superskalarnego wykonywania programu.

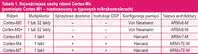

Architektura rdzenia Cortex-M7 jest taka sama jak w przypadku rdzeni Cortex-M3 i Cortex-M4 (zgodnie z nomenklaturą firmy ARM nosi ona oznaczenie ARMv7E-M - tabela 1), a jego działanie jest zgodne z definicją architektury Harvard: magistrale zapewniające komunikację z pamięcią danych i poleceń są rozdzielone. Firma ARM w opisie konstrukcyjnym rdzenia użyła nowych mechanizmów obniżających pobór mocy, które są dostępne opcjonalnie podczas implementacji rdzenia w nowoczesnych technologiach półprzewodnikowych, charakteryzujących się niewielkim wymiarem charakterystycznym.

Nowa magistrala

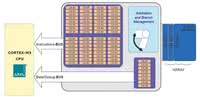

Ważnym udoskonaleniem wprowadzonym w rdzeniu Cortex-M7 jest nowa magistrala służąca do komunikacji CPU z blokami peryferyjnymi, który ma wpływ na wypadkową prędkość pracy mikrokontrolera: Master AXI (AXIM, rys. 1). Zapewnia ona "splatanie" kilku kanałów magistrali AHB w jeden, bardzo szybki kanał dwukierunkowej komunikacji rdzenia z otoczeniem (w rdzeniach Cortex-M4 rdzeń komunikuje się z otoczeniem za pomocą "standardowych" interfejsów-magistral AHB).

Rozwiązania zastosowane przez firmę ARM w rdzeniu Cortex-M7 pozwalają na szybszy niż w przypadku poprzedników dostęp rdzenia do zawartości pamięci SRAM i Flash, oczywiście przy założeniu, że konstrukcja pamięci umożliwia bezpośredni odczyt danych z relatywnie wysoką częstotliwością (dla typowych pamięci nieulotnych za taką uchodzi 70...90 MHz).

Tabela 1. Najważniejsze cechy rdzeni Cortex-Mx (pominięto Cortex-M1 - niestosowany w typowych mikrokontrolerach)

Żeby uniknąć efektu "wąskiego gardła" w dostępie do zawartości pamięci Flash, producenci stosują różne rozwiązania: w mikrokontrolerach STM32 pobieranie danych z pamięci Flash jest buforowane za pomocą sprzętowego akceleratora ART (Adaptive Real-Time).

Jego działanie polega m.in. na dekompozycji 128-bitowych słów przechowywanych w pamięci Flash na słowa 16- lub 32-bitowe (rys. 3), które są kolejkowane w lokalnej (wbudowanej w ART) pamięci cache. Według informacji publikowanych przez producenta, mechanizmy usprawniające dostęp do zawartości Flash spowodowały, że nie ma konieczności używania podczas odczytu wait-state'ów dotychczas istotnie zmniejszających realną prędkość transferu danych.

Efekty zabiegów konstruktorów mikrokontrolerów STM32F7 widać w ich wydajności: przy maksymalnej dopuszczalnej częstotliwości taktowania CPU, wynoszącej obecnie 200 MHz, uzyskiwana jest wartość CoreMark na poziomie 1000 (vs 608 w przypadku STM32F4 @180 MHz), a zgodnie z wybiegającymi w niezbyt odległą przyszłość zapowiedziami producenta, planowane jest osiągnięcie wyniku testu CoreMark o wartości 2000.

Układy peryferyjne

Producent, opracowując mikrokontrolery STM32F7, zadbał o wyposażenie ich w bogaty zestaw elementów peryferyjnych (schemat blokowy pokazano na rys. 2), w skład którego wchodzą wszystkie interfejsy znane z poprzednich generacji mikrokontrolerów oraz kilka nowych rozwiązań, w tym m.in.:

- zmodyfikowany podsystem generacji sygnałów zegarowych, pozwalający na modyfikację częstotliwości taktowania bloków peryferyjnych bez konieczności zmiany ustawień taktowania CPU,

- dwukanałowy transceiver I2S z obsługą SPDIF oraz 3 półdupleksowe kanały wejściowe SPDIF, interfejsy USBOTG z wydzielonym zasilaniem, co pozwala korzystać z tego interfejsu także przy zasilaniu mikrokontrolera napięciem 1,8 V,

- dwa interfejsy QSPI, które sprzętowo realizują transmisję danych z pamięciami wyposażonymi w 1-, 4- lub 8-bitowe interfejsy komunikacyjne.

Mogłoby się wydawać, że bogate wyposażenie wewnętrzne i duże możliwości obliczeniowe muszą spowodować wzrost mocy pobieranej podczas pracy, ale według zapewnień producenta cechy te nie wpłynęły na pogorszenie ich parametrów "oszczędnościowych" w porównaniu z układami STM32F4, co pozwoliło uzyskać wynik 7 CoreMark/mW w trybie Run, statyczny pobór 120 mA w trybie STOP z podtrzymaniem zawartości pamięci SRAM, 1,7 mA w trybie STANDBY oraz 0,1 mA w trybie VBAT.

Projektanci podrodziny STM32F7 zadbali o jeszcze jedną ważną rzecz: ich kompatybilność z mikrokontrolerami STM32F4, zarówno pod kątem fizycznego rozmieszczenia wyprowadzeń w obudowie, jak i ich kompatybilności elektryczno-czasowej, co minimalizuje ryzyko powstania problemów w przypadku modyfikowania konstrukcji urządzeń z tymi mikrokontrolerami.

Zabieg ten niezupełnie udał się w przypadku najmniejszych dostępnych w rodzinie STM32F7 obudów - LQFP100 - w których 30 wyprowadzeń jest umieszczonych odmiennie w obydwu podrodzinach. Pozostałe planowane wersje obudów (na razie dla mikrokontrolerów STM32F75x) - LQFP144, LQFP176, UFBGA176, LQFP208, TFBGA216 oraz WLCSP143 - dokładnie odpowiadają mikrokontrolerom STM32F4.

Piotr Zbysiński