Sterowniki bramki tranzystorów pracujących w układach mostkowych w konwerterach energii elektrycznej są znane na rynku od lat 90. ubiegłego wieku, a ich pomysłodawcą i pierwszym producentem była firma International Rectifier (IR). Po przejęciu IR w 2015 r. przez Infineon Technologies zainwestowano w poprawę kluczowych aspektów technicznych, z czego najważniejsza zmiana polegała na zmianie procesu półprzewodnikowego na technologię "krzem na izolatorze" (Silicon on Insulator, SOI).

Na początek zmiana technologii objęła najpopularniejsze układy sterowników bramek HVIC, takie jak IR(S)2106, IR(S)2108, IR(S)2109, IR(S)21091, IR(S)- 2181, IR(S)2183 i IR(S)2184. Sterowniki o małym wyjściowym natężeniu prądu (+290 mA/–700 mA), jak 2ED2106, 2ED2108, 2ED2109, 2ED21091 oraz wersje o dużym prądzie (±2,5 A), jak 2ED2181, 2ED2182, 2ED2183, 2ED2184, to z kolei już całkowicie nowe opracowania Infineona, które zachowują kompatybilność ze starymi wersjami IR, ale zapewniają lepszą wydajność i niezawodność. Nowością w ofercie jest też wypuszczony niedawno sterownik bramki dolnego tranzystora mostka – 1ED44175/76 ze zintegrowanym zabezpieczeniem nadprądowym i sygnalizatorem błędów, który kierowany jest do sterowania IGBT-em lub MOSFETem w układach korekcji współczynnika mocy lub aplikacjach konwerterów push-push lub fl yback, a więc takich, gdzie tranzystor kluczujący jest dołączony źródłem do masy.

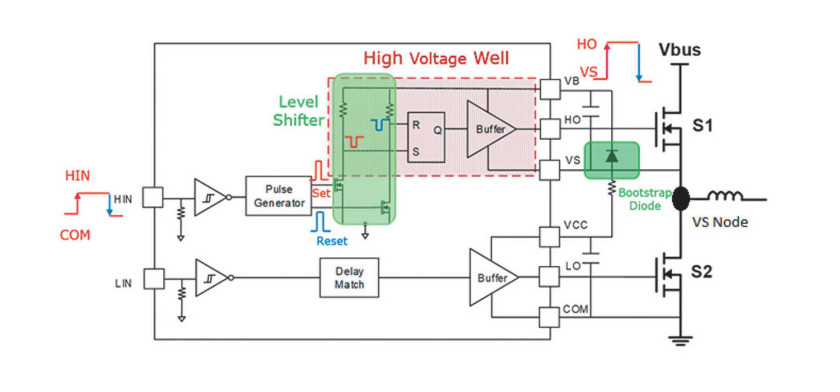

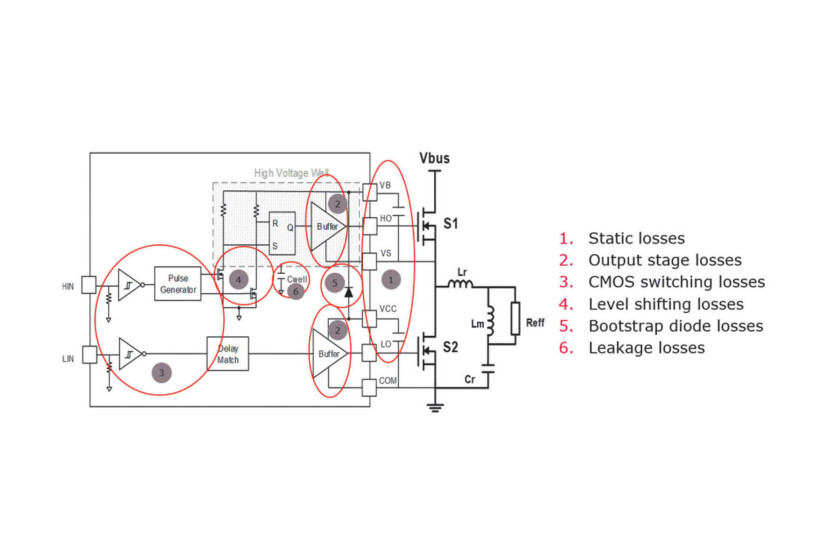

Sterownik bramki górnego tranzystora mostka (HVIC) działa w następujący sposób (rys. 1). Generator generuje impulsy na każdym zboczu sygnału wejściowego HIN. Przesuwnik poziomu przesuwa te impulsy odniesione do GND na analogiczne sygnały odniesione do górnej (wysokonapięciowej) linii odniesienia związanej z górnym tranzystorem mostka S1. Następnie przerzutnik RS zatrzaskuje (zapamiętuje) te impulsy, aby zapewnić bezbłędne wysterowanie drivera tranzystora przez cały wymagany czas.

W układzie jest też blok zapewniający dopasowanie opóźnień pojawiających się w wyniku przenoszenia poziomu impulsu, niezerowego czasu przełączania przerzutnika RS. Znajduje się on na dolnej gałęzi i dodaje tam niezbędne opóźnienie sygnału, które zapobiega niekontrolowanemu przełączeniu tranzystorów, w tym sytuacji, gdy oba, górny i dolny, są w stanie przewodzenia, czyli zapobiega przepływowi prądu skrośnego. Warto zauważyć, że sterownik nie potrzebuje dodatkowego izolowanego galwanicznie zasilacza dla strony górnej (wysokonapięciowej). Do tego wykorzystano układ bootstrapu, czyli podbijający napięcie zasilacz dla górnego drivera z diodą i kondensatorem gromadzącym energię.

Technologia SOI zapewnia możliwość działania w układach mostkowych do 1200 V, a więc przy typowych wartościach panujących w sieci energetycznej zapewnia dużą odporność na przepięcia. Podobne zabezpieczenia chronią sterownik bramki przed ujemnymi napięciami oscylacji pojawiającymi się na skutek komutacji sygnałów mocy przy obecności pasożytniczych reaktancji.

Jak wspomniano wcześniej, do zasilania drivera górnego tranzystora MOSFET wykorzystano układ bootstrapu. Pozwala on na uzyskanie napięcia zasilającego VB o kilkanaście woltów wyższego od napięcia zasilania (dokładnie o wartość VCC), co jest niezbędne do poprawnej pracy górnego MOSFET-a. W stanie, gdy jest on otwarty, napięcie na jego źródle jest praktycznie równe napięciu panującemu na górnej szynie zasilającej (VS≈VBUS). Wówczas napięcie na bramce musi być jeszcze wyższe, aby zapewnić utrzymanie tranzystora w stanie otwarcia i stąd bierze się wymóg, aby VS>VBUS. Układ bootstrapu realizuje ten warunek, jest tani i prosty w realizacji, niemniej wymaga zwrócenia uwagi na to, aby ładunek do kondensatora był dostarczany dostatecznie często, a jego pojemność zapewniała odpowiednią wydajność prądową drivera.

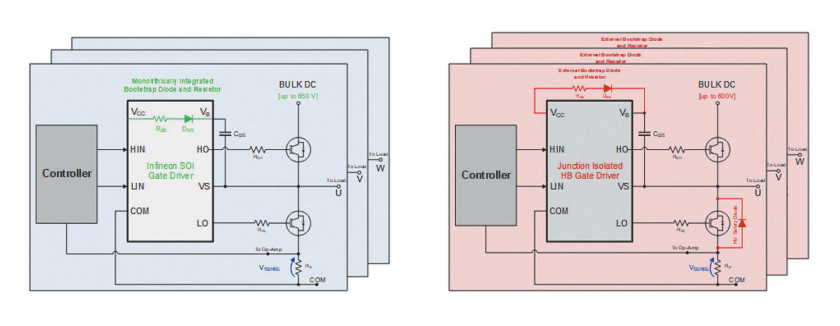

Na rysunku 2 pokazano z kolei typowe elementy zasilacza typu bootstrap stosowanego w tradycyjnych rozwiązaniach sterowników HVIC. Wykorzystywana tam dioda powinna charakteryzować się krótkim czasem regeneracji (typowo trr <100 ns) i mieć napięcie blokowania wyższe niż napięcie magistrali VBUS. Umieszczony szeregowo z diodą rezystor Rboot ma zazwyczaj niską wartość (<50 Ω) i służy do ograniczenia początkowego prądu ładowania kondensatora bootstrapu. Kondensator ten ładuje się do napięcia VCC, gdy tranzystor dolny jest włączony, a przełącznik po stronie górnej wyłączony. Element ten rozładowuje się, gdy dolny MOSFET jest wyłączony, a górny włączony. Jego pojemność powinna być wystarczająco duża, aby był on w stanie utrzymać napięcie zasilania dla drivera górnego w przez min. połowę cyklu przełączenia, gdy dioda nie przewodzi i jest on jedynym źródłem energii dla drivera. Infineon podaje w kartach katalogowych metodę obliczania wartości tej pojemności i dostarcza też kalkulator online na swojej stronie internetowej.

Nowa rodzina sterowników wykonanych w technologii SOI ma już tę diodę układu bootstrapu i szeregowy rezystor zintegrowane w strukturze, jak pokazano w lewej części rysunku 2. Realizacja stopnia mocy jest dzięki temu tańsza, a zajętość miejsca na PCB jest zmniejszona, co widać szczególnie wyraźnie w rozbudowanych konstrukcjach 3-fazowych, gdzie mostek zawiera 6 tranzystorów.

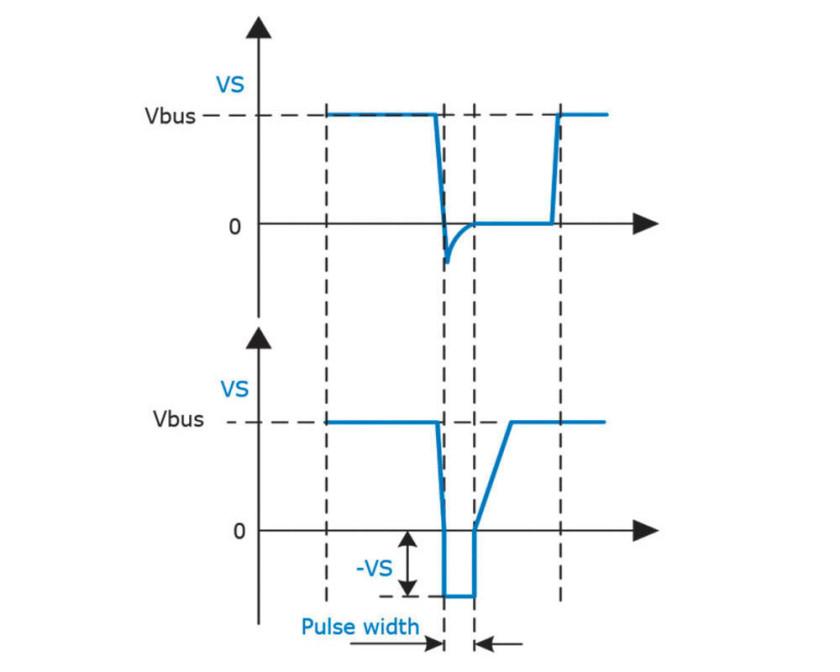

Częstym problemem we współczesnych konwerterach impulsowych dużej mocy są stany nieustalone pojawiające się w punkcie środkowym mostka (VS na rys. 1), w czasie gdy dochodzi do komutacji dużej wartości prądu płynącego przez tranzystory mocy. Typowa realizacja falownika trójfazowego w układzie podobnym do pokazanego na rysunku 2 ma przełącznik górny umieszczony w VBUS i VS. Kiedy się on wyłącza, a przez obciążenie indukcyjne jeszcze płynie prąd, następuje komutacja prądu z górnego przełącznika (Q1) do diody równoległej tranzystora dolnego w tej samej gałęzi mostka. W tym samym momencie napięcie w punkcie VS obniża się z poziomu VBUS do zera. Niemniej w praktyce powstaje przerzut ujemny i napięcie VS przyjmuje wartości ujemne, a więc dolnej szyny zasilania (masy konwertera). Wielkość tego przerzutu zależy od wartości reaktancji pasożytniczych w układzie, projektu PCB, parametrów tranzystorów itp. i niestety jest problemem wymagającym uwagi konstruktora.

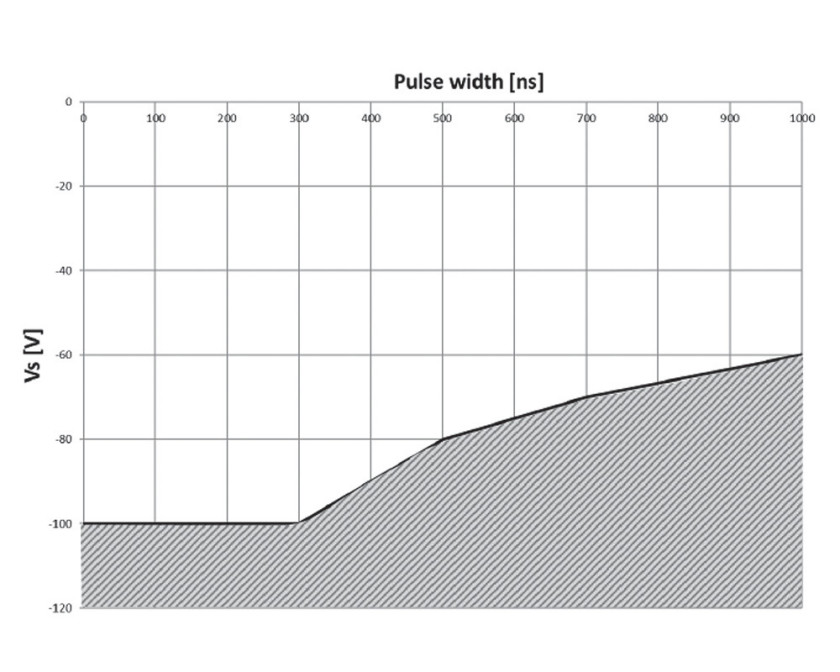

Rysunek 3 ilustruje ten problem dokładniej. Jego lewa część pokazuje charakterystyczny przerzut –VS podczas testu za pomocą impulsu trwającego od 10 ns do 1 μs. Przerzut jest zagrożeniem dla układu sterownika i badania pokazują, że konkurencyjne konstrukcje sterowników w tym zakresie zawodzą przy wartościach przerzutu poniżej –70 V w czasie dłuższym od 100 ns. Sterowniki bramek Infineona wykonane w procesie SOI są w stanie wytrzymać ujemny impuls VS –100 V o szerokości 300 ns, a więc ich podatność na uszkodzenie jest znacznie mniejsza. Taki poziom odporności jest uznawany za bardzo duży i zapewnia wysoką niezawodność zasilaczy i napędów. Dla konstruktorów Infineon dostarcza w kartach katalogowych wykresy definiujące obszar pracy bezpiecznej (Negative Transient SOA, NTSOA), jak pokazano w prawej połowie rysunku 3, aby mogli dokładnie wyznaczyć granice pracy aplikacji.

Moc rozpraszana przez układ scalony sterownika bramki pochodzi z kilku źródeł (rys. 4). Pierwsze to straty statyczne i te związane z prądami upływu. Kolejne zależą już od częstotliwości komutacji i wynikają z konieczności przeładowywania pojemności bramka-źródło tranzystora oraz wiążą się z procesem przenoszenia poziomu sygnału sterującego w górę. W tym ostatnim aspekcie nowa technologia SOI firmy Infineon charakteryzuje się znacznie mniejszymi stratami w porównaniu do starszych rozwiązań, co ułatwia budowę konwerterów działających z dużą szybkością przełączania bez dokuczliwych problemów z ciepłem.

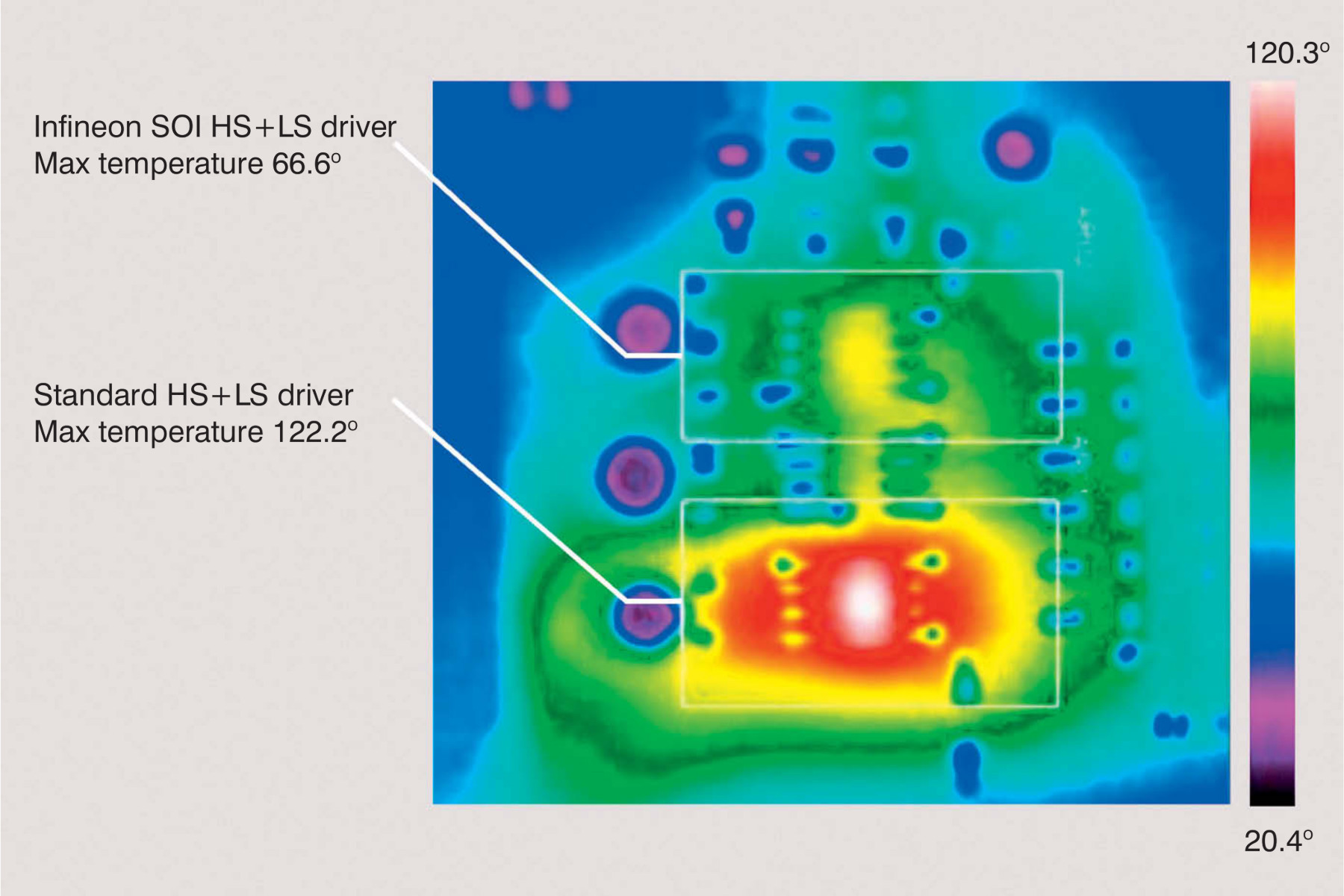

Rysunek 5 pokazuje porównawczy obraz z kamery termowizyjnej dwóch sterowników bramek z podobnymi funkcjami, ale bazującymi na różnych technologiach. Starszy IR(S)2106 ma wyższe straty niż równoważny nowy 2ED2106 przy 300 kHz. Przyrost temperatury jest prawie dwukrotnie mniejszy. Niższa temperatura przekłada się na większą niezawodność oraz pośrednio na łatwiejszą aplikację. Warto zauważyć, że nowe wersje są kompatybilne pinowo z poprzednikami.

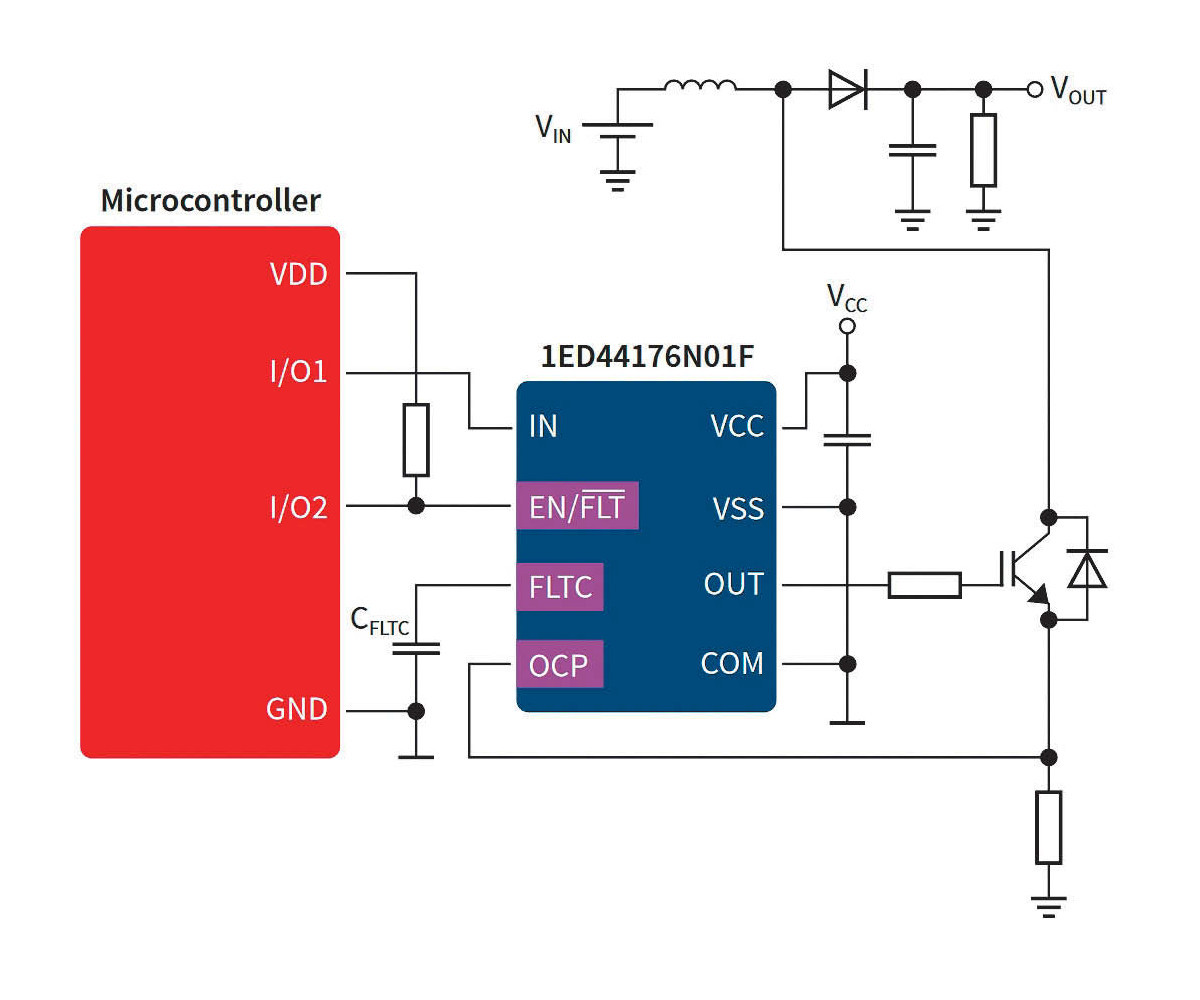

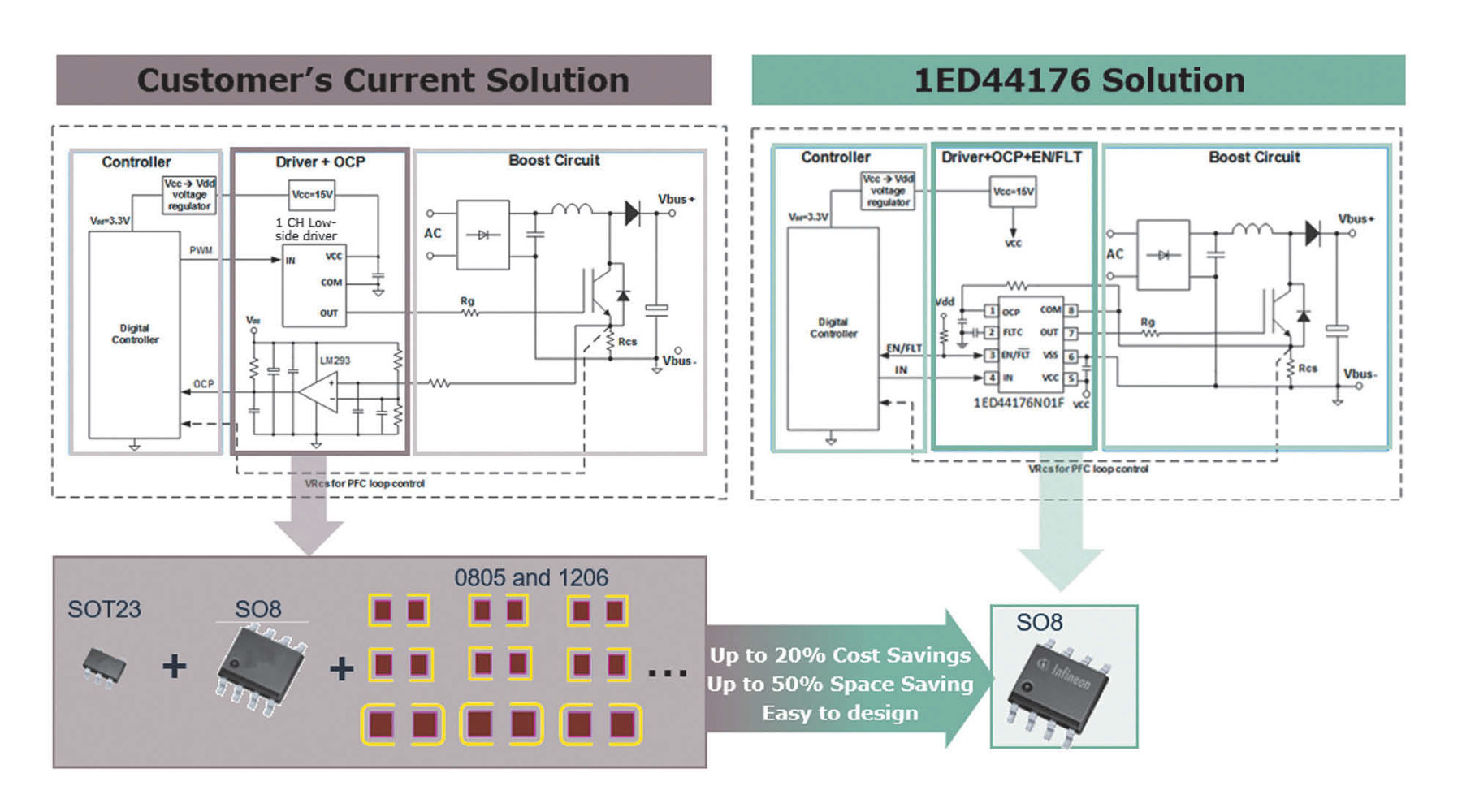

Kolejnym nowym sterownikiem bramki Infineona jest układ 1ED44176. Jest przeznaczony do sterowania dolnymi tranzystorami mostka lub pracy w układach, gdzie jest tylko jeden tranzystor przełączający i ma on źródło połączone z masą, np. w korektorach współczynnika mocy (PFC) z obwodami zabezpieczenia nadprądowego (OCP) – rysunek 6. W takich realizacjach funkcja OCP jest zwykle implementowana przy użyciu obwodu do pomiaru prądu oraz komparatora progowego, np. LM293 wraz z siecią rezystorów i kondensatorów. W porównaniu do tego typowego podejścia 1ED44176N01F zapewnia tutaj do 20% kosztów realizacji i do 50% oszczędności miejsca dzięki integracji wewnątrz sterownika komparatora układu OCP, który na dodatek zapewnia wysoką dokładność progu wykrywania prądu nadmiarowego rzędu ±5% (rys. 7). 1ED44176N01F ma również wyjście sygnału błędu do mikrokontrolera i funkcję enable na tym samym pinie oraz rozdzielone masy (sygnałową i zasilającą). Jest dostępny w obudowie DSO-8. Rysunek 7 pokazuje typowe zastosowanie 1ED44176N01F w aplikacji PFC.

Poza wymienionymi w artykule przykładami układów w ofercie pojawiło się w sumie aż 16 nowych jednostek, które zapewniają szeroki wybór i dobre możliwości dopasowania dla inżyniera projektującego różnorodne aplikacje energoelektroniczne.

Srivatsa Raghunath,

Staff Engineer-Gate Drivers,

Integrated Power & Discretes,

Infineon Technologies

tel 22 377 69 50, www.infineon.com