Tranzystory MOSFET oraz IGBT stosowane są powszechnie w roli przełączników w obwodach mocy, np. w zasilaczach oraz układach sterujących pracą silników elektrycznych. Wejściem sterującym tego typu komponentów jest bramka. Pozostałe dwie elektrody to odpowiednio dren oraz źródło (w przypadku MOSFET) lub kolektor i emiter (w przypadku IGBT). W celu przełączenia tranzystora konieczne jest podanie odpowiedniej wartości napięcia bramka-źródło (bramka-emiter w przypadku IGBT). Wytworzenie odpowiedniej wartości napięcia przy jednoczesnym zapewnieniu wystarczająco wysokiego natężenia prądu bramki (w celu możliwie szybkiego przeładowania wewnętrznych pojemności tranzystora) należy do głównych zadań sterownika bramki.

Przyczyny korzystania z układów sterowników

Każdy tranzystor MOSFET/IGBT charakteryzuje się niezerowym czasem przełączania, ponieważ w jego wewnętrznej strukturze występuje pasożytnicza pojemność bramki. Proces włączania tranzystora przedstawić można jako ładowanie tej pojemności, zaś wyłączanie może zostać wyjaśnione jako jej rozładowanie. Najmniejsza wartość napięcia bramki pozwalająca rozpocząć ładowanie pojemności bramki to napięcie progowe (napięcie tworzenia kanału). W celu przyspieszenia procesu przełączania konieczne jest podanie na wejście bramki napięcia o wartości większej od napięcia progowego.

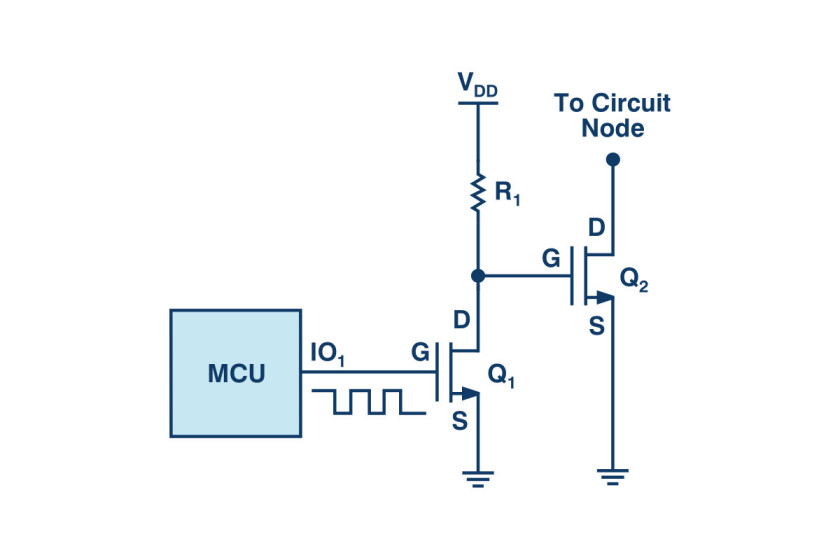

W przypadku konieczności przełączania sygnałów mocy nie jest z reguły możliwe bezpośrednie sterowanie bramką przełącznika za pomocą wyjścia układu cyfrowego, ponieważ napięcie bramki wymagane do załączenia tranzystora przekracza poziomy logiczne występujące w układach CMOS/TTL. Z tego powodu niezbędne jest zastosowanie pewnego rodzaju interfejsu, umożliwiającego konwersję sygnałów logicznych z wyjścia cyfrowego na poziomy napięć wymagane przez przełącznik mocy. Przykład tego typu rozwiązania przedstawiono na rysunku 1 – wyjście cyfrowe steruje bramką tranzystora MOSFET z kanałem typu n, ten zaś umożliwia załączenie tranzystora MOSFET pełniącego funkcję przełącznika mocy.

W przypadku układu z rysunku 1, gdy wyjście IO1 ustawione jest w stan niski, to VGSQ1 pozostaje niższe niż VTHQ1, zatem tranzystor Q1 pozostaje wyłączony. W związku z tym na wejście bramki tranzystora Q2 podawana jest wartość napięcia VDD, pozwalająca na jego włączenie. Po zmianie IO1 na stan wysoki pojemność bramki tranzystora Q2 zostaje rozładowana poprzez włączony rezystor Q1. Napięcie bramki tranzystora Q2 spada do stanu niskiego, co wyłącza przełącznik i zatrzymuje przepływ prądu w obwodzie wyjściowym. Główną wadą tego typu układu jest występowanie mocy strat na rezystorze R1 (związanej ze spadkiem napięcia na tym elemencie w wyniku przepływu prądu) przez cały okres czasu, gdy tranzystor Q2 jest włączony.

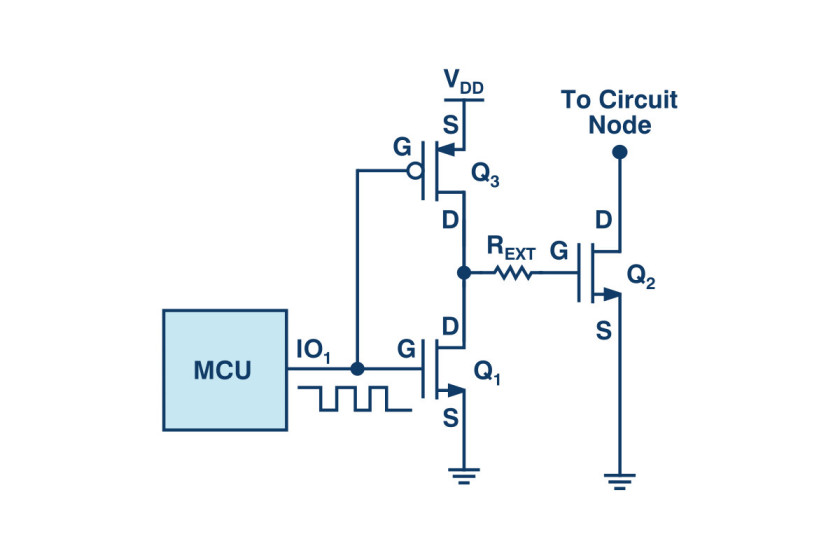

Modyfikacja obwodu w sposób pokazany na rysunku 2 pozwala wyeliminować ten kłopot. Tranzystor Q3 operujący razem z Q1 w układzie komplementarnym pozwala znacząco obniżyć moc strat układu. Wysoka rezystancja układu MOSFET w stanie wyłączenia ogranicza przepływ prądu w obwodzie. W celu poprawy jakości zboczy sygnału przełączającego do układu dołącza się zewnętrzny tranzystor o niewielkiej rezystancji, umieszczony pomiędzy drenem tranzystora Q1 oraz bramką tranzystora Q2. Kolejną zaletą konfiguracji z rysunku 2 jest łatwość wytworzenia tego typu struktury w krzemie – wytworzenie na podłożu półprzewodnikowym komplementarnej pary MOSFET jest znacznie prostsze niż skonstruowanie rezystora o w miarę precyzyjnie ustalonej wartości rezystancji. Układ z rysunku 2 jest w zasadzie punktem wyjście do konstrukcji typowego sterownika bramki tranzystora MOSFET. Tego typu układy są zazwyczaj wyposażone w dodatkowe obwody realizujące inne funkcjonalności, ich podstawowa rola wciąż polega jednak na generowania sygnału przełączającego o odpowiednim poziomie.

Podstawowe parametry sterownika bramki

Prąd wyjściowy

Sterownik musi nie tylko zapewniać odpowiedni poziom napięcia wyjściowego, pozwalający na sterowanie bramą tranzystora, ale również umożliwiać możliwie szybkie przeładowanie pojemności bramki, gwarantując krótki czas przełączania obwodu. Przebywanie w stanie przełączania jest wysoce niekorzystne z punktu widzenia efektywności obwodu, ponieważ w tym momencie przełącznik może umożliwić przepływ sygnału, charakteryzując się jednocześnie wysoką wartością rezystancji. W efekcie prowadzi to do istotnego wzrostu mocy strat rozpraszanej na tym elemencie i wzrostu jego temperatury. Przejście ze stanu przewodzenia do stanu rozłączenia powinno zatem nastąpić możliwie szybko. By osiągnąć taki rezultat, niezbędne jest zapewnienie możliwie wysokiego prądu wyjściowego sterowania bramki, pozwalającego na szybkie przeładowanie pojemności bramki.

Sterownik o wyższej wartości prądu wyjściowego umożliwia szybsze przełączenie tranzystora MOSFET, co przekłada się na niższa moc strat obwodu.

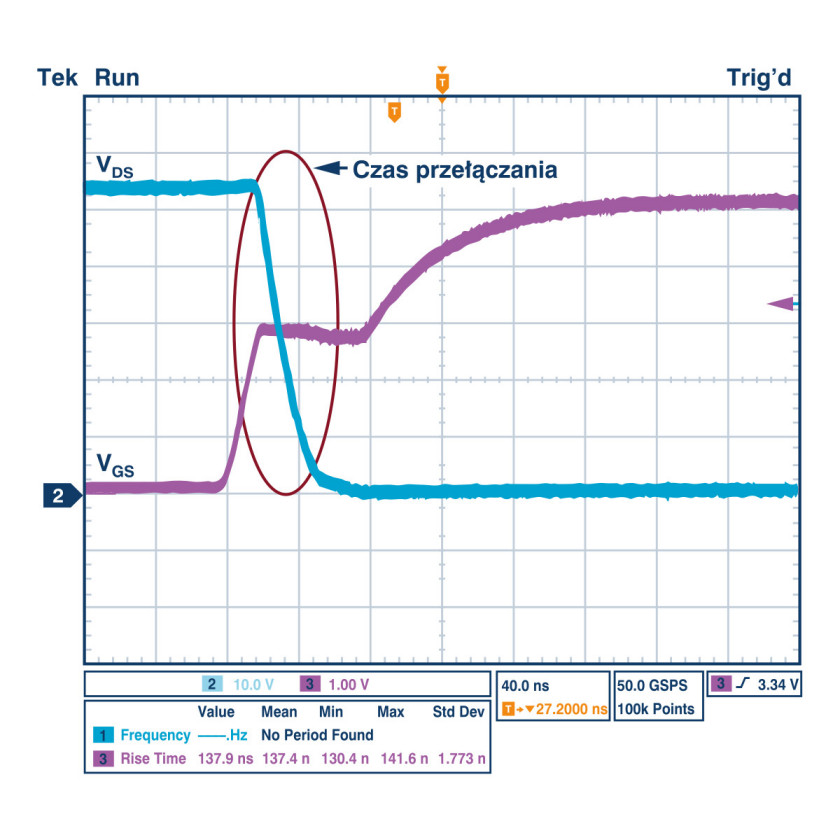

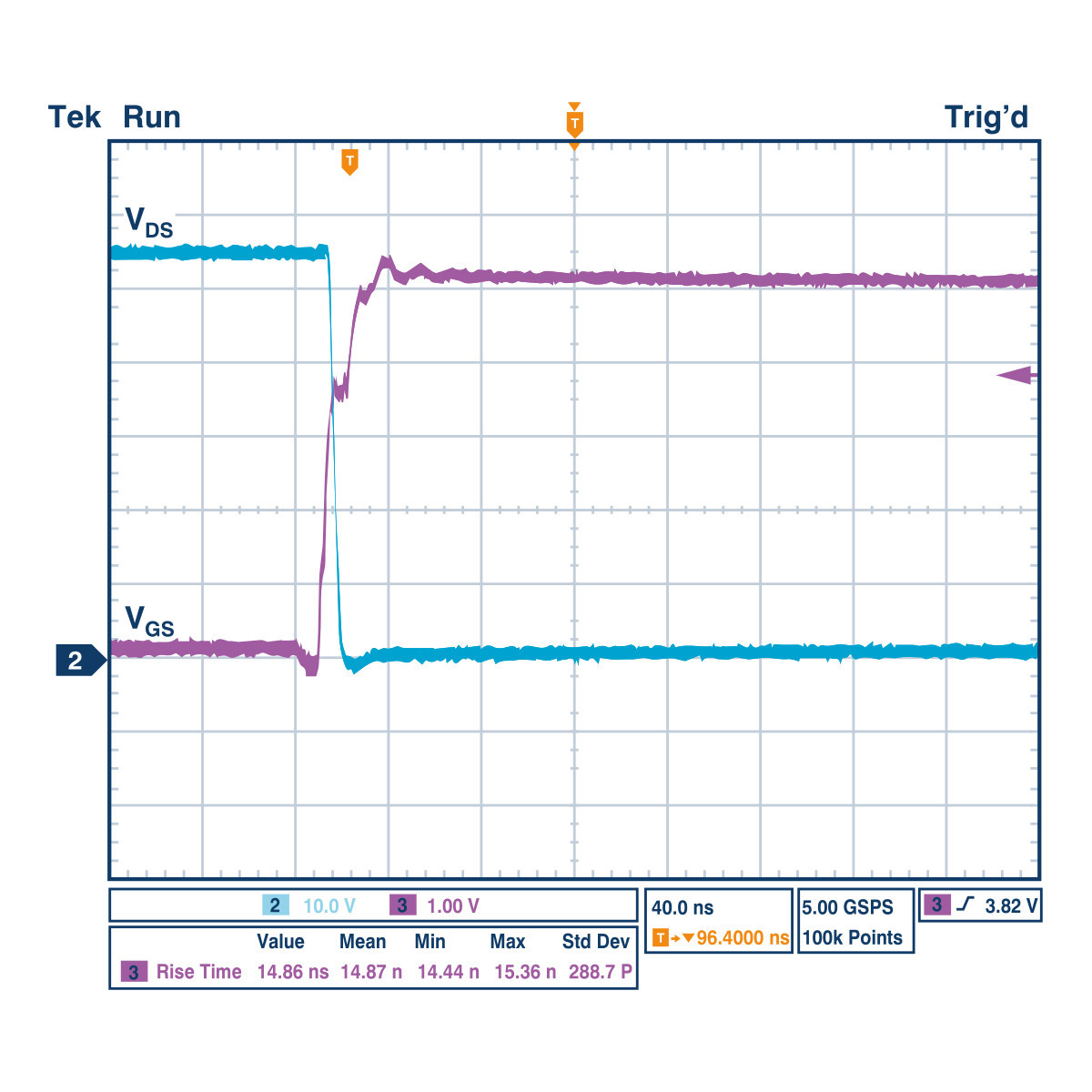

Na rysunkach 3 i 4 przedstawiono porównanie przebiegów przełączania typowego tranzystora MOSFET bezpośrednio z wyjścia układu logicznego oraz z wykorzystaniem sterownika bramki. Maksymalny prąd wyjściowy dla wyjścia typowego mikrokontrolera wynosi kilkadziesiąt miliamperów, zaś w przypadku sterowników bramki może być to wartość wielokrotnie większa, sięgająca nawet kilku lub kilkunastu amperów. Na rysunku 3 zauważyć można długi czas przełączania, znacząco wyższy niż w przypadku wykorzystania sterownika bramki (rys. 4).

Rezystancja w stanie przewodzenia (RDS(ON))

Kolejnym istotnym parametrem sterownika jest rezystancja kanału w stanie przewodzenia. W przypadku idealnego urządzenia wartość ta powinna wynosić 0, w praktyce nie przekracza zazwyczaj kilku omów.

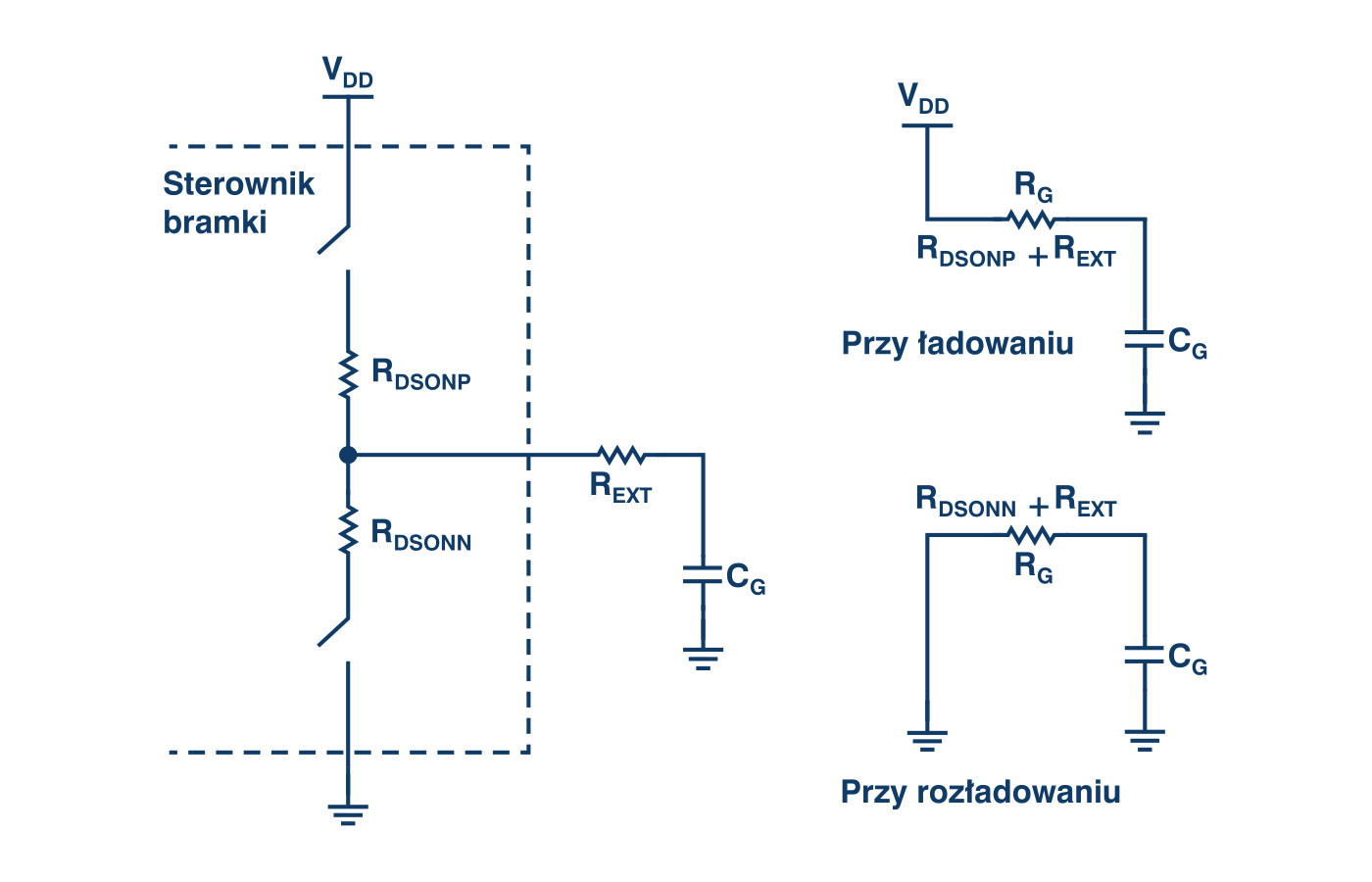

RDS(ON) jest jedną z głównych przyczyn warunkujących maksymalną wartość prądu wyjściowego sterownika. W celu dalszego ograniczenia prądu wyjściowego sterownika stosuje się dodatkowy rezystor zewnętrzny wpinany szeregowo pomiędzy wyjście sterownika a bramkę. Jak pokazano na rysunku 5, rezystancja układu podczas ładowania pojemności bramki stanowi sumę rezystancji kanału tranzystora MOSFET High-Side oraz zewnętrznej rezystancji, zaś rezystancja podczas rozładowania to suma rezystancji kanału tranzystora MOSFET low-side oraz zewnętrznej rezystancji.

RDS(ON) bezpośrednio wpływa też na poziom mocy strat sterownika. Im niższa wartość RDS(ON), tym mniejsza moc strat rozpraszanych w sterowniku przy zachowaniu tej samej wartości prądu wyjściowego. Niska wartość RDS(ON) jest zatem pożądana również ze względu na charakterystykę termiczną układu.

Czas propagacji

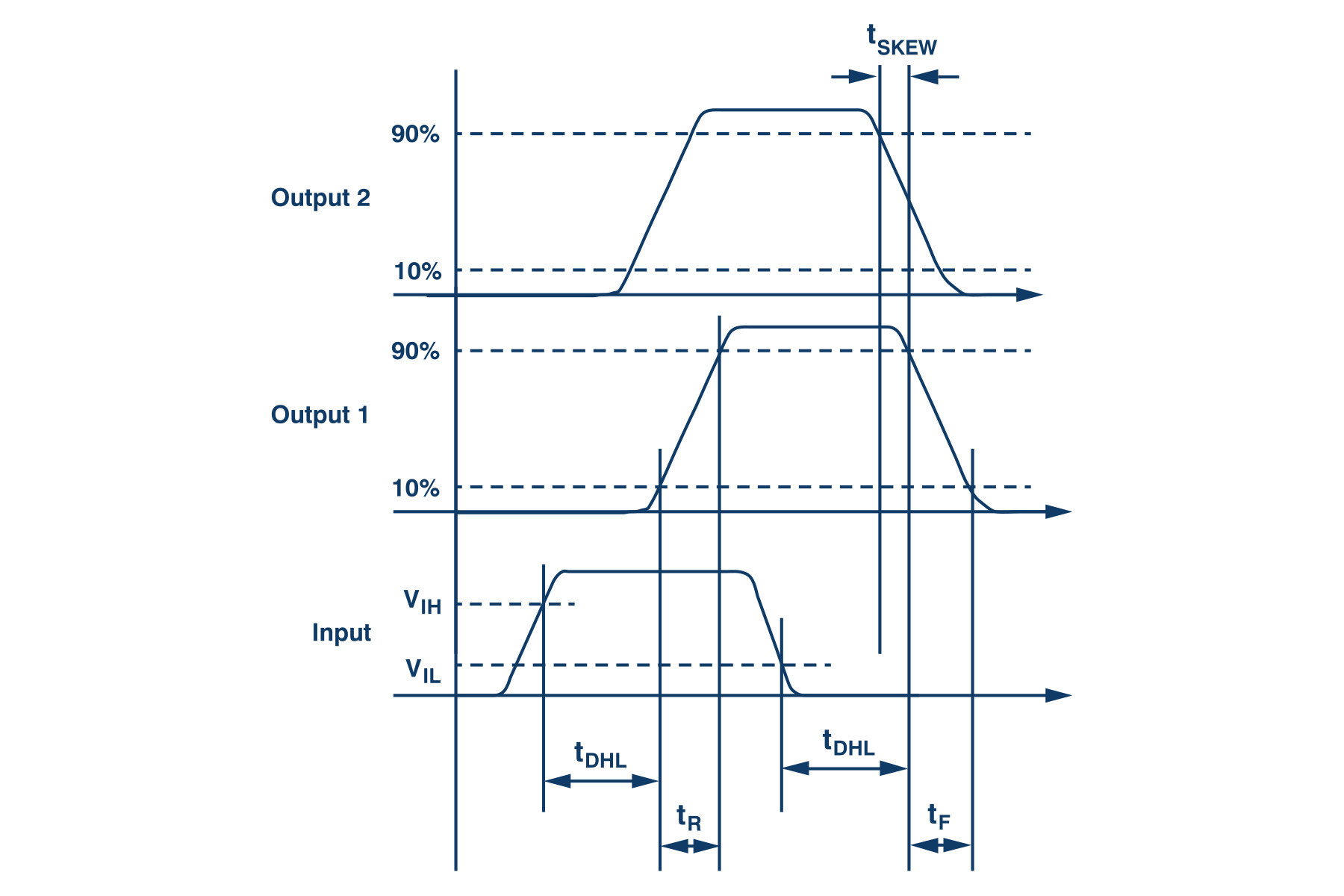

Czas propagacji sterownika definiowany jest jako czas pomiędzy zmianą wartości sygnału wejściowego a następującą w efekcie tego zmianą wartości sygnału wyjściowego. Innymi słowy, jest to czas reakcji układu na zmiany sygnału sterującego. Wyróżnia się tDLH, czyli czas propagacji sygnału wysokiego oraz tDHL, czyli czas propagacji sygnału niskiego. tDLH definiuje się jako czas pomiędzy wzrostem wartości sygnału wejściowego do wartości progowej a osiągnięciem przez sygnał wyjściowy 10% wartości docelowej. W podobny sposób tDHL definiowane jest jako czas pomiędzy spadkiem sygnału wejściowego do wartości progowej a spadkiem sygnału wyjściowego do 90% wartości startowej.

Różnicę pomiędzy tDLH oraz tDHL dla pojedynczego układu określa się jako parametr PWD, czyli Pulse Width Distortion. Różne egzemplarze tego samego modelu sterownika również mogą charakteryzować się nieco odmiennymi wartościami czasów propagacji – wynika to m.in. z niedoskonałości procesu produkcyjnego. Różnica ta określana jest jako tSKEW. W przypadku sterowników wielokanałowych, rozrzut czasów propagacji wyznaczany jest zarówno międzykanałowo, jak i pomiędzy egzemplarzami.

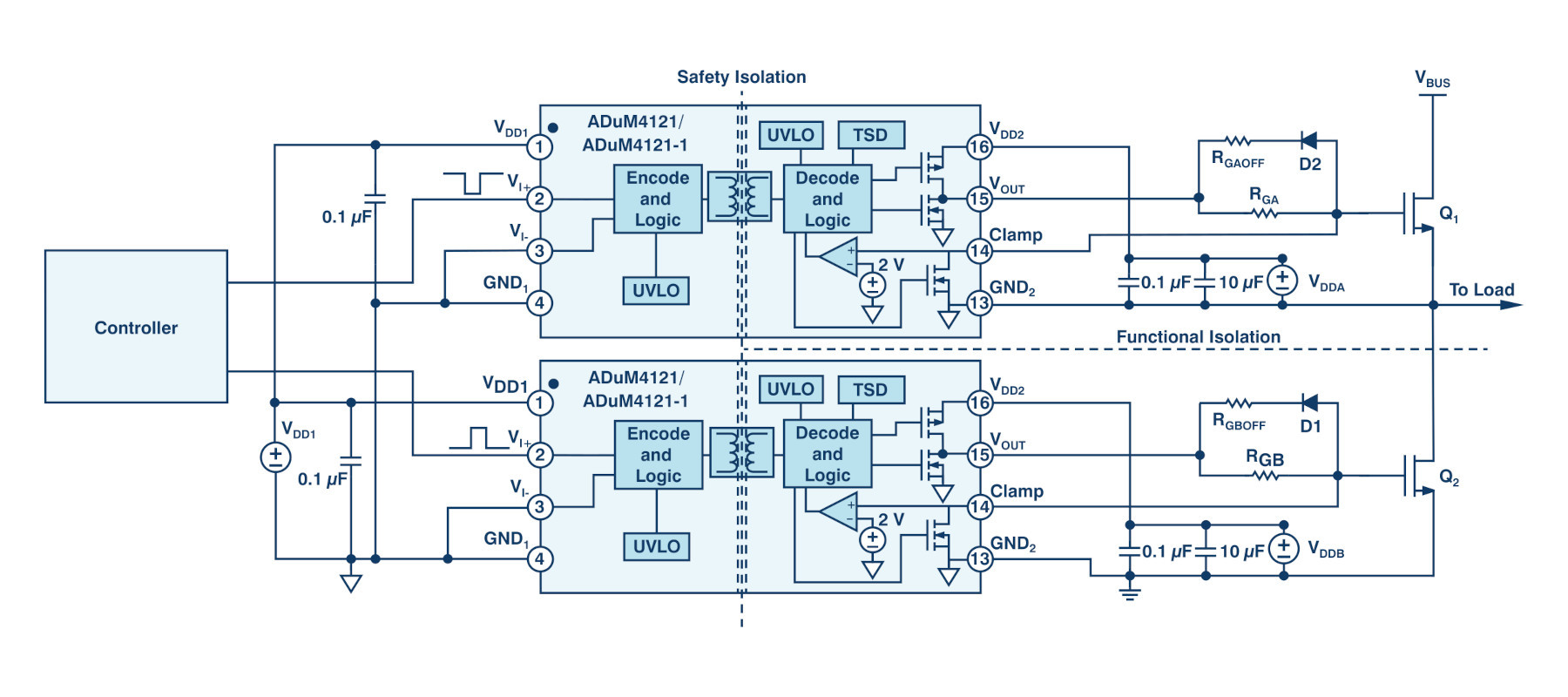

Na rysunku 7 przedstawiono typową konfigurację przykładowych sterowników bramki kontrolujących pracę pary tranzystorów MOSFET w konfiguracji półmostka. W takiej sytuacji jednoczesne włączenie tranzystorów Q1 oraz Q2 doprowadziłoby do zwarcia masy z zasilaniem, w efekcie zaś z dużym prawdopodobieństwem do permanentnego uszkodzenia układu. Biorąc pod uwagę pewną losowość w dystrybucji parametrów czasowych poszczególnych egzemplarzy sterowników, ryzyko wystąpienia zwarcia staje się całkiem spore. Aby zminimalizować to zagrożenie, sterowniki stosują dodatkowe opóźnienie przed przełączeniem stanu wyjścia, tzw. dead-time. Im większa precyzja wykonania sterowników (mniejsza wartość dystrybucji parametrów czasowych poszczególnych egzemplarzy), tym niższa wartość dead-time niezbędna jest do prawidłowej pracy systemu.

Izolacja elektryczna

W wielu urządzeniach dużej mocy konieczne jest zapewnienie izolacji galwanicznej pomiędzy obwodem sterowania a obwodem zasilania, m.in. ze względu na bezpieczeństwo użytkowników. Bariera izolacyjna pozwala na transfer informacji oraz energii, uniemożliwia jednak bezpośredni przepływ ładunku elektrycznego.

Załóżmy, że w przypadku układu z rysunku 7 napięcie VBUS wynosi kilkaset woltów, zaś prąd przepływający przez tę linię sięga kilkudziesięciu amperów. Przy braku izolacji galwanicznej jakakolwiek usterka obwodu mogłaby spowodować pojawienie się w obwodzie sterującym sygnału dużej mocy, stanowiącego zagrożenie dla zdrowia i życia użytkownika. W układzie tym niezbędne jest zatem zastosowanie bariery izolacyjnej.

Duża część modeli sterowników zapewnia izolację pomiędzy wejściem a wyjściem układu. Jakość tej izolacji określana jest przez wielkość napięcia przebicia. Im wyższa wartość tego parametru, tym lepsza ochrona zapewniana przez układ.

Kompatybilność elektromagnetyczna

Sterowniki MOSFET wykorzystywane są w różnego rodzaju otoczeniach, np. w środowisku przemysłowym, które charakteryzuje się obecnością wielu różnych źródeł zakłóceń elektromagnetycznych. Zakłócenia te nie powinny przeszkadzać w poprawnej pracy sterownika. Jedną z podstawowych miar odporności urządzenia na zakłócenia elektromagnetyczne jest parametr określający odporność na impulsowe zakłócenia w trybie wspólnym, czyli CMTI (Common Mode Transient Immunity). Wysoka wartość CMTI jest szczególnie istotna w przypadku urządzeń pracujących z wysoką częstotliwością przełączania oraz z bardzo wysokimi napięciami.

Podsumowanie

W tekście przedstawiono wybrane parametry sterowników bramek MOSFET, wraz z krótkim opisem ich roli dla poprawnej i efektywnej pracy urządzenia. Powyższy zbiór nie wyczerpuje pełnej listy parametrów tego typu urządzeń, które znaleźć można w opisach katalogowych, zamiast tego koncentruje się na charakterystykach specyficznych dla tej grupy układów. Podobnie jak w przypadku każdego układu elektronicznego, sterowniki również mają takie parametry jak dopuszczalny zakres temperatury otoczenia, napięcie zasilania czy liczba oraz rodzaj wyprowadzeń.

Damian Tomaszewski