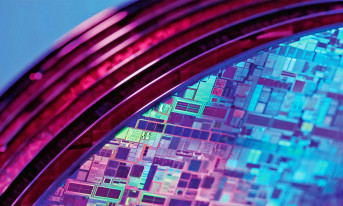

Nowa generacja tranzystorów SiC MOSFET od Navitas

Navitas Semiconductor, producent nowej generacji półprzewodników mocy i lider technologii z azotkiem galu (GaN) oraz węglikiem krzemu (SiC), wprowadza nowy standard niezawodności dla najbardziej wymagających zastosowań motoryzacyjnych i przemysłowych. Nowa generacja tranzystorów SiC MOSFET o napięciach 650 V i 1200 V, wykonanych w technologii „trench-assisted planar”, w połączeniu ze zoptymalizowaną obudową HV-T2Pak chłodzoną od góry, zapewnia największą w branży drogę upływu – 6,45 mm – spełniającą wymagania norm IEC dla aplikacji do 1200 V.

Nowe tranzystory SiC w obudowie HV-T2Pak zwiększają gęstość mocy i sprawność układów, poprawiając zarządzanie ciepłem oraz upraszczając projektowanie i produkcję na poziomie płytek PCB. Zastosowania docelowe obejmują pokładowe ładowarki (OBC) i przetwornice DC-DC w pojazdach elektrycznych, zasilacze centrów danych, falowniki fotowoltaiczne oraz systemy magazynowania energii (ESS), szybkie ładowarki DC do pojazdów EV, a także napędy silników HVAC.

AEC-Plus: Nowy standard niezawodności dla motoryzacji i przemysłu

Norma AEC-Q101, opracowana przez Automotive Electronics Council (AEC), definiuje wymagania kwalifikacyjne dla komponentów stosowanych w motoryzacji. Navitas wyznacza nowy punkt odniesienia w postaci standardu „AEC-Plus”, który przewyższa dotychczasowe wymagania AEC-Q101 oraz JEDEC, oferując jeszcze wyższy poziom niezawodności i trwałości.

Zakres kwalifikacji „AEC-Plus” obejmuje:

- Dynamiczne testy napięcia wstecznego (D-HTRB) oraz bramki (D-HTGB), odzwierciedlające realistyczne profile obciążenia

- Ponad dwukrotnie dłuższe testy cykliczne temperatury i mocy

- Ponad trzykrotnie dłuższe testy statyczne w wysokiej temperaturze i napięciu (HTRB, HTGB)

- Kwalifikacja pracy przy maksymalnej temperaturze złącza 200°C (TJMAX), potwierdzająca odporność na przeciążenia

Obudowa HV-T2Pak – kompaktowa i efektywna termicznie

Nowa obudowa HV-T2Pak (14 mm x 18,5 mm) została zoptymalizowana poprzez innowacyjne rowkowanie w materiale obudowy, co pozwala zwiększyć drogę upływu do 6,45 mm bez zmniejszania rozmiaru pola kontaktowego, zapewniając tym samym efektywne odprowadzanie ciepła. Dodatkowo, odsłonięty pad termiczny pokryto powłoką niklowo-fosforową, zamiast powszechnie stosowanej powłoki cynowej, co poprawia planarity powierzchni po lutowaniu oraz zwiększa efektywność i niezawodność połączenia z materiałem interfejsu termicznego (TIM).

Technologia GeneSiC – wyższa wydajność i trwałość

Bazując na ponad 20-letnim doświadczeniu w rozwoju technologii SiC, tranzystory Navitas GeneSiC oferują nawet o 20% niższą rezystancję w stanie przewodzenia przy wysokich temperaturach w porównaniu z konkurencją oraz znakomite parametry przełączania, co przekłada się na minimalne straty mocy w szerokim zakresie pracy. Wszystkie tranzystory GeneSiC SiC MOSFET posiadają najwyżej udokumentowaną odporność na przebicia lawinowe (100% testowane), doskonałą odporność na zwarcia oraz stabilne napięcie progowe ułatwiające równoległe łączenie.

Portfolio HV-T2Pak obejmuje:

- Tranzystory 1200 V o rezystancji od 18 mΩ do 135 mΩ

- Tranzystory 650 V o rezystancji od 20 mΩ do 55 mΩ

Wersje o niższej rezystancji (<15 mΩ) mają zostać zaprezentowane jeszcze w 2025 roku.

Źródło: Navitas Semiconductor