Wraz ze wzrostem liczby szyn zasilających w systemie projektanci muszą wybierać optymalne komponenty dla szyn wysokoprądowych i niskoprądowych. Wielofazowe układy zasilania zapewniają dużą wydajność prądową przy małych gabarytach cewek, a wielowyjściowe pozwalają zasilać kilka szyn FPGA przy wykorzystaniu pojedynczego układu scalonego.

W artykule omówiono wykorzystanie architektury wielowyjściowej w systemach zasilania FPGA na przykładzie dwuwyjściowego modułu MPM54322. Skupiono się na kwestiach regulacji napięcia, prawidłowego rozruchu i bezpiecznego wyłączenia szyn zasilających.

Napięcie tętnienia na liniach zasilania układów FPGA

Nowoczesne układy FPGA wymagają wielu szyn zasilających o różnych napięciach i wydajności prądowej. W zaawansowanych projektach nieraz występuje ich nawet 8, w zależności od cech konkretnych układów, takich jak wewnętrzna pamięć DDR, transceivery o dużej szybkości transmisji i inne bloki peryferyjne. Większość systemów z układami FPGA zawiera magistralę główną 12 V, a napięcia pozostałych szyn zasilających mieszczą się w przedziale od 0,65 do 3,3 V.

Napięcie tętnienia jest jednym z najważniejszych kryteriów przy projektowaniu zasilania do układów FPGA. Jest ono określone na karcie katalogowej producenta, ale ogólnie nie może przekraczać ±3% napięcia znamionowego lub ±30 mV.

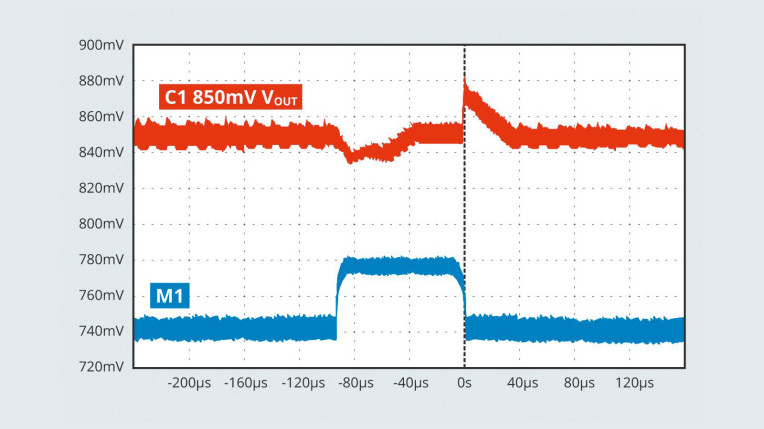

Problemy związane z zapewnieniem odpowiedniej wartości napięcia tętnienia można zademonstrować w teście obciążenia dynamicznego, przeprowadzanym za pomocą MPM54322 – dwuwyjściowego modułu mocy o wydajności prądowej 3 A. Aby lepiej zasymulować zachowanie układu FPGA, szybkie zmiany prądu zostały uzyskane przy wykorzystaniu symulatora obciążenia (load slammer), zdolnego do wytwarzania zboczy o współczynniku slew rate do 130 A/μs.

W teście obciążenia dynamicznego, na jednym z 3-amperowych wyjść układu został wygenerowany skok natężenia prądu od 0 do 1,5 A. Test ten, przeprowadzony przy napięciu wejściowym 12 V i napięciu wyjściowym 0,85 V, ma emulować zachowanie nowoczesnych układów FPGA (rys. 1). Wykazał on niewielkie napięcie szczytowe tętnienia, równe ±22,5 mV dla impulsu o szybkości narastania prądu 130 A/μs. Napięcie to znajduje się w zakresie tolerancji szyny zasilającej FPGA, dzięki sterowaniu w adaptacyjnym trybie constant-on-time (COT). W trybie COT układ zasilania dostarcza wymaganą energię do obciążenia znacznie szybciej niż w tradycyjnym trybie sterowania z kontrolą prądu szczytowego. Dzięki temu stabilne napięcie wyjściowe można zapewnić podczas przełączania, bez potrzeby stosowania dużej pojemności wyjściowej.

Sekwencyjne włączanie napięć podczas rozruchu i w trybie shutdown

Aplikacje z układami FPGA zawierają wiele szyn zasilających, podłączonych do wielu regulatorów napięcia. Podczas rozruchu musi zostać zachowana określona sekwencja ich włączania. Jednak zrealizowanie sekwensera może nie być wykonalne ze względu na małą dostępną przestrzeń na płytce drukowanej. Wielowyjściowe moduły zasilające, takie jak MPM54322, wykorzystują opatentowane przez MPS sterowanie sekwencyjne FLEX-timer, umożliwiające precyzyjne sterowanie czasami włączania i wyłączania wszystkich regulatorów napięcia, bez potrzeby korzystania z sekwensera.

Zapewnienie właściwego działania układu miękkiego startu

Faza rozruchu, krytyczna dla układów FPGA, zapewnia ich poprawną inicjalizację i minimalizuje ryzyko uszkodzeń. Właściwe czasy narastania sygnałów zasilających zapewniają regulatory napięcia. Ich kontrola jest szczególnie ważna w układach FPGA ze względu na to, że stanowią one duże obciążenia pojemnościowe. Bez zaimplementowanej funkcji miękkiego startu natężenie prądu rozruchowego mogłoby powodować znaczne fluktuacje napięcia na wejściu i uszkodzenie FPGA lub innych komponentów.

Większość producentów układów FPGA ustala czas działania funkcji miękkiego startu (tSS) na około 10 ms. Zapewniając liniowy wzrost napięcia zasilania w czasie tSS, ogranicza się natężenie prądu rozruchowego i „wygładza” sekwencję startową. Niespełnienie wymogów odnośnie do miękkiego startu może doprowadzić do niemonotonicznej sekwencji startowej lub nawet uszkodzenia układu FPGA.

Do uzyskania niezawodnej pracy systemu kluczowe jest wybranie regulatorów napięcia o czasie trwania fazy miękkiego startu, określonym przez konkretnych producentów układów FPGA. Moduły, takie jak MPM54322, umożliwiają precyzyjne dopasowywanie czasu tSS do wymogów układu FPGA i systemu zasilania. Zakres regulacji w jego przypadku wynosi od 1 ms do 14 ms (rys. 2).

Opatentowany przez MPS schemat kontroli sekwencji rozruchowej FLEX-timer

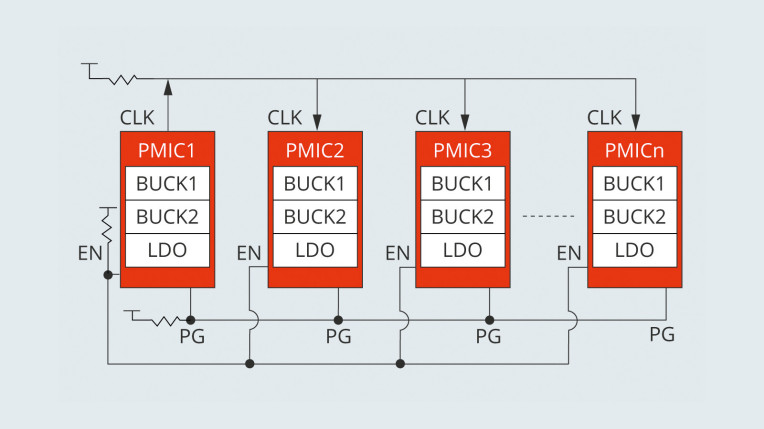

MPM54322 wykorzystuje sekwencyjne sterowanie FLEX-timer do kontroli kolejności inicjowania szyn zasilających. Ten schemat sterowania wykorzystuje strukturę master-slave, w której sygnały sterujące wszystkich układów zarządzania zasilaniem (PMIC) są ze sobą połączone (rys. 3). Jeden z układów PMIC, skonfigurowany jako master, generuje sygnał zegara, natomiast pozostałe, skonfigurowane jako układy slave, odbierają ten sygnał. Sekwencje uruchamiania i wyłączania wszystkich szyn zasilania są synchronizowane.

Po podaniu sygnału sterującego sekwencja rozruchu rozpoczyna się od wygenerowania przez główny PMIC impulsów zegarowych, podawanych do zliczających je, podrzędnych układów PMIC. Każda szyna zasilania włącza się, gdy zostanie osiągnięte określone opóźnienie. Sygnał statusu sygnalizuje zakończenie sekwencji dla wszystkich szyn i powoduje deaktywowanie wyjścia zegarowego głównego układu PMIC.

Podczas przełączania w tryb shutdown, przy braku sygnału sterującego, główny układ PMIC rozpoczyna generowanie impulsów, zliczanych przez podrzędne układy PMIC. Po osiągnięciu określonych czasów opóźnienia poszczególne szyny są wyłączane. Sekwencja kończy się po wyłączeniu ostatniej szyny i deaktywowaniu wyjścia zegarowego nadrzędnego układu PMIC.

Ten schemat sterowania sekwencyjnego zapewnia zsynchronizowany i skoordynowany proces uruchamiania i wyłączania wielu szyn zasilających, zarządzanych przez kilka układów PMIC bez konieczności wprowadzania dodatkowego sekwensera.

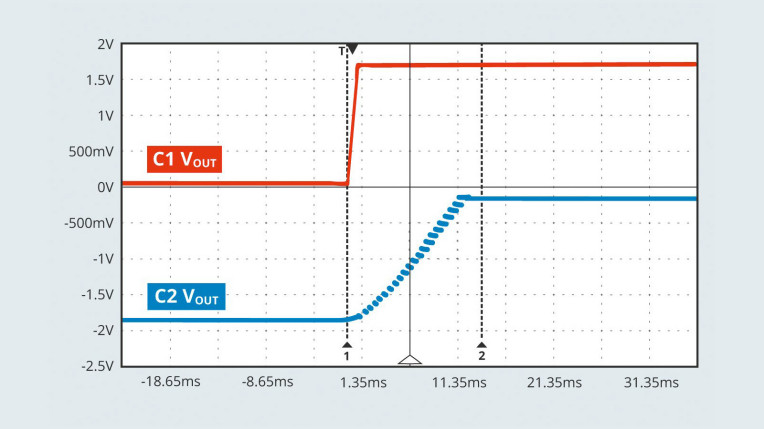

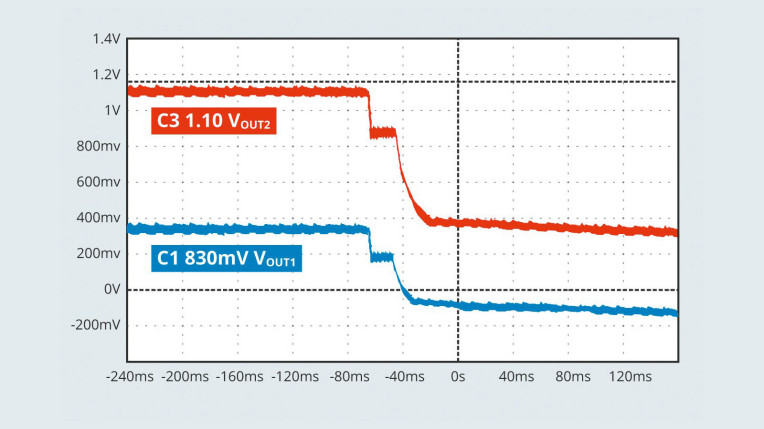

Bezpieczne przejście w tryb shutdown za pomocą aktywnego rozładowania

Przepięcia na liniach VOUT mogą uszkodzić układ FPGA. Gdy obciążenie zostanie nagle odłączone, energia zgromadzona w kondensatorach wyjściowych może spowodować pojawienie się dużych impulsów przepięciowych. Aby zapobiec tej sytuacji, w MPM54322 zaimplementowano funkcję aktywnego rozładowania, zapewniającą szybkie rozładowanie pojemności wyjściowej układu PMIC po wyłączeniu zasilania lub nagłym odłączeniu obciążenia. Aktywne rozładowanie jest przeprowadzane, gdy układ jest wyłączony, a napięcia wewnętrznych przetworników C/ A zmniejszają się. Gdy na ich wyjściach zostaną osiągnięte wartości 850 mV i 650 mV, procedura soft shutdown zostaje zakończona. Następnie pojemności ulegają dalszemu rozładowaniu przez rezystory sprzężenia zwrotnego. Na rysunku 4 przedstawiono sekwencję shutdown układu MPM54322.

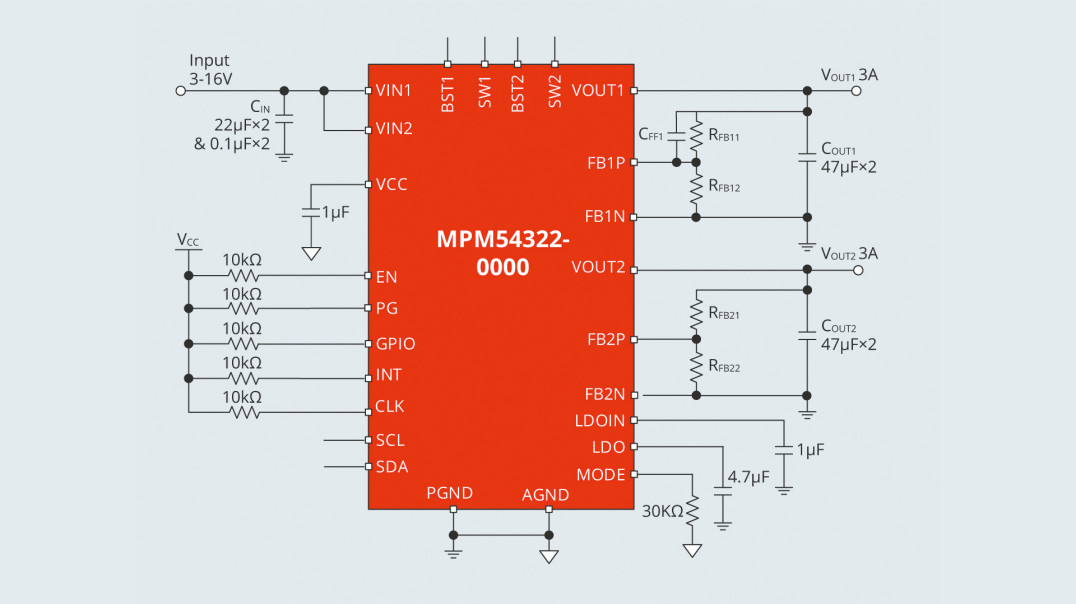

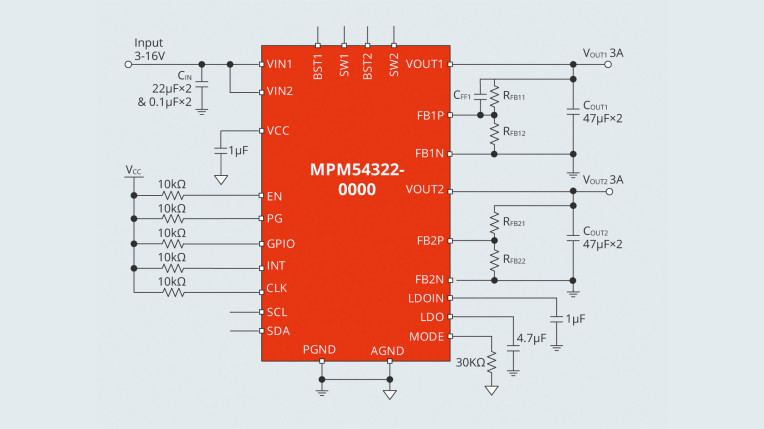

Dwuwyjściowy układ zasilający MPM54322

Firma MPS oferuje wiele elastycznych i skalowalnych modułów zasilających. MPM54322 to wersja dwuwyjściowa o wydajności prądowej 3 A, zawierająca dwa wewnętrzne konwertery DC-DC step-down o dużej sprawności, regulator LDO i komplet elementów pasywnych, w tym dwie cewki do konwerterów DC- DC. Wyjścia MPM54322 mogą pracować niezależnie od siebie, zasilając dwa oddzielne układy FPGA, jak również mogą być łączone w pojedyncze wyjście o wydajności prądowej 6 A. Na rysunku 5 przedstawiono typowy schemat aplikacyjny MPM54322.

Aplikacje FPGA mogą zawierać wiele szyn zasilających, w tym również do systemów zewnętrznych. Te same moduły wielowyjściowe mogą być wykorzystywane do realizowania sekwencji startowych również innych podsystemów. Poszczególne wersje układów zasilających o różnych wartościach zaprogramowanych fabrycznie napięć i prądów często różnią się jedynie sufiksem w oznaczeniu, co może prowadzić do pomyłek podczas produkcji i konfiguracji, stwarzając ryzyko uszkodzenia układów FPGA. Aby rozwiązać ten problem, w MPM54322 dostępna jest wewnętrzna pamięć MTP, pozwalająca przełączać do 10 różnych zestawów parametrów zasilania za pomocą rezystora na wejściu konfiguracyjnym.

Codico Poland

CODICO Poland

tel. 12 4171083 w. 21

www.codico.com