Testowanie płytek zawierających zaawansowaną elektronikę odbywa się na odpowiednio zaprojektowanych stanowiskach pomiarowych umożliwiających automatyzację tego procesu. Istotnym ich wyposażeniem są sondy pomiarowe umożliwiające dostęp do wielu punktów pomiarowych. Nietrudno zauważyć, że zagęszczanie elektroniki na płytce obwodu drukowanego nie ułatwia dołączania sond do wybranych punktów układu. Zresztą nie tylko samo zagęszczenie jest problemem, także coraz mniejsze wymiary elementów często wręcz uniemożliwiają dołączanie sond do punktów testowych. A trzeba tu zaznaczyć, że testowanie urządzeń elektronicznych polega nie tylko na pomiarach elektrycznych, ale również na inspekcji wizualnej mającej na celu m.in. lokalizację uszkodzeń mechanicznych powstałych podczas montażu. Nie jest to niestety koniec problemów. Utrudnieniem staje się także nierzadko stosowany obustronny montaż elementów na PCB.

Nieco inną kwestią jest programowanie układów. Często na jednej płytce znajduje się szereg układów wymagających programowania. Są to na przykład programowalne układy logiczne (PLD), układy FPGA, mikrokontrolery, pamięci Flash, EEPROM itp. Mogą one wymagać wielu programatorów i programów przeznaczonych wyłącznie do układów określonego typu.

Testowanie układów elektronicznych to bardzo ciekawa dziedzina, której warto przyjrzeć się bliżej. Może być ono realizowane wieloma metodami i technikami, wśród których szczególne znaczenie ma powszechnie już stosowane testowanie graniczne – boundary scan. Technika ta umożliwia sprawdzanie wzajemnych połączeń i wypełnianie funkcji urządzenia po zakończonym montażu elementów na płytkach drukowanych.

Zagadnienie nie jest proste. Testowanie elektryczne zmontowanych płytek w środowisku produkcyjnym na wielką skalę wymaga znacznych zasobów inżynieryjnych. Konieczne jest zebranie, a często również opracowanie, odpowiedniego osprzętu i oprogramowania. W nowoczesnych układach scalonych charakteryzujących się dużą złożonością i gęstością upakowania stosowane są magistrale umożliwiające dostęp do liczonych nawet w tysiące węzłów testowych. Dzięki temu możliwa jest ocena poprawności działania urządzenia w zakresie realizowanych funkcji, a także integralności połączeń wewnętrznych. Dostęp do takiej sieci jest uzyskiwany przez złącze krawędziowe pytki lub bezpośrednio przez dołączenie sondy do końcówek układu półprzewodnikowego znajdującego się na płytce. Jest to bardzo dokładna technika testowa, umożliwiająca zarówno testowanie komponentów wewnętrznych płytki, jak i całego systemu. Wdrożenie boundary scan eliminuje potrzebę stosowania tradycyjnego wymogu ICT ("jeden węzeł na sieć"). Urządzenie musi mieć jednak zaimplementowaną funkcję autotestu.

Test JTAG według normy IEEE 1149.1

Nie ma chyba elektronika, który nie zetknąłby się z akronimem JTAG. Jego rozwinięcie to Joint Test Action Group, co można przetłumaczyć jako zespół specjalistów w dziedzinie inżynierii testów. To oni opracowali standardową procedurę weryfikacji projektów i testowania złożonych zespołów płytek drukowanych. Zagadnienie z zasady nie jest proste. Przed rozpoczęciem testów konieczne są pewne zabiegi przygotowawcze, do których należy m.in. opracowanie specjalnych programów testowych. Niestety, nie są to programy uniwersalne i muszą być pisane dla każdego konkretnego przypadku. Mimo to, technika ta znajduje ekonomiczne uzasadnienie i jest już powszechnie stosowana.

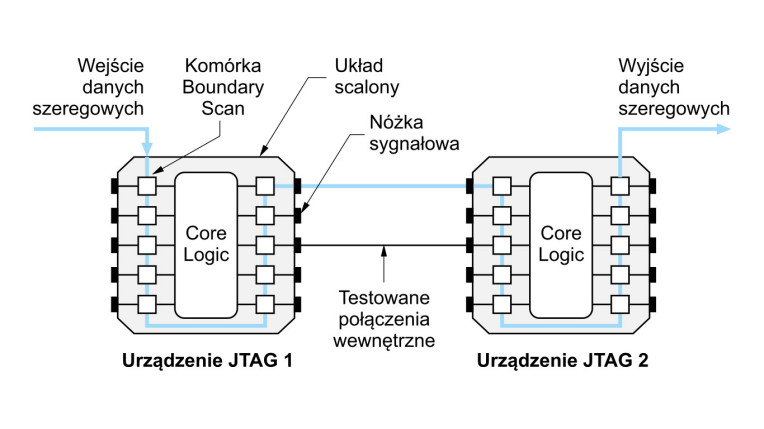

Architektura boundary scan zapewnia testowanie płytek drukowanych z wielonóżkowymi układami logicznymi dużej skali integracji poprzez przechwytywanie danych funkcjonalnych w czasie normalnej pracy urządzenia. Komórki boundary scan wbudowane w każde urządzenie przechwytują dane z sygnałów logicznych. Są one następnie przesuwane szeregowo i porównywane zewnętrznie z przewidywanymi wynikami (rys. 1).

Jedną z zalet testowania techniką boundary scan jest możliwość wykrywania uszkodzeń nawet wewnątrz półprzewodnikowej struktury układu scalonego, jeśli tylko jest on skonfigurowany w układzie macierzowym. Ponadto, choć może wydawać się to dość zaskakujące, testowanie może być prowadzone bez konieczności fizycznego dostępu do wszystkich węzłów na płytce drukowanej. W typowym teście boundary scan tester wysyła sygnały diagnostyczne do styku wejściowego urządzenia. Komórki boundary scan przechwytują sygnały i przesuwają je przez logikę rdzenia. Sygnał wyjściowy jest następnie szeregowo przesuwany z rdzenia poprzez pin wyjściowy danych.

Wymagania dotyczące dostępu do węzła testowego

Jak już wspomniano wcześniej, jedną z operacji testowania techniką boundary scan jest przesuwanie danych. Jest ona realizowana z użyciem rejestru przesuwającego, który musi być wbudowany w każde połączenie zewnętrzne wszystkich urządzeń zgodnych z techniką boundary scan. Jedna komórka boundary scan znajduje się w układzie scalonym na linii we/wy lub na innym wyprowadzeniu, i gdy jest używana w trybie rejestru przesuwającego, może przesyłać dane do następnej komórki w urządzeniu. Istnieją określone punkty wejścia i wyjścia danych wchodzących i wychodzących do/z urządzenia, dlatego możliwe jest progresywnego łączenie ze sobą kilku urządzeń.

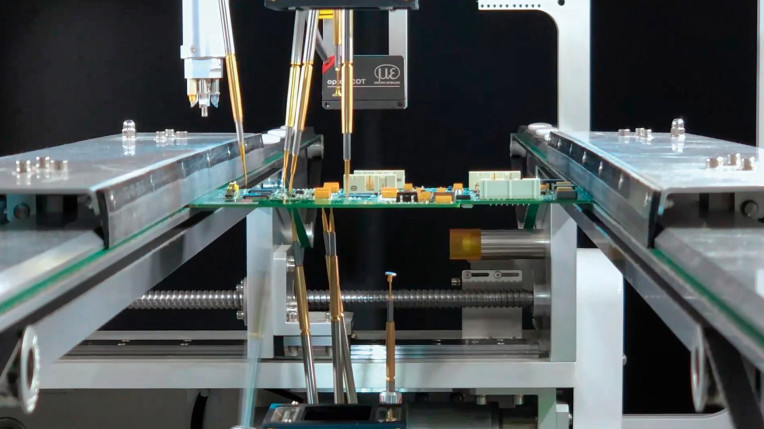

Typowy sprzęt testowy opracowany przez JTAG Technologies (rys. 2) zapewnia maksymalną elastyczność i niezależność. Tester może być skonfigurowany jako samodzielna stacja boundary scan, zintegrowana lub połączona z testem funkcjonalnym i testem w obwodzie (ICT – In Circuit Test) lub podczas korzystania z testerów FPT (Flying Probe Testers).

Testowy port dostępu jest utworzony z kilku linii sterujących i linii danych. Linie sterujące pełnią funkcje zegara i wyboru trybu testu. Jest także opcjonalna linia zerowania testu. Linie są dołączone równolegle do układu scalonego, tworząc łańcuch boundary scan. Sygnały prowadzące do wejścia i wychodzące z wyjścia danych testowych są połączone łańcuchowo, aby zapewnić ścieżkę obejmującą urządzenia boundary scan. Dane funkcjonalne są przesyłane do węzła wejściowego danych testowych pierwszego układu scalonego. Wyjście z pierwszego urządzenia jest następnie dołączane do wejścia danych testowych następnego urządzenia (urządzeń) itd.

Korzyści wynikające z wdrożenia boundary scan to:

- Przyspieszenie uruchamiania i rozwijania nowych produktów

- Skrócenie czasu wprowadzenia produktu na rynek

- Szybkie i wydajne generowanie programu testowego

- Urządzenia takie są idealne do płyt poddawanych rewizjom projektu.

Jedną z ważniejszych zalet procedur testowych JTAG jest to, że mogą być używane w całym procesie produkcyjnym płytki drukowanej, wliczając w to weryfikację projektu, programowanie w systemie, testowanie i debugowanie. Testowanie boundary scan opiera się na wbudowanych funkcjach testowania komponentów, do których dostęp jest uzyskiwany poprzez cztery do sześciu wyprowadzeń układów scalonych. Pozwalają one na przeprowadzenie pełnej analizy działania urządzenia. Wykrywanie usterek jest możliwe dzięki specjalnej logice testowej, która jest zaimplementowania w elementach montowanych na PCB oprócz zwykłych funkcji użytkowych, i odpowiada za skanowanie układów poprzez szeregowy interfejs JTAG.

Skanowanie graniczne płytek, szczególnie tych, które odznaczają się dużym stopniem złożoności, może być prowadzone z użyciem narzędzi X-JTAG, które współpracują z różnymi dostawcami rozwiązań testowych obejmujących m.in. latające sondy. Umożliwiają one dostęp do wielu punktów testowych na płytce drukowanej, na której mogą znajdować się nawet układy w obudowach BGA (Ball Grid Array) – rysunku 3. Dzięki nim użytkownik osiąga największe korzyści testowe, a więc maksymalny zasięg testów przy minimalnym czasie testowania.

Przekazanie dokumentacji do testu montażowego

Test montażowy płytki drukowanej prowadzony techniką boundary scan wymaga opracowania odpowiedniej dokumentacji. W ogólnym przypadku nie jest to zadanie proste i zwykle jest powierzane inżynierowi doskonale znającemu zarówno zagadnienia sprzętowe, jak i programowe. Jego zadaniem jest dostarczenie plików zawierających wzorce testowe opracowane na podstawie dostarczonej mu listy połączeń. Test umożliwia sprawdzenie wszystkich komponentów zawartych w badanym obwodzie. W rezultacie wykrywane i wydzielane są wszelkie usterki we wszystkich sieciach obwodu, które mogą być testowane techniką boundary scan. Co więcej, możliwe jest ponadto utworzenie wektorów testowych wykrywających usterki w węzłach lub na nóżkach układu scalonego dla komponentów skanowania niebędących granicami, ale otoczonych urządzeniami testowanymi techniką boundary scan. Wymagania dla poszczególnych przypadków mogą się różnić, jednak większość dokumentów wymaganych do skonfigurowania testu jest dość typowa i obejmuje:

- Szczegóły montażu: Są to grafiki przedstawiające zarys komponentów, lokalizację i oznaczenia referencyjne dla każdego układu zamontowanego na płytce

- Schemat elektryczny: Przedstawia szczegóły połączeń między wszystkimi pasywnymi i aktywnymi elementami zamontowanymi na płytce z odpowiednimi oznaczeniami referencyjnymi

- Szczegóły produkcji płytki drukowanej: Obejmują główne wymiary mechaniczne, lokalizacje narzędzi, materiały wyszczególnione do produkcji, kolejność warstw z reprezentatywnymi szczegółami przekroju poprzecznego

- Plik CAD: dane cyfrowe opisujące rozmieszczenie elementów na płytce oraz wzajemne połączenia obwodów. Zawierają one określone współrzędne X-Y komponentów, ich orientację i funkcje umożliwiające dostęp do sondy testowej

- Plik Gerber: Plik Gerber to standardowy plik opracowany do przechowywania danych projektowych płytki drukowanej lub przesyłania obrazu każdej warstwy PCB. Zawiera ponadto maskę lutowniczą

- Zestawienie materiałów: Wszystkie komponenty są wymienione według typu, wartości i/lub numeru identyfikacyjnego części oraz ilości. W przypadku dwustronnego montażu SMT typy elementów należy rozdzielić i zidentyfikować na podstawie lokalizacji

- Lista zatwierdzonych dostawców: Lista dostawców reprezentuje "kwalifikowanych dostawców" użytkownika w zakresie wszystkich materiałów i elementów przeznaczonych do montażu płytki drukowanej

- Lista połączeń: Identyfikuje połączenia elektryczne (węzły) pomiędzy końcówkami elementów w układzie. Lista zawiera oznaczenia referencyjne elementów, typ elementu i numery wyprowadzeń

- Współrzędne X-Y węzła testowego: Konkretna lokalizacja każdego węzła zidentyfikowanego w liście połączeń musi być odniesiona do pojedynczej docelowej cechy referencyjnej, naniesionej chemicznie na elemencie.

Oprócz wyżej wymienionej dokumentacji projektant płytki drukowanej powinien przedstawić wymagania związane z oczekiwanym działaniem lub środowiskiem użytkowania wyrobu końcowego oraz wyszczególnić kluczowe dane dla wszystkich niestandardowych układów montowanych na PCB.

Zgodność z testami boundary scan

Przed przekazaniem płytki do produkcji projektant wraz z inżynierem odpowiedzialnym za nią, jeśli jest to inna osoba, powinni przedyskutować z autorem programu testowego wszystkie zagadnienia techniczne, aby upewnić się, że produkt końcowy będzie testowany skutecznie. Jeśli nie zostanie zapewniony pełny dostęp sond do wszystkich węzłów sieci lub końcówek boundary scan, osoba odpowiedzialna za test prawdopodobnie poprosi o dodanie wszelkich możliwych zasobów, które zapewniłyby skuteczne testowanie całości. To nie zawsze będzie proste zadanie, może być na przykład konieczna zmiana PCB tak, aby stworzyć dostęp sond do węzłów sieci połączeń. W ogólnym rozrachunku nie powinno to wpłynąć na cenę fabrycznej produkcji płytki drukowanej, zapewni natomiast 100-procentową testowalność PCB.

Jarosław Doliński Opr. na podstawie "Design for Test", Vern Solberg, "Design Magazine"