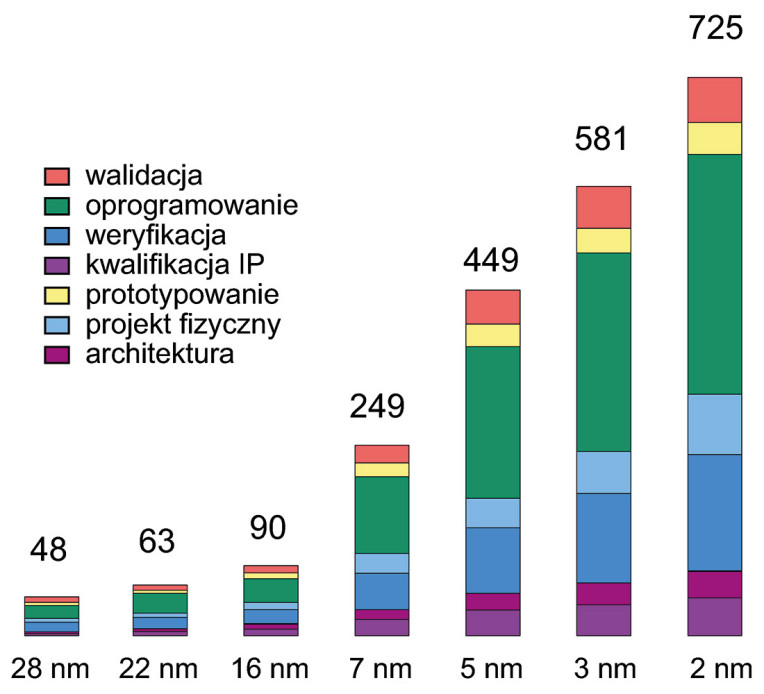

Dane pokazują, że w procesie 7 nm koszt zaprojektowania układu scalonego osiągnął już 249 mln dolarów, podczas gdy przy 16 nm było to zaledwie 89,8 mln. W przypadku 5 nm wydatki wzrosły do 449 mln, przy 3 nm do 581 mln, a dla 2 nm prognozuje się już 750 mln dolarów. I jest to prognoza bardzo optymistyczna. Jeśli tempo wzrostu się utrzyma, granica miliarda dolarów na projekt zostanie przekroczona już niedługo.

Tak duże koszty wynikają z relacji panujących w całym łańcuchu produkcyjnym chipów. Podstawowe działania obejmują projektowanie, produkcję, pakowanie i testowanie, a elementy powiązane to między innymi bloki IP, narzędzia EDA, sprzęt oraz materiały. Do głównych źródeł wydatków należą koszty pracy i badań, opłaty za tape-out, licencje na zewnętrzny IP i narzędzia EDA, a także inwestycje w fabryki, produkcję krążków krzemowych oraz zakup wyspecjalizowanego sprzętu.

To, że nowoczesna architektura scalona jest droższa od przestarzałej nie, powinno stanowić dla nikogo żadnego zaskoczenia. Struktura kosztów wskazuje jednak, że największym obciążeniem jest oprogramowanie, a następnie weryfikacja, walidacja i dopiero projekt fizyczny chipa. Akurat ten element wydaje się nieco niespodziewany, szczególnie na pierwszy rzut oka.

Sztuczna inteligencja to sposób na obniżenie kosztów?

Około 750 mln dolarów to scenariusz realny, ale być może najgorszy z możliwych. Istnieje spora szansa, że sztuczna inteligencja już wkrótce znacząco obniży wydatki na oprogramowanie oraz weryfikację – dwa najdroższe elementy środowiska projektowania chipów. To dlatego, że projektowanie generatywne wspierane przez sztuczną inteligencję pozwala w dużej mierze zautomatyzować proces tworzenia układów scalonych oraz podsystemów elektronicznych. Wystarczy odpowiedni zestaw parametrów i ograniczeń, aby algorytmy samodzielnie opracowały rozwiązanie, bez konieczności angażowania dużych zasobów inżynierskich.

Dobrym przykładem są też dostępni już asystenci inżynierscy oparci na generatywnej AI, którzy umożliwiają korzystanie z narzędzi projektowych w języku naturalnym. Dzięki temu początkujący inżynierowie mogą pracować nawet dwa razy szybciej i efektywniej oraz szybciej się uczą. Z kolei w obszarze dokumentacji sztuczna inteligencja znacząco skraca czas opracowywania kart katalogowych, instrukcji technicznych czy materiałów dopasowanych do konkretnych grup odbiorców i rynków. Ciekawa wydaje się również możliwość wykorzystania AI jako narzędzia badawczego. Systemy te potrafią dostarczać inżynierom rekomendacje w odpowiednim kontekście, wspierać analizę problemów i przyspieszać znajdowanie kluczowych rozwiązań. W efekcie zespoły zyskują nie tylko na produktywności, ale także szybciej reagują na wyzwania projektowe i badawcze.

Kluczowy jest jednak chłodny optymizm. Narzędzia EDA do automatyzacji produkcji elektroniki są obecne na rynku od wielu dekad. Co prawda obecny rozwój komercyjnych i otwartoźródłowych modeli językowych (LLM) otwiera nowe możliwości automatyzacji takich zadań w procesach front-end, back-end i testach produkcyjnych, ale czy naprawdę będzie to rewolucja, która powstrzyma wykładniczy wzrost kosztów? Teoretycznie oznacza to możliwość przyspieszenia pracy inżynierów poprzez automatyczne generowanie kodu. W praktyce opłaty licencyjne i konieczność weryfikacji mogą jeszcze przez wiele lat generować podobne koszty. Scenariusz jest co prawda optymistyczny, ale warto spojrzeć na niego nieco krytycznie.

TSMC dyktuje ceny

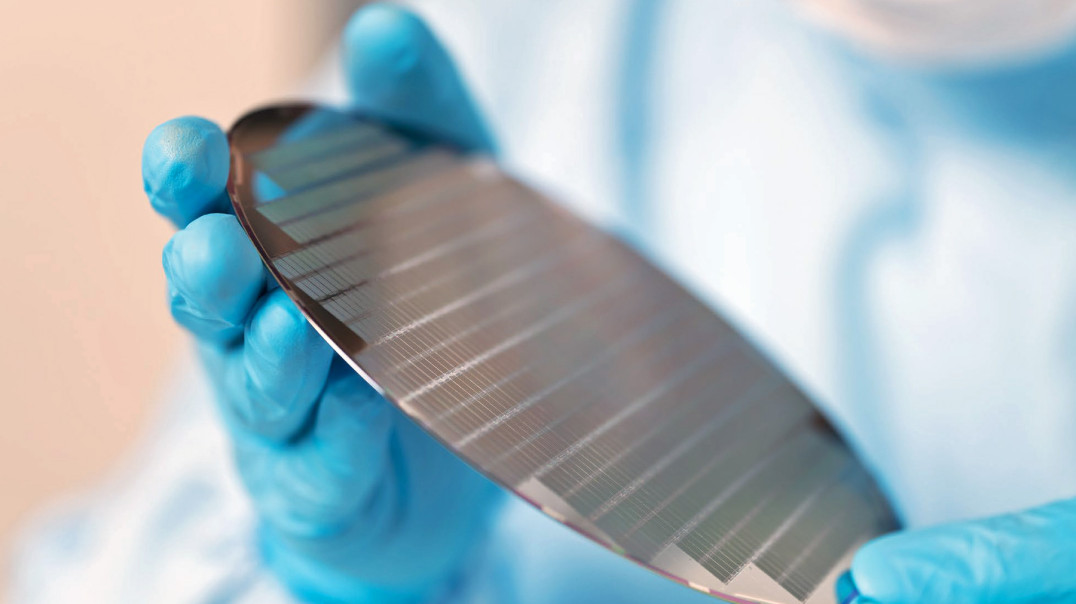

Niestety, nie tylko oprogramowanie stanowi barierę cenową w produkcji najnowszych chipów. Same fabryki stanowią coraz większy koszt. Zgodnie z danymi CEST, produkcja pojedynczego krążka krzemowego o średnicy 300 mm w procesie 5 nm kosztuje około 17 tys. dolarów. Dla porównania, podobny wafel wytworzony w technologii 7 nm to koszt rzędu 9400 dolarów. Oznacza to, że przy tej samej wielkości krzemu cena produkcji w procesie 5 nm jest wyższa o ponad 7000 dolarów względem wersji 7 nm. Według doniesień krążki w technologii 2 nm od TSMC mają kosztować za to około 30 tys. za sztukę. To znaczący wzrost względem obecnych układów 3 nm i jednocześnie nowy punkt odniesienia dla największych firm technologicznych.

Mimo zaporowej ceny, takie firmy jak Apple, AMD, Nvidia czy Qualcomm, prawdopodobnie jeszcze w tym roku złożą zamówienia, lub już złożyły, na chipy w procesie 2 nm. Apple ma mieć nawet priorytetowy dostęp do technologii, aby wykorzystać ją w procesorze A20, przeznaczonym do przyszłorocznego iPhone’a 18 Pro. Popyt nie jest przypadkowy – chodzi o kluczowe wzrosty wydajności niezbędne w produktach nowej generacji i brak realnych alternatyw w tej skali produkcji. Dodatkowo testy pamięci 256 Mb SRAM na procesie N2 wykazały 90% uzysk, co sugeruje gotowość technologiczną do masowej produkcji jeszcze w tym roku.

Tak wysoka cena odzwierciedla ogromne nakłady kapitałowe na nowe fabryki i wprowadzanie coraz bardziej złożonych architektur tranzystorów. TSMC w 2 nm po raz pierwszy zastosuje tranzystory typu gate-all-around (GAA), które mają lepiej radzić sobie z prądem upływu. Kolejne kroki są już w planach – procesy takie jak A16 (1,6 nm) wprowadzą m.in. zasilanie od strony tylnej (backside power delivery). Według doniesień ceny w tych przyszłych technologiach mogą sięgać nawet 45 tys. dolarów za jeden krążek.

Taka sytuacja mocno wpływa na cały łańcuch dostaw elektroniki. TSMC ma dominującą pozycję, więc ich polityka cenowa bezpośrednio przekłada się na koszt materiałów i finalną cenę praktycznie wszystkich układów wysokiej wydajności. Owszem, Intel rozwija własną strategię z procesem 18A (również opartym na GAA i zasilaniu od strony tylnej), ale rynek wciąż w dużej mierze zależy od mocy produkcyjnych TSMC. Ta zależność, w połączeniu z rosnącą ceną podłoży krzemowych, w praktyce kształtuje zarówno decyzje projektowe, jak i strategie zakupowe firm działających na granicy możliwości współczesnej technologii krzemowej. Konsensus wydaje się jasny – chipy będą coraz droższe, ale istnieje spora szansa, że wzrost nie będzie wcale aż tak dramatyczny, jak zakładano jeszcze kilka lat temu.