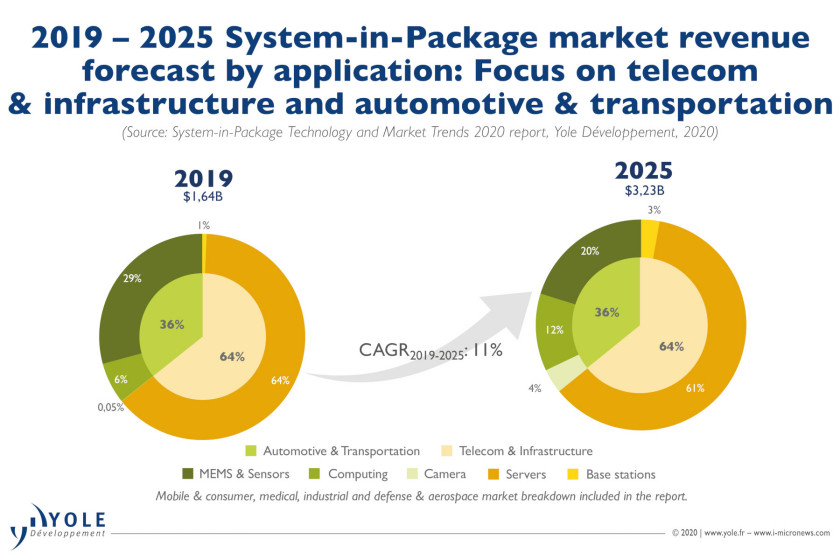

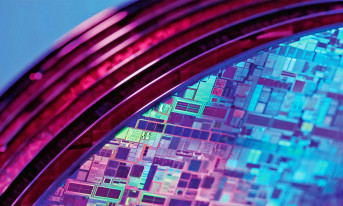

- W ciągu następnych pięciu lat elektronika do noszenia, routery Wi-Fi i Internet Rzeczy będą generowały znaczny wzrost rynku SiP. Głównym motorem wzrostu będą technologie 5G i czujniki. Pomimo tego, że rynek telefonów komórkowych, a zwłaszcza smartfonów jest już nasycony, pojawiają się nowe możliwości stosowania SiP ze względu na wymagania, jakie niesie za sobą technologia 5G - powiedział Favier Shoo z Yole Developpement.

W segmencie stacji bazowych, serwerów i telekomunikacji oczekuje się wzrostu charakteryzującego się dwucyfrowym CAGR-em, przy czym dla stacji bazowych wyniesie on aż 41%. Motorem wzrostu w tym segmencie będą stacje bazowe 5G, w których wykorzystuje się coraz więcej układów SiP zamykanych metodą flip-chip (FC) w formie BGA. Ponadto serwery zawierają wysokiej klasy chipy SiP, takie jak CPU, PU (chiplety, interposer Si, FO) i FPGA.

W sektorze motoryzacji i transportu głównymi czynnikami wzrostu są systemy informacyjno-rozrywkowe i ADAS. Mimo, że kamery stanowią niewielką część tego sektora, jednak osiągają znaczący wzrost. Większości systemów informacyjno-rozrywkowych i VPU stanowią układy MEMS i czujniki, na które składają się aplikacje takie, jak pomiar ciśnienia, IMU, optyczne MEMS, mikrobolometry, oscylatory i czujniki środowiskowe. Udział układów w obudowach SiP na rynkach medycznych, przemysłu obronnego i lotniczego jest znacznie mniejszy, jednak w robotyce i aplikacjach IoT charakteryzuje się silnym wzrostem.

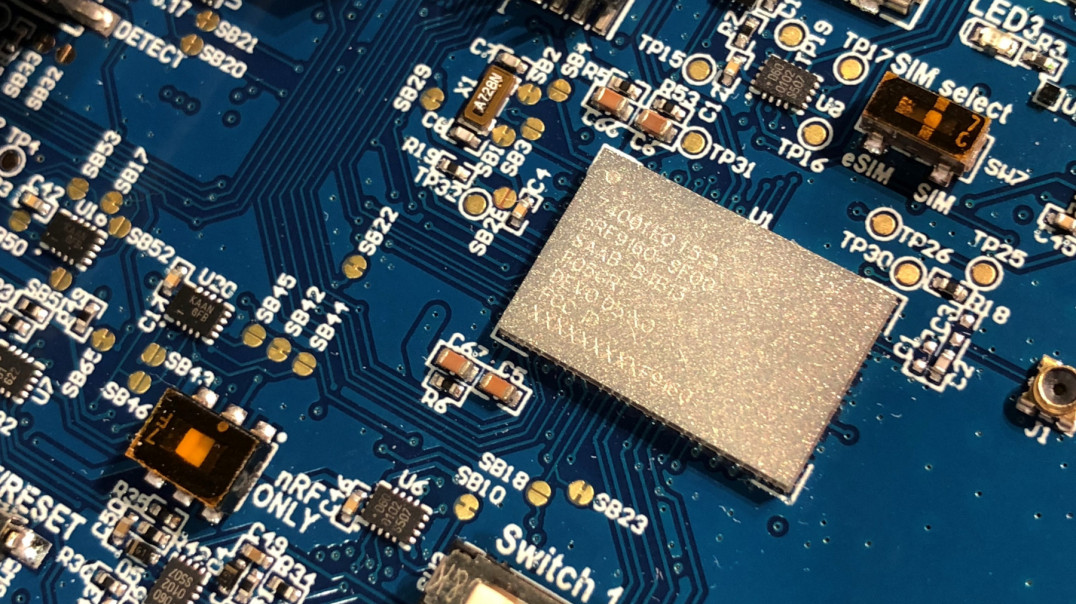

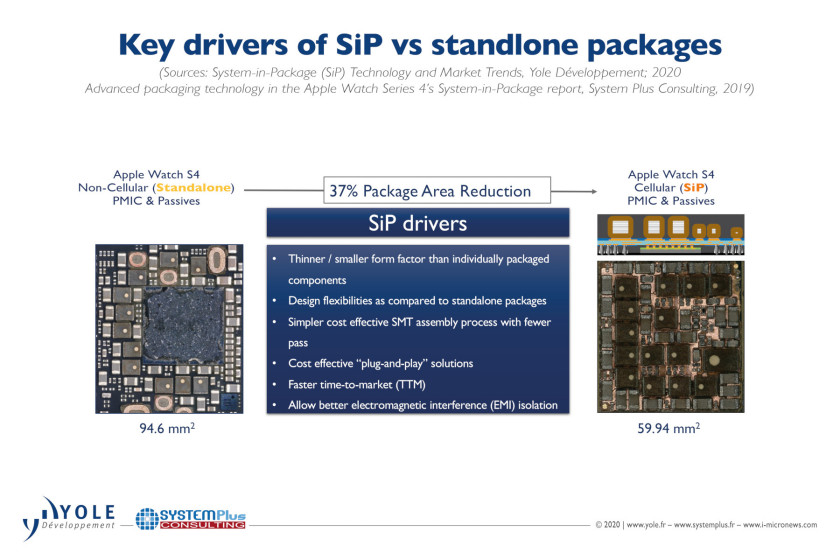

Do zalet układów SiP należą mniejsze wymiary, zwiększona wydajność i integracja funkcjonalna chipu z izolacją zakłóceń EMI, elastyczność projektowania w porównaniu do samodzielnych układów SoC, a także niższy koszt. W związku występującym ostatnio wzrostem popytu na układy w obudowach SiP wysokiej klasy i o większych rozmiarach, producenci uruchomili wiele inwestycji w procesy technologiczne flip-chip i wire-bond (WB).

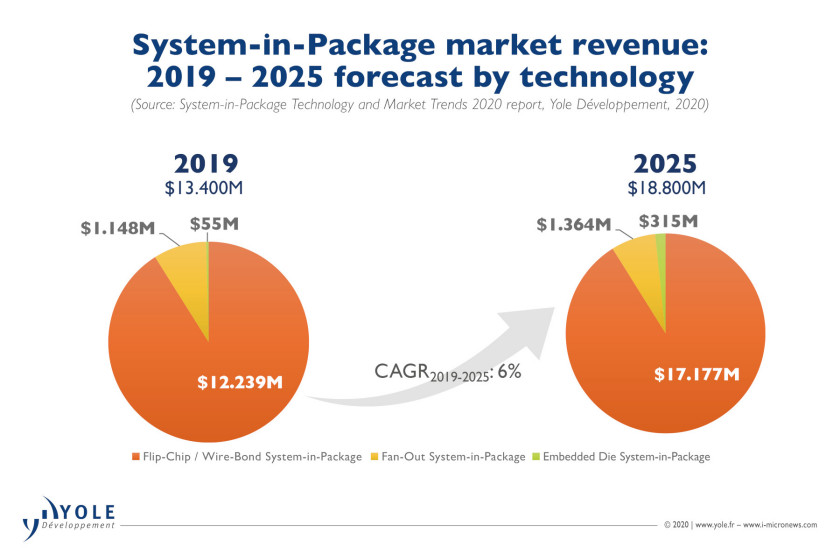

Wartość rynku układów SiP w technologii FC i WB wynosi 12,2 mld dolarów, co stanowi ponad 90% przychodów z zamykania struktur w obudowach SiP. Oczekuje się, że do 2025 roku wartość ta osiągnie 17,1 mld dolarów.

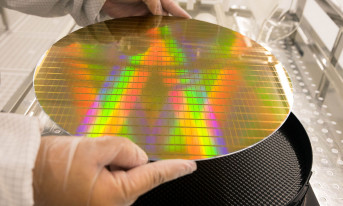

Takie metody, jak FC i WB zajmują czołowe miejsca w produkcji chipów w obudowach SiP, zarówno do zastosowań nisko-, jak i wysokowydajnych, a także generują nowe możliwości w łańcuchu dostaw. Opakowania FO pojawiły się jako jedna z głównych metod pakowania półprzewodników w obudowach SiP. Potencjał technologii FO jest jednak nadal dość ograniczony z powodu problemów związanych z kosztami produkcji w przypadku większej ilości płytek. W rezultacie firmy, które zajmują się badaniami i produkcją chipów metodą FO w obudowach SiP są już graczami o dużej wiedzy i dojrzałości produkcyjnej. Od 2017 roku rynek ten jest zdominowany przez firmę TSMC, której udział w zamykaniu struktur metodą FO od roku 2019 przekracza 90%.

W okresie prognozy, czyli w latach 2019-2025, wzrost wykorzystania technologii ED SiP wyniesie około 27%, podczas gdy przychody z opakowań ED SiP przekroczą do 2025 roku wartość 310 mln dolarów. Takie kategorie, jak motoryzacja, telekomunikacja i telefony komórkowe będą odpowiadały za większość tych przychodów. Pomimo, że przychody z technologii ED SiP są bardzo małe, ich tempo wzrostu jest bardzo wysokie.

Źródło: Electronics Weekly, Yole