Wymagania i wiążące się z nimi normy je definiujące formalnie często można spełnić jedynie poprzez wprowadzenie dodatkowego procesu mycia w procesie produkcji. W artykule opisano wymagania dotyczące czystości powierzchni elementów przed powlekaniem oraz przedstawiono szybkie i opłacalne metody badań i analizy poziomu czystości. Ponadto zaprezentowano przegląd różnych sposobów mycia płytek drukowanych, spełniających takie wymagania.

Najważniejsze jest to, że nakładane powłoki muszą idealnie przylegać na podzespołach elektronicznych, aby zagwarantować ich optymalną pracę nawet w ekstremalnych warunkach środowiskowych, takich jak duże zmiany temperatury i wilgoć, które zwiększają ryzyko usterek. Główną ich przyczyną są prądy upływu i migracja elektrochemiczna. Jest to wynik tego, że wraz z wprowadzeniem bezołowiowych past lutowniczych w pozostałościach po lutowaniu pojawiło się więcej cząsteczek stałych wymieszanych z agresywnymi chemicznie aktywatorami. Odpowiadają one za wzrost degradacji połączeń, a więc awarie oraz zmniejszenie niezawodności i żywotności elementów elektronicznych.

Dodatkowa powłoka jako niezawodny środek ochronny

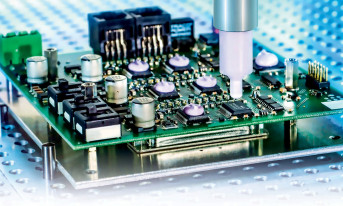

Zabezpieczenie elementów elektronicznych w powłoki ochronne jest ważnym i niezbędnym środkiem zapewniającym niezawodność produktów elektronicznych. Ponieważ powlekanie elementów elektronicznych jest na ogół ostatnim etapem procesu produkcyjnego, błędy na tym etapie mogą mieć drastyczny wpływ na koszty produkcji i na powstawanie awarii. Aby zapewnić optymalną przyczepność powłoki ochronnej i zapobiec późniejszemu powstawaniu pęknięć i rozwarstwianiu się, ważne jest, aby zapewnić najwyższą czystość powierzchni przed powlekaniem.

Minimalna czystość powierzchni przed nałożeniem powłoki ochronnej

Minimalna czystość dla procesów powlekania jest zwykle określana zgodnie z normą J-STD 001D, która jest uważana za najczęściej stosowaną normę przemysłową do określania czystości elementów elektronicznych.

Do pełnej kwalifikacji zgodnie z J-STD 001D wymagane są następujące czynności:

- kwalifikacja wizualna przy powiększeniu 20× lub 40× (zgodnie z IPC A610D),

- kwalifikacja czystości używanej żywicy (poziom zanieczyszczeń <40 μg/cm2 dla pakietów klasy 3),

- pomiar zanieczyszczenia jonowego (dopuszczalny poziom jonów chlorku sodu <1,56 μg/cm²),

- kontrola obecności innych zanieczyszczeń organicznych,

- pomiar SIR po lub w trakcie przechowywania w warunkach klimatycznych.

Ocenę wizualną można przeprowadzić za pomocą makroskopu i po montażu nie powinno być żadnych widocznych zanieczyszczeń w postaci resztek żywicy na połączeniach lutowniczych, które wpływają na przyczepność powłoki lakierniczej i powodować jej złuszczanie. Próg dla pakietów klasy 3 wynosi tylko 40 μg/cm², co w praktyce odpowiada dopuszczeniu pozostałości żywicy tylko na jednym połączeniu lutowniczym. Jak dotąd takie pozostałości wykrywane były za pomocą drogich procedur, takich jak HPLC (wysokociśnieniowa chromatografia cieczowa), na szczęście teraz zanieczyszczenia tego typu można łatwo wykryć także za pomocą szybkich testów chemicznych, np. Zestron Resin Test. Umożliwia on łatwą identyfikację brudnych płytek, co pozwala ich dodatkowe wyczyszczenie z pozostałości żywicznych podczas produkcji bez przekroczenia maksymalnej wartości granicznej 40 μg/cm².

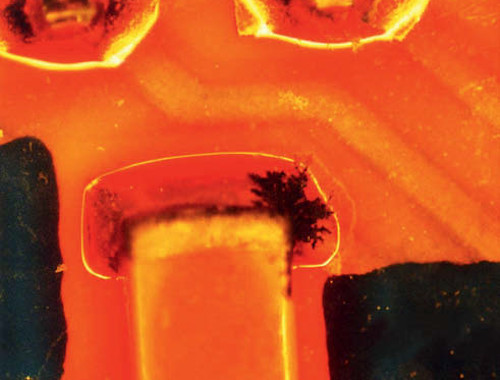

Drugim istotnym czynnikiem czystości powierzchni jest poziom ekwiwalentnych zanieczyszczeń jonowych. Duża wartość wskazuje na brud o własnościach higroskopijnych, którego pozostawienie prowadzi w ciągu kilku lat do rozwarstwienia się powłok ochronnych, a tym samym do zniszczenia ciągłości powierzchni (rys. 3).

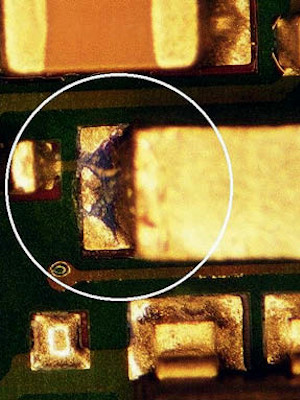

Ponadto inne zanieczyszczenia organiczne, takie jak pozostałości topnika, mogą również mieć wpływ na jakość powłoki i doprowadzić do awarii komponentów pod powłoką. Obecność takich zanieczyszczeń ocenia się zgodnie z J-STD 001D, ale warto wiedzieć, że istnieją szybkie i łatwe w użyciu metody detekcji przez odbarwianie (takie jak Zestron Flux Test), które mogą służyć jako alternatywa dla istniejących drogich metod badawczych, takich jak spektroskopia w podczerwieni. Za pomocą reakcji chemicznej wywołującej zmianę koloru na podzespole uwidacznia się obecność niezmytych kwasów organicznych używanych jako aktywatory w topnikach (rys. 4). Ponadto te szybkie testy pokazują rozmieszczenie zanieczyszczeń na powierzchni obwodu.

Do oceny można wykorzystać ponadto pomiar SIR, który służy do oceny jakości izolacji powierzchniowych. Pozostałości topnika i zanieczyszczenia przewodzą prąd i mogą powodować przepływ prądu upływowego, a tym samym mogą prowadzić do nieprawidłowego działania czułych obwodów. Podczas pomiaru SIR mozaika połączeń w kształcie grzebienia umieszczana jest w szafie klimatycznej i mierzona jest rezystancja między poszczególnymi strukturami grzebieniowymi. Pozwala to na określenie rezystancji powierzchni po lutowaniu podzespołów.

Przedstawione metody gwarantują wykrywanie różnych zanieczyszczeń na PCB. Niemniej jednak, aby obwody były czyste wg J-STD 001D, mycie jest często wymaganą operacją. Proces ten powinien nie tylko usuwać zanieczyszczenia, ale powinien również pozytywnie wpływać na przyczepność powłoki ochronnej, aby zminimalizować w dłuższej perspektywie ryzyko tworzenia się pęknięć i rozwarstwień.

Wybór odpowiedniej technologii mycia

Przy wyborze technologii mycia w pierwszej kolejności należy wziąć pod uwagę wymagania techniczne.

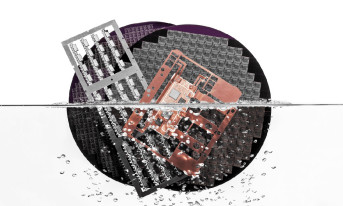

W przypadku, gdy kolejnym procesem jest powlekanie, mycie musi przede wszystkim zapewnić wysoką czystość powierzchni. W ten sposób zapewniona jest przyczepność lakieru. Mechaniczne metody aplikacji, takie jak natrysk w powietrzu, natrysk pod zanurzeniem lub ultradźwięki, powinny być dostosowane do wymagań związanych z usuwaniem pozostałości oraz budową i wrażliwością komponentów na narażenia mechaniczne.

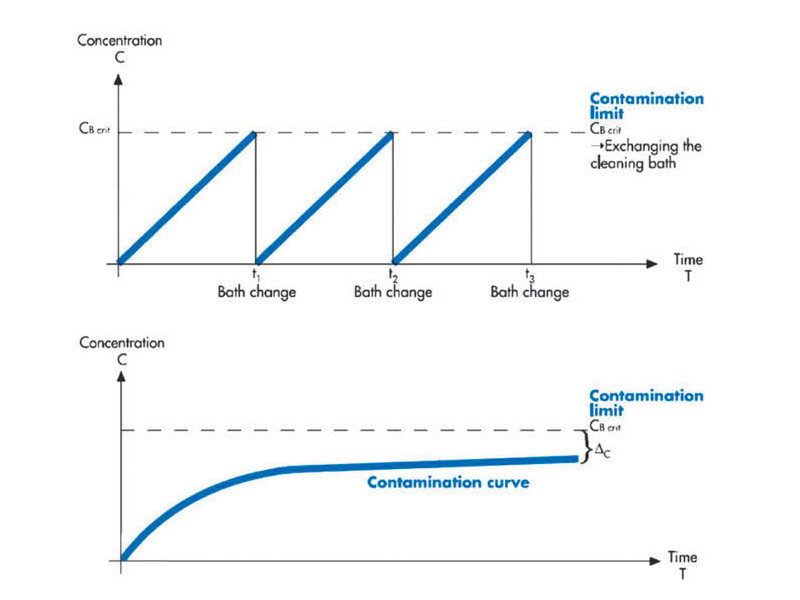

Istotną zaletą konwencjonalnych środków czyszczących zawierających środki powierzchniowo czynne jest to, że nie są one palne i ogólnie mają niską wartość VOC. Główne wady stosowania środków powierzchniowo czynnych do czyszczenia podzespołów elektronicznych wynikają z zasady ich działania. Aktywne elementy czyszczące konwencjonalnych środków powierzchniowo czynnych trwale wiążą się z zanieczyszczeniami. Z tego powodu następuje wyczerpanie składników aktywnych. Wynika z tego pojawiająca się z czasem nieskuteczność środka myjącego, której można przeciwdziałać jedynie, dodając więcej środka aktywnego do zbiornika lub całkowicie wymieniając preparat w zbiorniku myjącym. Skutkuje to zwiększonymi kosztami materiałów, robocizny, utylizacji i usuwania zużytego preparatu. Jednocześnie pozostałości środków myjących ściśle przylegają do powierzchni podłoża, co może prowadzić do problemów w kolejnych procesach, takich jak powlekanie.

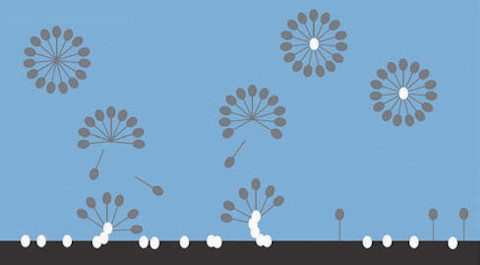

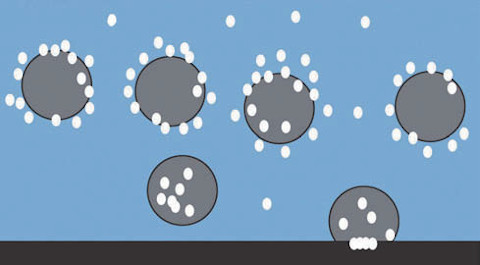

Cząstki mikrofazy usuwają pozostałości topnika, pozostałości żywicy i inne zanieczyszczenia z powierzchni podłoża. Aktywne składniki czyszczące nie wiążą się ściśle z zanieczyszczeniami jak tradycyjne środki powierzchniowo czynne (rys. 5). Cząsteczki brudu usuwane przez mikrofazy łączą się w grudki na krawędzi fazy i są uwalniane w filtrze (rys. 6). Dlatego w tym przypadku zanieczyszczenia można usunąć przez prostą filtrację. Co więcej, środki czyszczące typu MPC nie tracą składników aktywnych, tak jak wersje powierzchniowo czynne. Można ich używać dłużej, co skutkuje mniejszym zużyciem, a także niższymi kosztami wymiany zbiornika ze środkiem myjącym, utylizacji i transportu resztek (rys. 7). Dzięki MPC i formule bez środków powierzchniowo czynnych i ciał stałych, na powierzchni PCB nie ma żadnych pozostałości. Dzięki temu dalszy proces powlekania jest wysoce niezawodny.

Podsumowanie

Połączenie procesu mycia ze skutecznymi testami czystości powierzchni daje ekonomicznie opłacalne rozwiązanie procesów powlekania i znacznie zwiększa niezawodność procesu i niezawodność operacyjną powlekanych elementów. Takie prawidłowości potwierdza również organizacja GfKORR (Society for Corrosion Protection) w aktualnych wytycznych "Stosowanie i obróbka powłok ochronnych dla podzespołów elektronicznych". Zostały one przygotowane przez wiodących producentów powłok, pomagają w wyborze procesów zapewniających ekonomicznie opłacalne, a jednocześnie niezawodne rozwiązanie. Stosując zoptymalizowaną metodę mycia i dopuszczeń na etapie produkcji poprzedzającym proces powlekania, zapewnia się odpowiednią przyczepność powłok, zapobiegając w ten sposób awariom powlekanych elementów podczas działania w warunkach rzeczywistych. W obliczu tego złożonego problemu coraz ważniejsza staje się współpraca między inżynierami procesów produkcyjnych, dostawcami procesów mycia i producentami urządzeń.

Helmut Schweigart, Zestron Europe

Krzysztof Kołodziej, PB Technik

PB Technik sp. z o.o.

tel. 615 83 44

ul. Zwoleńska 27, 04-761 Warszawa

info@pbtechnik.com.pl