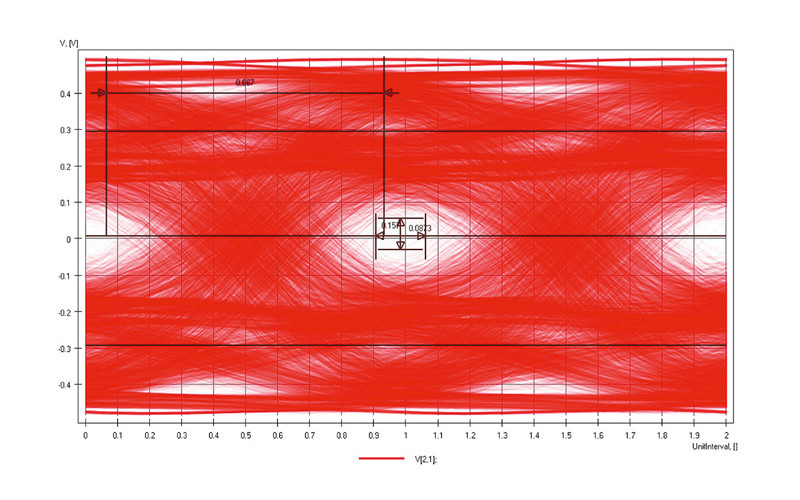

Dla projektantów tego typu systemów sprzętowych oczywiste stało się już jakiś czas temu, że sygnał cyfrowy nie jest już tak zupełnie cyfrowy. Sygnał cyfrowy o przepływności już nawet pojedynczych Gbps mierzy się z problemami strat, szumów amplitudowych i fazowych, przez co właściwie rozpatruje się go jak specjalny sygnał analogowy z całą paletą nowych starych problemów.

Obok przepływności strumienia danych kluczowym elementem toru sygnałowego jest niezawodność transmisji. Kwantytatywnym wskaźnikiem niezawodności jest bitowa stopa błędów BER (Bit Error Rate), którą dla systemów telekomunikacyjnych oczekuje się nawet poniżej 10–18. Zapewnienie tak wysokich wymagań niezawodnościowych przy interfejsach pracujących z szybkościami 25–33 Gbps (NRZ) / 112 Gbps (PAM4) to elektronika w trudniejszym wydaniu.

Straty

Kluczowym problemem w projektowaniu interfejsów wielogigabitowych są straty toru sygnałowego, będące źródłem zniekształceń przenoszonego sygnału. Tor sygnałowy o dużej przepływności (dla ustalenia uwagi przyjmijmy >10 Gbps) należy rozpatrywać w bardzo szerokim paśmie, rozciągającym się od 0 do kilkudziesięciu GHz. Symulacje, diagnostyka i pomiary w tak szerokim paśmie częstotliwości są nie lada wyzwaniem, stanowiąc wyróżnik wśród aplikacji RF, choć obie dziedziny korzystają z tego samego słownika pojęć, m.in. jak: impedancja falowa, szybkość propagacji, macierz rozproszenia itd.

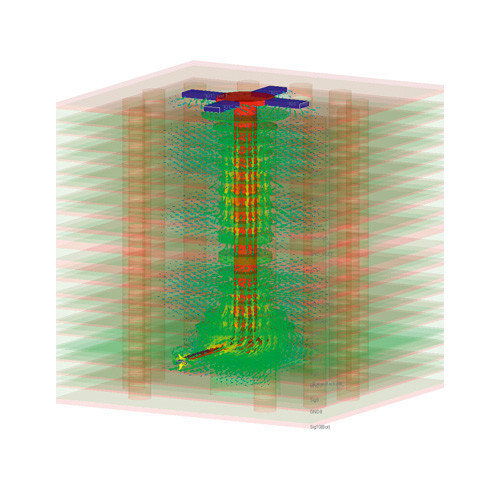

Wyróżnia się pięć źródeł strat w torach sygnałowych: (1) straty na promieniowanie EM, (2) straty wynikające ze sprzężeń (przesłuchy), (3) straty przewodzenia, (4) straty w dielektryku i (5) straty wynikające z niedopasowania falowego na drodze propagacji sygnału. Poprzez zasadniczo proste zabiegi projektowe można zminimalizować straty (1) i (2) – np. odpowiednio ekranując czy separując tory sygnałowe. Za to straty (3) i (4) zależne są od częstotliwości, co sprawia, że propagacja sygnału odbywa się w środowisku dyspersyjnym, a to z kolei jest podstawowym źródłem szumu fazowego sygnałów cyfrowych. W tym miejscu należy wspomnieć o roli, jaką odgrywa sieć zasilająca systemu (PDN – Power Distribution Network). Źle zaprojektowana sieć zasilająca może stanowić istotne źródło szumu fazowego na skutek przenikania szumów zasilania do źródeł taktujących oraz nawet rezonansowe wzmocnienia szumów. Z tego powodu prawie zawsze obok integralności sygnałowej pojawiają się problemy integralności mocy. Na integralność mocy składa się nie tylko przewidywanie obciążalności systemu zasilania (DC), ale także analityka modeli impedancji szerokopasmowych PDN (AC) – lecz to temat na zupełnie inny artykuł.

Straty (3)–(5) są poważnym wyzwaniem w praktyce inżynierskiej, gdyż dużo trudniej je dokładnie przewidywać, zaś ich poprawna diagnostyka wymaga odpowiedniego warsztatu, tj. narzędzi symulacyjnych, CAD/EDA oraz zaplecza pomiarowego.

Strat toru sygnałowego nie da się wyeliminować, można nimi co najwyżej odpowiednio zarządzać. Budżetowanie strat toru sygnałowego jest więc jednym z kluczowych wyzwań projektowych inżyniera integralności sygnałowej.

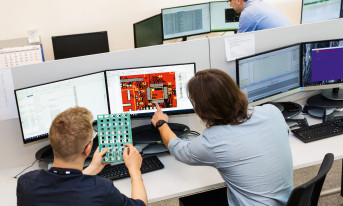

Symulacja i pomiary

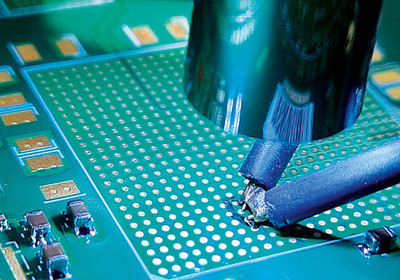

W projekcie zawierającym interfejsy wielogigabitowe niezbędna jest właściwa interakcja między zespołem inżynierskim a technologami PCB już na etapie konstrukcji stosu PCB. Oprócz doboru materiałów dielektrycznych, gdzie poszukujemy szybkich dielektryków o możliwie stałych częstotliwościowo Dk i Df, istotny jest także dobór folii miedzianej z uwagi na istotny w interesującym paśmie efekt naskórkowości. W praktyce dane katalogowe użytych materiałów nie wystarczają. Dla częstotliwości powyżej 8–10 GHz mogą uwidaczniać się rozmaite efekty, np. wpływ niejednorodności stałej dielektrycznej wokół linii sygnałowej czy różnice między oczekiwanym a rzeczywistym modelem chropowatości folii miedzianej. Dla uzyskania poprawnych wyników symulacji EM niezbędna jest więc wiedza o rzeczywistych szerokopasmowych modelach Dk, Df (strat w dielektryku) i stratach przewodzenia. W procesie projektowym planuje się więc etap prewalidacji, polegający na wyznaczeniu rzeczywistych strat danej konstrukcji stosu PCB. Modele symulacyjne materiałów powstają w wyniku adaptacji do danych pomiarowych zebranych ze specjalnie zaprojektowanego kuponu, dzięki czemu symulacje EM torów sygnałowych mają szansę odzwierciedlać rzeczywistość w paśmie nawet kilkudziesięciu GHz.

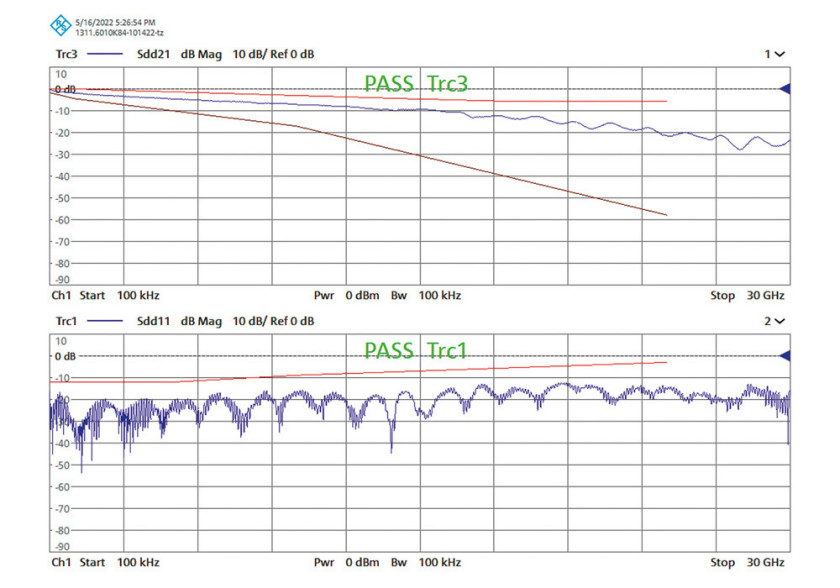

Jak łatwo się domyślić, w prawidłowym wyznaczania modeli strat kluczową rolę odgrywa dokładność pomiaru. Na szczęście z pomocą przychodzi tutaj standard IEEE370 systematyzujący metodologię, wprowadzający m.in. odpowiednie narzędzia do oceny spójności uzyskanych danych pomiarowych. Posługując się tym opracowaniem, można zweryfikować wiarygodność informacji, na podstawie których podejmowane są późniejsze decyzje inżynierskie w projekcie. Dalej, przy użyciu wyznaczonych modeli, można prowadzić symulacje pre- i post-layout i doprowadzić projekt do fazy prototypowania przy znacznie zmniejszonym ryzyku niepowodzenia. Ostatnim etapem jest finalna weryfikacja strat toru sygnałowego na drodze pomiaru macierzy rozproszenia bezpośrednio w zaprojektowanym obwodzie PCB. Na tej podstawie można dokonać weryfikacji prawidłowości budżetowania strat wtrąceniowych i odbiciowych dla danego toru sygnałowego i w sposób świadomy podejmować decyzje projektowe.

Podsumowanie

Właściwe zaadresowanie problemów integralności sygnałowej pozwala na uzyskanie oczekiwanej niezawodności transmisji sygnału przy minimalnej liczbie iteracji projektowych. Projektowanie systemów transmisji danych o prędkościach rzędu 25 Gbps wymaga odpowiedniego warsztatu, na który składa się tandem narzędzi symulacyjnych i pomiarowych. FastLogic w ramach współpracy krótkoi długoterminowej oferuje usługi B+R i projektowe z obszaru zagadnień integralności sygnałowej (SI) i integralności mocy (PI) dla wymagających systemów FPGA, SoC, CPU, DDRx, DSP, ASIC, itp. FastLogic ma certyfikaty ISO9001, ISO27001 oraz AQAP2110.

dr inż. Kamil Grabowski, FastLogic

FastLogic Sp. z o.o.

tel. 42 207 40 96

www.fastlogic.pl

office@fastlogic.pl