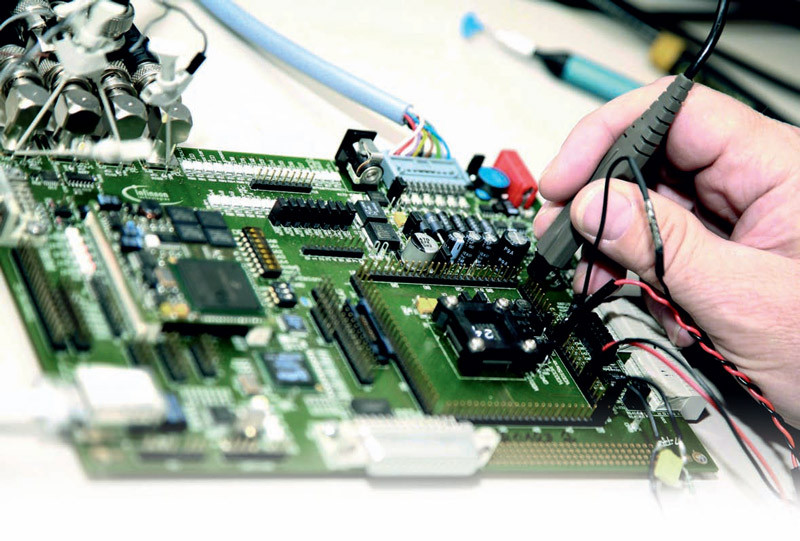

Jeżeli powyższych warunków nie uda się spełnić, należy liczyć się z różnymi problemami, na przykład gdy w danym urządzeniu układ cyfrowy o niższym poziomie napięć ma sterować układem zasilanym wyższym napięciem.

Jeżeli różnica napięć poziomów logicznych obu układów będzie zbyt duża, takie połączenie może nie funkcjonować prawidłowo. By takim sytuacjom zapobiegać, wykorzystuje się różne sposoby dopasowania niekompatybilnych napięć. W artykule zaprezentujemy najpopularniejsze rozwiązania oraz przykłady ich wdrożenia w konkretnych aplikacjach.

Translatory napięć

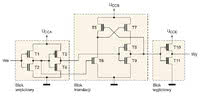

Jedną z możliwości jest zastosowanie dodatkowego układu pośredniczącego, tzw. translatora napięć. Przykładem są translatory zasilane dwoma napięciami, które umożliwiają jednokierunkową lub dwukierunkową konwersję napięć poziomów logicznych. Układ tego typu w wersji z jednokierunkową translacją przedstawiono na rysunku 2. Napięcia poziomów logicznych odnoszone do napięcia UCCA są w nim podnoszone do napięć poziomów logicznych zależnych od napięcia UCCB.

Działanie translatora jest następujące: jeżeli na wejściu pojawia się napięcie odpowiadające stanowi wysokiemu, tranzystor T9 załącza się i napięcie wyjściowe wzrasta do UCCB przez tranzystor T10. Jeżeli z kolei na wejściu występuje stan niski, przewodzą tranzystory T6, T7 oraz T8, a poziom napięcia na wyjściu obniża się przez tranzystor T11. Zaletą tej konfiguracji jest to, że nie występuje stała droga prądu między UCCA lub UCCB a masą, dzięki czemu układ ten charakteryzuje niski pobór prądu spoczynkowego.

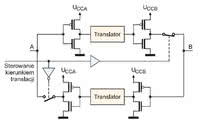

Do realizacji translatora dwukierunkowego wymagane jest stworzenie ścieżki powrotnej od strony układu zasilanego napięciem UCCB do układu zasilanego napięciem UCCA. Na rysunku 3 przedstawiono przykład realizacji takiego translatora. Kierunkiem translacji można w nim sterować za pośrednictwem sygnału kontrolnego.

Translatory z kluczami FET

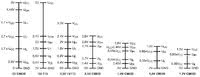

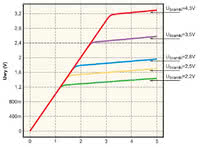

Jako translator napięć poziomów logicznych wykorzystać można również klucz w postaci tranzystora FET. Wynika to z charakterystyki komponentów tego typu, której przykład dla tranzystora polowego o napięciu progowym o wartości około 1V przestawiono na rysunku 4. Z wykresu wynika, że napięcie wyjściowe tranzystora zostaje ograniczone do wartości odpowiadającej różnicy napięcia bramki i napięcia progowego.

Stąd by uzyskać napięcia przyjęte za wartość odniesienia w popularnych rodzinach układów cyfrowych, np. 3,3V, 2,5V, 1,8V 1,5V raz 1,2V, napięcie bramki wynosić powinno odpowiednio 4,3V, 3,5V, 2,8V, 2,5V oraz 2,2V. Ta właściwość umożliwia wykorzystanie tranzystorów w translacji napięć "w dół".

Dwukierunkowy translator FET

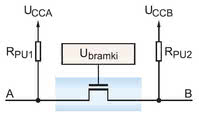

W opisany sposób zrealizować można jednak wyłącznie translację jednokierunkową. By zbudować translator dwukierunkowy, należy zastosować układ w konfiguracji jak na rysunku 5, w którym oprócz tranzystora polowego wykorzystano dwa rezystory podciągające. Bramka tego tranzystora jest zazwyczaj połączona ze źródłem niższego napięcia spośród UCCA i UCCB.

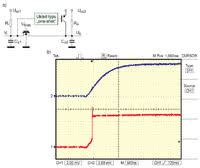

Zaletą tego rozwiązania jest to, że kierunek translacji napięć jest ustalany automatycznie i nie jest wymagany żaden dodatkowy sygnał sterujący. Pracę translatora z rysunku 5 można usprawnić, uzupełniając go o układ typu "one-shot" (rys. 6a), który omijając rezystor podciągający, załącza się, przyspieszając w ten sposób przejście ze stanu niskiego w stan wysoki.

Na rysunku 6b można zaobserwować znaczne skrócenie czasu narastania sygnału dzięki zastosowaniu takiego rozwiązania. Układ "one-shot" może się załączać, gdy napięcie wejściowe wzrasta powyżej pewnego napięcia progowego i wyłączać po pewnym czasie samoczynnie lub w reakcji na przekroczenie określonego progu napięcia wyjściowego.

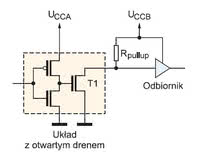

Translatory z otwartym drenem

Do konwersji napięć poziomów logicznych można też wykorzystać układy z wyjściem typu otwarty dren. Przykład takiego układu, w którym między zaciskiem wyjściowym a masą znajduje się tranzystor T1, zamieszczono na rysunku 7. Napięcie wyjściowe w takiej konfiguracji zależy od wartości napięcia zasilającego UCCB.

Typ translatora można zmieniać przez odpowiedni dobór tego napięcia. Na przykład jeżeli UCCB jest większe niż wejściowe napięcie odpowiadające stanowi wysokiemu, uzyskujemy translację "w górę", jeżeli natomiast UCCB jest mniejsze - translację "w dół". Rozwiązanie to nie jest pozbawione wad. Na przykład kiedy wyjście bloku translatora jest w stanie niskim, czyli gdy tranzystor T1 jest załączony między zaciskiem UCCB a masą układu, istnieje stała ścieżka prądu płynącego przez rezystor podciagający Rpullup i tranzystor T1.

Z tego powodu układ charakteryzuje zwiększony pobór mocy. Natężenie prądu można wprawdzie ograniczyć, wykorzystując rezystor podciągający o większej rezystancji, ale jednocześnie wydłuża się wówczas czas narastania sygnału wyjściowego, a tym samym maleje szybkość działania całego translatora. Przyczyną jest duża stała czasowa układu RC tworzonego przez rezystor Rpullup oraz pojemność obciążenia.

Urządzenia z tolerancją na przepięcia

Jako element pośredniczący między urządzeniami o niekompatybilnych poziomach napięć można też wykorzystać układ, który charakteryzuje się zwiększoną odpornością na napięcia wejściowe wyższe od napięcia zasilającego. Takie właściwości uzyskuje się, zwiększając grubość bramki tranzystorów oraz blokując pasożytnicze ścieżki prądu między wejściem a zaciskiem napięcia zasilania.

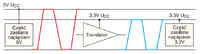

Przykład takiego rozwiązania przedstawia rysunek 8. Wykorzystano tu translator poziomów napięć z 5V na 3,3V. Przełączenie tego elementu następuje, gdy napięcie wejściowe zmieniające się od 0 do 5V przekroczy próg 3,3V. Niestety problemem w takim wypadku są różnice w czasie przejścia ze stanu niskiego do wysokiego, a przejściem odwrotnym.

W niektórych aplikacjach uniemożliwia to zastosowanie takiego rozwiązania. W kolejnych akapitach zostanie pokazane, gdzie w praktyce wykorzystuje się translację napięć na przykładzie magistrali I²C oraz translatorów napięć firmy Analog Devices, które zostaną przedstawione w przykładowych aplikacjach.

Przykład 1 - translacja poziomów napięć w magistrali I²C

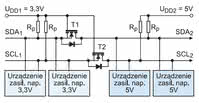

Na rysunku 9 przedstawiono przykład magistrali I²C, za pośrednictwem której komunikują się urządzenia zasilane różnymi napięciami. W związku z tym w obrębie magistrali wyróżnić można sekcję "wyższych napięć", którą stanowią urządzenia zasilane napięciem 5V oraz sekcję "niższych napięć", w obrębie której podłączone są urządzenia zasilane napięciem 3,3V.

By transmisja była możliwa, zastosowano dwukierunkowy translator napięć. Stanowią go tranzystory MOSFET, po jednym dla każdej linii magistrali, tzn. odpowiednio TR1 dla linii danych SDA i TR2 dla linii zegara SCL. Bramki tranzystorów są połączone z niższym napięcie zasilającym UDD1, źródła z liniami magistrali w sekcji "niższego napięcia", natomiast dreny z liniami magistrali w części "wyższego napięcia".

W pracy tak skonfigurowanej magistrali można wyróżnić trzy stany. Gdy żadne z urządzeń nie nadaje, linie magistrali w części "niższych napięć" są przez rezystory podciągające podłączone do napięcia 3,3V. W związku z tym tranzystory TR1 i TR2 nie przewodzą, dzięki czemu linie magistrali w sekcji "wyższych napięć" są przez rezystory podciągające podłączone do napięcia 5V.

Linie magistrali obu sekcji pozostają zatem w stanie wysokim, przy czym w każdej z nich wysokiemu poziomowi logicznemu odpowiada inna wartość napięcia. Gdy któreś z urządzeń zasilanych napięciem 3,3V zacznie nadawać, na liniach magistrali (i na zaciskach źródeł TR1 i TR2) pojawia się sygnał w stanie niskim. Wówczas tranzystory TR1 i TR2 zaczynają przewodzić, a za ich pośrednictwem również linie magistrali w części "wyższego napięcia" przechodzą w stan niski.

Ostatecznie na liniach magistrali w obu sekcjach wystąpi takie samo napięcie odpowiadające niskiemu poziomowi logicznemu układów zasilanych ze źródła napięcia 3,3V. Analogicznie będzie w przypadku, gdy nadawanie rozpocznie któreś z urządzeń zasilanych napięciem 5V.

Przykład 2 - translator ADG3123

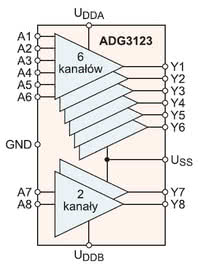

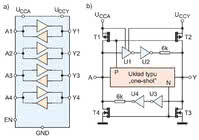

Na rysunku 10 przedstawiono uproszczony schemat funkcjonalny układu ADG3123. Jest to 8-kanałowy translator poziomów logicznych układów CMOS podawanych na wejścia A1- A8 do wyższych napięć, które dostępne są na zaciskach Y1-Y8. ADG3123 jest zasilany ze źródeł napięcia doprowadzonych do zacisków UDDB i USS. Wartości tych napięć ustalają napięcie logicznego poziomu niskiego dla wszystkich wyjść oraz poziomu wysokiego dla wyjść Y7 i Y8.

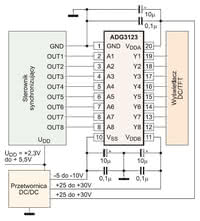

Napięcie logicznego poziomu wysokiego dla pozostałych wyjść (Y1-Y6) zależy natomiast od wartości napięcia na zacisku UDDA. By translator funkcjonował poprawnie, napięcie UDDB powinno być równe lub większe od napięcia UDDA, z kolei napięcie między zaciskiem UDDB i pinem USS nie powinno przekroczyć 35V. Omawiany translator wykorzystać można na przykład w układach sterujących wyświetlaczami LCD TFT.

Często sygnały synchronizujące proces skanowania pikseli są do paneli przekazywane za pośrednictwem niskonapięciowych układów CMOS, podczas gdy większość wyświetlaczy pracuje przy wyższych napięciach. Stąd wymagana jest translacja poziomu sygnałów synchronizujących do wartości umożliwiających wysterowanie wyświetlacza. Przykład takiego rozwiązania przedstawia rysunek 11, na którym układ ADG3123 podwyższa napięcia ośmiu sygnałów sterujących.

Przykład 3 - translator ADG3304

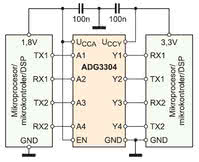

Rys. 13. ADG3304 pośredniczy w transmisji między dwoma procesorami zasilanymi różnymi napięciami, które komunikują się w trybie full-dupleks

Na rysunku 12 przedstawiono schemat funkcjonalny (a) oraz uproszczony schemat struktury wewnętrznej (b) czterokanałowego dwukierunkowego translatora napięć ADG3304. Translator jest zasilany z dwóch źródeł napięcia podłączanych do zacisków UCCA i UCCY (UCCA powinno być równe lub mniejsze od UCCY), względem których ustalane są napięcia poziomów logicznych na zaciskach odpowiednio A1-A4 oraz Y1-Y4.

W zależności od tego, na które porty doprowadzane są sygnały wejściowe, następuje translacja napięć w kierunku A->Y lub w odwrotnym. W pierwszym przypadku wykorzystywane są bloki U1 oraz U2, natomiast w translacji w kierunku Y->A udział biorą bloki U3 oraz U4. Translator nie wymaga dodatkowego sygnału kontrolnego określającego kierunek translacji.

Częścią ADG3304 jest też układ typu "oneshot", który wykrywa narastające lub opadające zbocza sygnałów wejściowych poszczególnych kanałów, załączając odpowiednio tranzystor PMOS: T1 lub T2 albo jeden z tranzystorów NMOS: T3 lub T4. W ten sposób przyspieszane jest ładowanie lub rozładowywanie pojemności obciążeń pojemnościowych, co skraca czas przejście między poziomami logicznymi.

W opisywanym układzie możliwa jest też jednoczesna translacja napięć w obu kierunkach, tzn. dopuszczalna jest sytuacja, w której na przykład w dwóch kanałach zachodzi konwersja napięć w kierunku A->Y, natomiast w pozostałych w kierunku odwrotnym. Przykład zastosowania tej funkcji translatora przedstawiono na rysunku 13. ADG3304 jest tu wykorzystywany jako układ pośredniczący w komunikacji między dwoma procesorami zasilanymi różnymi napięciami (1,8V i 3,3V), które pracując w trybie full-dupleks transmitują dane przez zaciski TX1/RX1 i TX2/RX2.

Monika Jaworowska